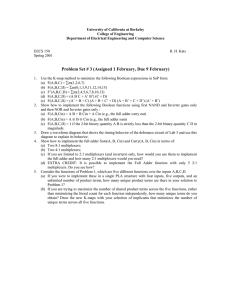

Binary full adder 2-bit ripple

advertisement

CSE 370 Spring 2006 Introduction to Digital Design Lecture 12: Adders Last Lecture PLAs and PALs Binary full adder 1-bit full adder Computes sum, carry-out Carry-in allows cascaded adders Sum = Cin xor A xor B Cout = ACin + BCin + AB A 0 0 0 0 1 1 1 1 XOR A B XOR 32 Cin 0 1 0 1 0 1 0 1 S 0 1 1 0 1 0 0 1 Cout 0 0 0 1 0 1 1 1 Sum Cin Today Adders B 0 0 1 1 0 0 1 1 33 AND2 B Cin A B Cin 11 A Cin AND2 OR3 12 14 Cout Sum Cout Full Adder AND2 A B 13 Full adder: Alternative Implementation Multilevel logic Slower Less gates 2 XORs, 2 ANDs, 1 OR Sum = (A ⊕ B) ⊕ Cin Cout = ACin + BCin + AB = (A ⊕ B)Cin + AB A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 Cin 0 1 0 1 0 1 0 1 S 0 1 1 0 1 0 0 1 Cout 0 0 0 1 0 1 1 1 Cout 0 0 0 1 0 1 1 1 2-bit ripple-carry adder A Half Adder B Cin Sum Cout A xor B AB Half Adder Sum Cout A xor B xor Cin A1 B1 A2 B2 Cin Cout Cin Cout Sum1 Sum2 1-Bit Adder XOR A B 32 XOR Sum Cin 0 33 AND2 Cin B Cin A Cin A B Cout 11 AND2 OR3 12 14 Cout AND2 Sum A B 13 (A xor B)Cin Cout Overflow Sum 4-bit ripple-carry adder/subtractor Circuit adds or subtracts 2s complement: A – B = A + (–B) = A + B' + 1 Problem: Ripple-carry delay Carry propagation limits adder speed Cin XOR A3 B3B3' 0 1 A2 B2B2' Sel A1 B1B1' 0 1 Sel @0 A @0 B A0 B0B0' 0 1 Sel 32 @2N Cin 0 1 Sel XOR 33 Sum @2N+1 @0 A B A B B A B A Cout Cin Cout Cin Cout Cin Cout Cin Sum Sum Sum Sum 0 Ð Add 1 Ð Subtract A @2N Cin S1 @3 C2 @4 A1 B1 AND2 B @2N Cin S0 @2 C1 @2 A0 B0 11 AND2 OR3 12 14 @0 @2N+2 Cout S2 @5 C3 @6 A2 B2 AND2 S3 S2 S1 S0 Note: Can replace 2:1 muxes with XOR gates Overflow Ripple-carry adder timing diagram Critical delay Carry propagation 1111 + 0001 = 10000 is worst case S0, C1 Valid T0 T2 S1, C2 Valid T4 S2, C3 Valid T6 S3, C4 Valid T8 @0 A @0 B 13 A3 B3 Cout takes two gate delays Cin arrives late S3 @7 Cout @8 One solution: Carry lookahead logic Compute all the carries in parallel Derive carries from the data inputs Not from intermediate carries Use two-level logic Compute all sums in parallel Cascade simple adders to make large adders Speed improvement 16-bit ripple-carry: ~32 gate delays 16-bit carry-lookahead: ~8 gate delays Issues Complex combinational logic Cin A0 B0 S0 @2 C1 @3 A1 B1 S1 @4 C2 @3 A2 B2 S2 @4 C3 @3 A3 B3 S3 @4 C4 @3 C4 @3 Carry-lookahead logic Full adder again Half Adder A Sum B Cout Half Adder A xor B Sum AB Cout A xor B xor Cin Cin Cout XOR Ai Bi XOR Pi 36 Si Si = Ai xor Bi xor Ci = Pi xor Ci 38 AND2 Ai Bi Sum Cin(A xor B) Carry generate: Gi = AiBi Generate carry when A = B = 1 Carry propagate: Pi = Ai xor Bi Propagate carry-in to carry-out when (A xor B) = 1 Sum and Cout in terms of generate/propagate: AND2 Gi 37 39 Ci+1= AiBi + Ci(Ai xor Bi) = Gi + CiPi OR2 Ci Ci+1 40 Implementing the carrylookahead logic Carry-lookahead logic (cont’d) Re-express the carry logic in terms of G and P C1 = G0 + P0C0 C2 = G1 + P1C1 = G1 + P1G0 + P1P0C0 C3 = G2 + P2C2 = G2 + P2G1 + P2P1G0 + P2P1P0C0 C4 = G3 + P3C3 = G3 + P3G2 + P3P2G1 + P3P2P1G0 + P3P2P1P0C0 Implement each carry equation with two-level logic Derive intermediate results directly from inputs Rather than from carries Allows "sum" computations to proceed in parallel Ai Bi Logic complexity increases with adder size Pi @ 1 gate delay Si @ 2 gate delays Ci Gi @ 1 gate delay C0 P0 G0 C0 P0 P1 G0 P1 G1 C1 C2 C0 P0 P1 P2 G0 P1 P2 G1 P2 G2 C3 C0 P0 P1 P2 P3 G0 P1 P2 P3 G1 P2 P3 G2 P3 G3 C4 Another solution: Carry-select adder Cascaded carry-lookahead adder Redundant hardware speeds carry calculation Compute two high-order sums while waiting for carryin (C4) Select correct high-order sum after receiving C4 4 four-bit adders with internal carry lookahead Second level lookahead extends adder to 16 bits 4 4 A[15-12] B[15-12] A[11-8] C12 4-bit Adder P G C4 A[7-4] C8 G @2 S[11-8] @8 @3 @5 G3 C3 B[7-4] P A[3-0] C4 S[7-4] @7 @3 G P G2 C2 C0 @0 G C8 4 @2 S[3-0] @4 @3 @5 P2 B[3-0] 4-bit Adder 4 @2 4 4 4-bit Adder 4 P3 C16 @4 B[11-8] P 4 4 4-bit Adder 4 S[15-12] @8 4 4 @2 @3 P0 G0 C8 @4 P1 G1 C1 C0 Lookahead Carry Unit P3-0 @3 C0 @0 G3-0 @5 1 0 1 0 five 2:1 muxes C8 We've finished combinational logic... What you should know Twos complement arithmetic Truth tables Basic logic gates Schematic diagrams Timing diagrams Minterm and maxterm expansions (canonical, minimized) de Morgan's theorem AND/OR to NAND/NOR logic conversion K-maps, logic minimization, don't cares Multiplexers/demultiplexers PLAs/PALs ROMs Adders S7 4-bit adder [7:4] 0 4-bit adder [7:4] 1 10 C4 S6 1 0 1 0 S5 adder low adder high C0 4-Bit Adder [3:0] S4 S3 S2 S1 S0 Sequential versus combinational A C B clock Apply fixed inputs A, B Wait for clock edge Observe C Wait for another clock edge Observe C again Combinational: C will stay the same Sequential: C may be different Sequential logic Two types Synchronous = clocked Asynchronous = self-timed Has state State = memory Employs feedback Assumes steady-state signals Signals are valid after they have settled State elements hold their settled output values Sequential versus combinational (again) Combinational systems are memoryless Outputs depend only on the present inputs Inputs Outputs System Sequential systems have memory Outputs depend on the present and the previous inputs Inputs Outputs System Feedback Synchronous sequential systems Memory holds a system’s state Changes in state occur at specific times A periodic signal times or clocks the state changes The clock period is the time between state changes A clock clock Outputs retain their settled values The clock period must be long enough for all voltages to settle to a steady state before the next state change A C B pulsewidth Steady-state abstraction State changes occur at rising edge of clock duty cycle = pulsewidth/period (here it is 50%) clock clock C period C B Settled value Clock hides transient behavior Example: A sequential system Door combination lock Enter 3 numbers in sequence and the door opens If there is an error the lock must be reset After the door opens the lock must be reset Inputs: Sequence of numbers, reset Outputs: Door open/close Memory: Must remember the combination