Level Translation with Termination Methods

advertisement

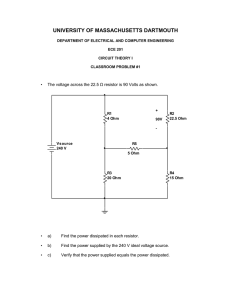

FastEdge™ Series Level Translation with Termination Methods Interconnection between Logic Families Termination at the Receiver pins This document will cover the I/O families based on PECL (LVPECL), LVDS, HSTL and LVTTL uses. There are dozens of other level classes and even sub classes in these. Areas of discussion include the PECL output and input translations and the HSTL input translations to and from these logic levels. The first is PECL. Zo = 50 ohm 51 Zo = 50 ohm PECL Outputs 51 VTT (1.3V) Typical 3.3V PECL, LVPECL Output • General comments on the “spec” into PECL , LVPECL input • Positive Emitter Coupled Logic • Differential Mode b. PECL to LVDS • Power 3.3V, 2.5V • Usage backplane, transmission lines noisy and higher voltage needs The Offset values and termination voltages of LVDS require the user to both divide and re-terminate the voltages. The LVDS input has 100 ohms across it - GND is centered. The voltage is based on the resistor ladder 3.3V * 51/(120+22+51) or 0.825 V. • Noise Immunity ; 140 mV LVDS Spec Levels • Owner None - Without a standard. • VID(diff) min = The Spec levels • VIX(diff) max = • VOD(diff) min = 375 mV • VIX(diff) min = • VOX(diff) max =1.42V 100mV 500mV 2.350 V This DC bias level lies within the VIX limits. • VOX(diff) min = 1.125V • VIX(diff)max = 500 mV The load for the PECL is based on the parallel combinations of the three resistors. 51+33 in parallel to 120. This is approxamately 50 ohms. (84*120)/(84+120)= 49.4 • VIX(diff) min =2.350V Now for the waveform calculations. • VID(diff)min =100 mV VIDlvds = VODpecl *(51/(33+51)) = 228mv LVDS VID(min) input(min) spec = 100mv. Sample interconnections 1. Pecl output to: a. PECL to PECL 3.3V PECL or LVPECL (the 3.3V and 2.5V versions) use two termination voltages based solely on the voltage level of VCC. The value is typically VCC-2.0V yielding 1.3V or 0.5V. The later voltage intended for the 2.5V use has typically been grounded. Since the inputs have wide latitude, (2.35V down to 0.5V), variations in supply and loading occur. The example uses standard EIA resistor values which are 2% higher than standard 50 ohm definitions. Application defines specs and cost allowances. The resistors to VTT are at the far end of the transmission line, in all cases next to the input of the next device. If transversing a backplane higher impedance resistors, 330 ohms as an example, have been used on the near end when a cable or P.C.B. is pulled during use. Cypress Semiconductor Corporation • 3901 North First Street 120 PECL 120 50 ohm 50 ohm • 33 33 51 51 San Jose, CA 95134 • LVDS INPUT 408-943-2600 June 26,2003 [+] Feedback Level Translation and Termination Methods c. PECL to HSTL All resistors on both boards should be close to their respective device. The I/O class called HSTL, High Speed Transceiver Logic, is defined for both Single and Differential I/o lines. The output bus voltage is defined to be at 1.5V while the core voltage can be any value. This was defined before semiconductor logic could be run at 1.5V and started in the 5V days. The owner of this spec is JEDEC, actually “Solid State Technolog Association” . The spec number at JEDEC is JESD8-6. Rz, the termination resistors, are actually considered part of the LVPECL driver itself. Since they are on the far end of a cable system, the driver must have balancing 330-ohm resistors to complete the output driver and allow it to function when the cable or far end PCB is unplugged. The 'lower end' of the driver is in the form of Rz since it is an open emitter design. The Spec levels are HSTL Spec Levels : Notice how the count of Rz is doubled? Rz is the impedance of the PCB. The total value between the two lines is 2 X Rz, between each line and virtual ground is Rz. • VIH(ac) min = 0.95 • VIL(ac) max = 0.55 In the specific case of 62 ohm trace impedance, the value of Rz = 56 ohm (each) with Rs being a 12 ohm chip resistor. VTT is typically VDD-2V. RS = 62 - 50 = 12 ohm. Measuring points Theory says 62 ohm resistor, standard chip resistors are 56 or 68. Use 62 ohm if available. Backplane cable connections Theory says 12 ohm and it is available and standard value. 4pf 0.1uf 330 ohm 100 ohm In most cases, the smaller value of Rs are desirable for use in series matching. This resistor will discharge a cable when it is plugged on. Floating cables have a stored charge and possible high-energy component that should have a passive shunting device prior to the driver. 4pf 33 18 1.25V The 100 ohm termination resistor may not be present in all devices. This applcation required an HSTL clock and only an LVPECL device was available. The LVPECL device drove a backplane cable to several sites - this is one. The 330 ohm resistors on the near side were discussed earlier on the PECL to PECL. The calculations are much like LVDS. Circuit Design concept for use of LVPECL on P.C.B.s other than 50 ohm and use of cables. LVPECL: • VOD(diff) min = 375 mV LVPECL output • VOX(diff) max =1.42V Backplanes Rs • VOX(diff) min = 1.125V Rz 330 RL = 33+18 = 51 ohm critically it is 51||330 thus Rz 330 RLc= 51*330/(51+330) = 44 ohms. The critical load is close to 10% over the standard 50 ohm value due to the 330 ohm that stabilizes the driver when and if a cable on the backplane is pulled or in a routed backplane, the loading PCB is pulled. Naturally, if this isn’t on a backplane, the 330’s should be kept perhaps increased to lessen the loading effects, but the part is needed for a passive termination for VT. VTT LVPECL input Rs Cable Electrically speaking, VOD will be also diminished through the use of series resistors. The output level will be VOD(rec) = VOD(drive) * Rz/ (Rs+Rz). It can be seen that when RS << Rz the effect is nominal in magnitude change. VT = 1.25(330+33)/(330+33+18) = 1.19v which is above LVPECL’s VOX min and below the VOXmax. d. Termination with non-50 ohm transmission lines Regarding stored energy in a transmission line, consider the high quality, low loss lines that have extremely low leakages. The capacitance per foot will charge to a DC level and maintain it, and can accumulate charge on the bench. It is proper practice to ‘unload’ a cable by shorting both lines together prior to use. Back planes and cable present challenges in maintaining impedance and quality signals. LVPECL outputs are 50 ohm in nature. The values of Rs in the next figure are used to match the driver impedance to that of the PCB trace. 2 [+] Feedback Level Translation and Termination Methods PECL inputs minimum of LVDS is more than 2 x that of the minimum input of LVPECL. A listing of the LVDS outptut spec. is below. • General comments on the “spec” • Positive Emitter Coupled Logic • VOD(diff) min = • Differential Mode • Power 3.3V, 2.5V • Owner None - Without a standard. 247 mV • VOX(diff) max = 1.375 V • VOX(diff) min = 1.125 V Notice how this spec falls into that of LVPECL. VOX lies within the region of VIX - the high value is 1 volt below LVPECL max input crossing. • Usage backplane, transmission lines noisy and higher voltage needs • Noise Immunity ; 140 mV Two connection examples will be provided. One point ot point, and another is a specific need for DC isolation transmission. The Spec levels • VID(diff)min =100 mV • VIX(diff)max = 500 mV • VIX(diff) min =2.350V Zo = 50 ohm Before we start on the input section let us evaluate the input specs. VID (voltage input differential) min is 100mv - that is a 100 mv p-p waveform is within spec to drive a LVPECL input. The central point of that waveform, the X or crossing point is defined by VIX(min and max). Notice the wide range. Inputs from 0.5V to over 2.3V is the input detector ability to detect this small 100mv signal. 100 Sample interconnections Zo = 50 ohm For example, from 0.450v through 0.550 is the Min VIX with Min VID value superimposed. On the other end, a signal can be valid if moving between 2.3V and 2.4V - basing the 100mv on the high VIX. 51 51 Notice the following drawing. The theorical VTT of 1.25v is based on the center of the VOX of LVDS,(which doesnt’ need a VTT voltage due to the current mirror design), the capacitors are used to level shift the output signals “about ground” and is often used when transmitting a signal across long transmission lines. The dual voltage dividers are simply level shifting back to the mid point of LVPECL. LVDS is fully a. PECL to PECL This PECL or LVPECL input is taking differential lines and having them terminate the EIA 50 ohm resistors into the standard termination voltage of VCC-2V or 1.3 volts for 3.3V. When working with 2.5V, tradition flies into rules and VTT becomes ground saving design from the 0.5V VTT voltage. 3.3V LVDS OUTPUT 70 70 51 51 LVPECL Termination at the Receiver pins Zo = 50 ohm VTT (1.3V) Zo = 50 ohm 0.1uf 51 51 51 1.4V 51 capable of driving cable directly and the use of capacitors is used to isolate the VTT value from the LVDS output. Allowing LVDS to drive 100 ohms directly is the cleanest interface to implement, the level shifting is most flexable and allows for unique applications. Typical 3.3V PECL, LVPECL Output into PECL , LVPECL input b. LVDS to PECL This level translation can occur since the LVPECL or PECL input requires as little as 100mv. LVDS is a Low Voltage Differential Signaling description. Actually the output 3 [+] Feedback Level Translation and Termination Methods c. HSTL to PECL d. LVTTL to PECL LVTTL or single ended connection to differential parts are common as crystal buffers - those with LVTTL outputs. The FastEdgeTM does not have to have external termanations like this in order to function in single ended mode. HSTL inputs • High Speed Transceiver Logic Single - Differential Mode • Power 1.5 V Power is not a JEDEC spec - just I/O. • Owner JEDEC JESD8-6 VDD • Usage backplane, transmission lines noisy environment R1 • Noise Immunity ; 150 mV The Spec levels V REF • VOH(ac) min = 1.10 C1 R2 0 .1 u F • VOL(ac) max = 0.40 S in g le E n d e d L in e D riv in g a D iffe re n tia l in p u t Here we go again - If the HSTL driver provides the expected minimum VOD or simply since it is defined as a single ended spec 2*(VOH-VOL) or 1.4V p-p and uses the VOX of 0.75 then a simple connection is feasable. Naturally, a voltage divider design provides some flexability This is the typical CMOS method, when inputs were not self biasing, required calculation of a voltage divider such as this. Zo = 50 ohm 50 Zo = 50 ohm 0.75V 50 Vlow VIN - P-P R1 0.0 3.3V 1K ohm 1K ohm 1.65 V 0.0 2.5V 1K ohm 600 ohm 1.25 V 1.0 2.5V 1K ohm 2.2K ohm 2.25 V 3.3V 70 70 LVPECL CLKA VCC 0 CLKA# CLKB 0.1uf 51 51 VT = 0.75v 51 51 VREF FastEdgeTM utilizes pull-down resistors on the true input and on the inversion input there is both pull-up and pull-down resistors putting the input into a known state. A LVTTL input signal is simply applied directly to the true input. A data sheet design is shown below. The familular DC blocking dual VTT interface. Besides HSTL OUTPUT R2 1.4V VCC CLKB# flexability, this model places the waveform at the center of the spec’d crossing point. By doing so, greater signal margin is attained. .. CLK_SEL 1 .. Q0 Q0# Q3 Q3# Q4 Q4# Q9 Q9# 4 [+] Feedback Level Translation and Termination Methods Therefore the design engineer has fewer parts to place and the quality engineer has a higher quality design (fewer parts). Production likes the throughput of the pick and place machines as they have fewer parts now to place. If you put terminations on the inversion inputs you will alter the trip point of the gate. This may be undesirable or actually desireable for skew or level placement. Naturally input edge rates allow for little skew gain - if the rise/fall were long, then skew is logical. Zo = 50 ohm 50 Zo = 50 ohm 0.75V 50 Standard HSTL to HSTL conditioning. ENB A controlled LVTTL input CLKA b. To HSTL from PECL CLKA# CLKB A buffered LVTTL input VCC The load for 2.5V PECL is normally 50 ohm that is terminated into 0.5V or 0.0V by convension. Termination at 0.75 for PECL is slightly high, however, functionally just fine on the open emitter driver. VCC CLKB# Now for the waveform calculations. CLK_SEL An Inverting LVTTL input FastEdge VIDhstl = VODpecl = 375mv (minimum). HSTL VID(min) input(min) spec = 400mv. 2.5V PECL driving the HSTL input. Zo = 50 ohm HSTL Inputs • High Speed Transceiver Logic • Single - Differential Mode 50 Zo = 50 ohm 0.75V 50 • Power 1.5 V • Owner JEDEC JESD8-6 • Usage backplane, transmission lines, noisy environment • Noise Immunity ; 150 mV The Spec levels c. To HSTL from LVDS The load for the LVDS is the standard 100 ohm. • VIH(ac) min = 0.95 Now for the waveform calculations. • VIL(ac) max = 0.55 VIDHSTL = VODLVDS = 247mv ; 500mv B version. Sample interconnections HSTL VID(min) input(min) spec = 200mv 2. To HSTL input from : 1.5v a. To HSTL from HSTL HSTL is a rather old spec. The spec was developed for the need of a 1.5V clock in whatever logic family supply the developer could do. The first versions were 5 Volt core logic. Current designs are 3.3V and 2.5V cores. The FastEdgeTM has HSTL inputs. These inputs are differential and function much like any other differential or single ended input. The input levels are somewhat different, however for the most part, other logic levels swing through these levels. 51 LVDS 51 HSTL 100 0.1uf 51 51 0.75V The HSTL to HSTL interface consists of termination loads at the end of the transmission line, if it were 1 mm or 1 M. Some drivers are series matched and others have symetrical source and sink 50 ohm resistors to VTT. One of thse is shown below. © Cypress Semiconductor Corporation, 2003. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress Semiconductor against all charges. [+] Feedback