Dual, Low Power Video Op Amp AD828

advertisement

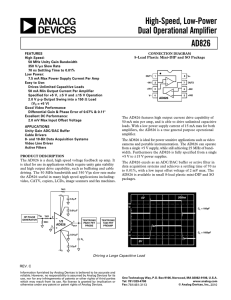

a Dual, Low Power Video Op Amp AD828 FUNCTIONAL BLOCK DIAGRAM FEATURES Excellent Video Performance Differential Gain & Phase Error of 0.01% & 0.05 High Speed 130 MHz 3 dB Bandwidth (G = +2) 450 V/s Slew Rate 80 ns Settling Time to 0.01% Low Power 15 mA Max Power Supply Current High Output Drive Capability: 50 mA Minimum Output Current per Amplifier Ideal for Driving Back Terminated Cables Flexible Power Supply Specified for +5 V, 5 V and 15 V Operation 3.2 V Min Output Swing into a 150 Load (VS = 5 V) Excellent DC Performance 2.0 mV Input Offset Voltage Available in 8-Lead SOIC and 8-Lead Plastic Mini-DIP The AD828 is a low cost, dual video op amp optimized for use in video applications which require gains of +2 or greater and high output drive capability, such as cable driving. Due to its low power and single supply functionality, along with excellent differential gain and phase errors, the AD828 is ideal for power sensitive applications such as video cameras and professional video equipment. With video specs like 0.1 dB flatness to 40 MHz and low differential gain and phase errors of 0.01% and 0.05°, along with 50 mA of output current per amplifier, the AD828 is an excellent choice for any video application. The 130 MHz gain bandwidth and 450 V/µs slew rate make the AD828 useful in many high speed applications including: video monitors, CATV, color copiers, image scanners and fax machines. V 1 8 V+ –IN1 2 7 OUT2 +IN1 3 6 –IN2 V– 4 5 +IN2 AD828 The AD828 is fully specified for operation with a single +5 V power supply and with dual supplies from ± 5 V to ± 15 V. This power supply flexibility, coupled with a very low supply current of 15 mA and excellent ac characteristics under all power supply conditions, make the AD828 the ideal choice for many demanding yet power sensitive applications. The AD828 is a voltage feedback op amp which excels as a gain stage (gains >+2) or active filter in high speed and video systems and achieves a settling time of 45 ns to 0.1%, with a low input offset voltage of 2 mV max. The AD828 is available in low cost, small 8-lead plastic miniDIP and SOIC packages. 0.03 0.1F 0.02 VIN RT 75 RBT 75 1/2 AD828 0.1F 75 RT 75 –V 1k 1k Figure 1. Video Line Driver REV. B Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. DIFFERENTIAL PHASE – Degrees DIFF GAIN 0.01 0.07 0.06 DIFFERENTIAL GAIN – Percent PRODUCT DESCRIPTION OUT1 DIFF PHASE 0.05 0.04 5 10 SUPPLY VOLTAGE – Volts 15 Figure 2. Differential Phase vs. Supply Voltage One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2000 AD828–SPECIFICATIONS (@ T = +25C, unless otherwise noted) A Parameter Conditions VS Min AD828 Typ DYNAMIC PERFORMANCE –3 dB Bandwidth Gain = +2 ±5 V ± 15 V 0, +5 V ±5 V ± 15 V 0, +5 V ±5 V ± 15 V 0, +5 V ±5 V ± 15 V 0, +5 V 60 100 30 35 60 20 30 30 10 15 30 10 85 130 45 55 90 35 43 40 18 25 50 19 MHz MHz MHz MHz MHz MHz MHz MHz MHz MHz MHz MHz 22.3 MHz 7.2 350 450 250 45 45 80 80 MHz V/µs V/µs V/µs ns ns ns ns ± 15 V ± 5 V, ± 15 V ± 5 V, ± 15 V ± 15 V ±5 V 0, +5 V ± 15 V ±5 V 0, +5 V –78 10 1.5 0.01 0.02 0.08 0.05 0.07 0.1 dB nV/√Hz pA/√Hz % % % Degrees Degrees Degrees ± 5 V, ± 15 V 0.5 ± 5 V, ± 15 V 10 3.3 ± 5 V, ± 15 V 25 Gain = –1 Bandwidth for 0.1 dB Flatness Gain = +2 CC = 1 pF Gain = –1 CC = 1 pF Full Power Bandwidth1 Slew Rate Settling Time to 0.1% Settling Time to 0.01% NOISE/HARMONIC PERFORMANCE Total Harmonic Distortion Input Voltage Noise Input Current Noise Differential Gain Error (RL = 150 Ω) Differential Phase Error (RL = 150 Ω) VOUT = 5 V p-p RLOAD = 500 Ω VOUT = 20 V p-p RLOAD = 1 kΩ RLOAD 1 kΩ Gain = –1 ±5 V –2.5 V to +2.5 V 0 V–10 V Step, AV = –1 –2.5 V to +2.5 V 0 V–10 V Step, AV = –1 FC = 1 MHz f = 10 kHz f = 10 kHz NTSC Gain = +2 NTSC Gain = +2 DC PERFORMANCE Input Offset Voltage ± 15 V ±5 V ± 15 V 0, +5 V ±5 V ± 15 V ±5 V ± 15 V 300 400 200 TMIN to TMAX Offset Drift Input Bias Current TMIN TMAX Input Offset Current TMIN to TMAX Offset Current Drift Open Loop Gain VOUT = ± 2.5 V RLOAD = 500 Ω TMIN to TMAX RLOAD = 150 Ω VOUT = ± 10 V RLOAD = 1 kΩ TMIN to TMAX VOUT = ± 7.5 V RLOAD = 150 Ω (50 mA Output) INPUT CHARACTERISTICS Input Resistance Input Capacitance Input Common-Mode Voltage Range ± 15 V ± 15 V ±5 V ± 15 V 0, +5 V Common-Mode Rejection Ratio VCM = +2.5 V, TMIN to TMAX VCM = ± 12 V TMIN to TMAX –2– 0.3 ±5 V ±5 V ± 15 V ± 15 V Max 0.02 0.03 0.09 0.1 2 3 6.6 10 4.4 300 500 Unit mV mV µV/°C µA µA µA nA nA nA/°C 3 2 2 5 5.5 2.5 9 V/mV V/mV 3 5 V/mV +3.8 –2.7 +13 –12 +3.8 +1.2 82 86 84 300 1.5 +4.3 –3.4 +14.3 –13.4 +4.3 +0.9 100 120 100 kΩ pF V V V V V V dB dB dB 4 V/mV V/mV V/mV REV. B AD828 Parameter OUTPUT CHARACTERISTICS Output Voltage Swing Conditions VS Min Typ RLOAD = 500 Ω RLOAD = 150 Ω RLOAD = 1 kΩ RLOAD = 500 Ω ±5 V ±5 V ± 15 V ± 15 V 3.8 3.6 13.7 13.4 ±V ±V ±V ±V RLOAD = 500 Ω 0, +5 V ± 15 V ±5 V 0, +5 V ± 15 V 3.3 3.2 13.3 12.8 +1.5, +3.5 50 40 30 90 8 ±V mA mA mA mA Ω dB dB V/µs Output Current Short-Circuit Current Output Resistance MATCHING CHARACTERISTICS Dynamic Crosstalk Gain Flatness Match Skew Rate Match DC Input Offset Voltage Match Input Bias Current Match Open-Loop Gain Match Common-Mode Rejection Ratio Match Power Supply Rejection Ratio Match POWER SUPPLY Operating Range Open Loop f = 5 MHz G = +1, f = 40 MHz G = –1 ± 15 V ± 15 V ± 15 V –80 0.2 10 TMIN to TMAX TMIN to TMAX VO = ±10 V, RL = 1 kΩ, TMIN to TMAX VCM = ± 12 V, TMIN to TMAX ± 5 V to ± 15 V, TMIN to TMAX ± 5 V, ± 15 V ± 5 V, ± 15 V ± 15 V ± 15 V 0.5 0.06 0.01 100 100 Dual Supply Single Supply Power Supply Rejection Ratio ± 2.5 +5 ±5 V ±5 V ±5 V Quiescent Current TMIN to TMAX TMIN to TMAX VS = ± 5 V to ± 15 V, TMIN to TMAX 80 80 14.0 14.0 80 NOTES 1 Full power bandwidth = slew rate/2 π VPEAK. Specifications subject to change without notice. Max Unit 2 0.8 0.15 mV µA mV/V dB dB ± 18 +36 15 15 15 V V mA mA mA dB 90 ORDERING GUIDE Temperature Range Model Package Description AD828AN –40°C to +85°C AD828AR –40°C to +85°C AD828AR-REEL7 –40°C to +85°C AD828AR-REEL –40°C to +85°C ABSOLUTE MAXIMUM RATINGS 1 Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ± 18 V Internal Power Dissipation2 Plastic DIP (N) . . . . . . . . . . . . . . . . . . See Derating Curves Small Outline (R) . . . . . . . . . . . . . . . . . See Derating Curves Input Voltage (Common Mode) . . . . . . . . . . . . . . . . . . . . ± VS Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . ± 6 V Output Short Circuit Duration . . . . . . . . See Derating Curves Storage Temperature Range (N, R) . . . . . . . –65°C to +125°C Operating Temperature Range . . . . . . . . . . . –40°C to +85°C Lead Temperature Range (Soldering 10 sec) . . . . . . . . +300°C Package Option 8-Lead Plastic DIP N-8 8-Lead Plastic SOIC SO-8 7" Tape & Reel SO-8 13" Tape & Reel SO-8 2.0 MAXIMUM POWER DISSIPATION – Watts TJ = +150C NOTES 1 Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. 2 Specification is for device in free air: 8-Lead Plastic DIP Package: θJA = 100°C/Watt 8-Lead SOIC Package: θJA = 155°C/Watt 8-LEAD MINI-DIP PACKAGE 1.5 1.0 0.5 8-LEAD SOIC PACKAGE 0 –50 –40 –30 –20 –10 0 10 20 30 40 50 60 70 AMBIENT TEMPERATURE – C 80 90 Figure 3. Maximum Power Dissipation vs. Temperature for Different Package Types CAUTION ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD828 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality. REV. B –3– WARNING! ESD SENSITIVE DEVICE AD828–Typical Characteristics 7.7 QUIESCENT SUPPLY CURRENT PER AMP – mA INPUT COMMON-MODE RANGE – Volts 20 15 +VCM 10 –V CM 5 7.2 +85°C –40°C 6.2 5.7 0 0 5 10 15 SUPPLY VOLTAGE – Volts 0 20 20 500 15 450 RL = 500 10 15 10 SUPPLY VOLTAGE – Volts 20 RL = 150 5 400 350 0 5 15 10 SUPPLY VOLTAGE – Volts 300 20 0 30 10 15 SUPPLY VOLTAGE – Volts 20 CLOSED-LOOP OUTPUT IMPEDANCE – 100 25 Vs = 15V 20 15 10 Vs = 5V 5 0 10 5 Figure 8. Slew Rate vs. Supply Voltage Figure 5. Output Voltage Swing vs. Supply Voltage OUTPUT VOLTAGE SWING – Volts p-p 5 Figure 7. Quiescent Supply Current per Amp vs. Supply Voltage for Various Temperatures SLEW RATE – V/s OUTPUT VOLTAGE SWING – Volts Figure 4. Common-Mode Voltage Range vs. Supply Voltage 0 +25°C 6.7 100 1k LOAD RESISTANCE – 10k 10 1 0.1 0.01 1k 10k 100k 1M FREQUENCY – Hz 10M 100M Figure 9. Closed-Loop Output Impedance vs. Frequency Figure 6. Output Voltage Swing vs. Load Resistance –4– REV. B 100 6 80 PHASE 5V OR 15V SUPPLIES +100 +80 15V SUPPLIES 5 4 3 60 +60 40 +40 5V SUPPLIES 20 +20 0 2 PHASE MARGIN – Degrees 7 OPEN-LOOP GAIN – dB INPUT BIAS CURRENT – A AD828 0 RL = 1k 1 –60 –40 –20 0 20 40 60 80 100 120 –20 1k 140 10k TEMPERATURE – C Figure 10. Input Bias Current vs. Temperature 100k 1M 10M FREQUENCY – Hz 100M 1G Figure 13. Open-Loop Gain and Phase Margin vs. Frequency 9 130 110 OPEN-LOOP GAIN – V/mV SHORT CIRCUIT CURRENT – mA 15V 8 SOURCE CURRENT 90 SINK CURRENT 70 50 30 –60 7 5V 6 5 4 –40 –20 0 20 40 60 80 100 120 3 100 140 1k LOAD RESISTANCE – TEMPERATURE – C Figure 14. Open-Loop Gain vs. Load Resistance Figure 11. Short Circuit Current vs. Temperature 80 10k 100 80 80 70 PHASE MARGIN 60 60 GAIN BANDWIDTH 50 50 +SUPPLY 70 PSR – dB 70 –3dB BANDWIDTH – MHz PHASE MARGIN – Degrees 90 60 50 –SUPPLY 40 30 20 40 –60 –40 –20 0 20 40 60 80 TEMPERATURE – C 100 120 10 100 40 140 10k 100k 1M FREQUENCY – Hz 10M 100M Figure 15. Power Supply Rejection vs. Frequency Figure 12. –3 dB Bandwidth and Phase Margin vs. Temperature, Gain = +2 REV. B 1k –5– AD828–Typical Characteristics –40 140 VIN = 1V p-p GAIN = +2 HARMONIC DISTORTION – dB –50 CMR – dB 120 100 80 –60 –70 –80 2ND HARMONIC –90 3RD HARMONIC –100 100 60 1k 10k 100k FREQUENCY – Hz 1M 10M Figure 16. Common-Mode Rejection vs. Frequency 10k 100k FREQUENCY – Hz 1M 10M Figure 19. Harmonic Distortion vs. Frequency 30 Hz 50 RL = 1k INPUT VOLTAGE NOISE – nV/ OUTPUT VOLTAGE – Volts p-p 1k 20 RL = 150 10 0 100k 1M 10M FREQUENCY – Hz 40 30 20 10 0 100M 0 10 100 1k 10k FREQUENCY – Hz 100k 10M 1M Figure 20. Input Voltage Noise Spectral Density vs. Frequency Figure 17. Large Signal Frequency Response 10 650 6 550 4 1% 0.1% SLEW RATE – V/s OUTPUT SWING FROM 0 TO ±V 8 0.01% 2 0 –2 1% 0.1% 0.01% –4 450 350 –6 –8 –10 0 20 40 60 80 100 SETTLING TIME – ns 120 140 250 –60 160 –40 –20 0 20 40 60 80 100 120 140 TEMPERATURE – C Figure 21. Slew Rate vs. Temperature Figure 18. Output Swing and Error vs. Settling Time –6– REV. B AD828 10 5 6 1k VIN GAIN – dB VOUT AD828 4 2 1k VS 15V 5V +5V 150 1k 3 2 VS 15V 5V +5V 1k VOUT VIN AD828 0 VS = 15V 1 0 –1 VS = +5V –4 –2 VS = 5V VS = 5V –6 –3 –8 –4 –10 100k 1M 10M FREQUENCY – Hz 1M 10M FREQUENCY – Hz 100M Figure 25. Closed-Loop Gain vs. Frequency, G = –1 DIFF GAIN 0.01 0.06 0.8 0.6 0.4 GAIN – dB 0.02 1.0 DIFFERENTIAL GAIN – Percent 0.03 0.07 VS = +5V –5 100k 100M Figure 22. Closed-Loop Gain vs. Frequency DIFFERENTIAL PHASE – Degrees FLATNESS 50MHz 25MHz 19MHz 150 VS = 15V –2 0.1dB 4 FLATNESS 40MHz 43MHz 18MHz GAIN – dB 8 1pF 0.1dB 1pF 0.2 VS = 15V 0 –0.2 VS = 5V –0.4 DIFF PHASE –0.6 0.05 VS = 5V –0.8 –1.0 100k 0.04 5 15 10 SUPPLY VOLTAGE – Volts Figure 23. Differential Gain and Phase vs. Supply Voltage 1M 10M FREQUENCY – Hz 100M Figure 26. Gain Flatness Matching vs. Supply, G = +2 +5V –30 0.1F VOUT –40 1F CROSSTALK – dB –50 3 VIN –60 5 8 1/2 AD828 1 7 2 –70 1/2 AD828 4 6 RL = 150 0.1F –80 RL RL 1F RL = 1k –90 –100 –110 10k –5V 100k 1M FREQUENCY – Hz 10M USE GROUND PLANE PINOUT SHOWN IS FOR MINIDIP PACKAGE 100M Figure 27. Crosstalk Test Circuit Figure 24. Crosstalk vs. Frequency REV. B –7– AD828–Typical Characteristics CF 5V 1k +VS 50ns 100 3.3F 90 0.01F HP PULSE (LS) V 1k OR FUNCTION IN (SS) GENERATOR 50 2 8 1/2 AD828 3 4 VOUT 1 TEKTRONIX P6201 FET PROBE TEKTRONIX 7A24 PREAMP 10 0.01F 0% RL 5V 3.3F –VS Figure 31. Inverter Large Signal Pulse Response ± 15 VS, CF = 1 pF, RL = 1 kΩ Figure 28. Inverting Amplifier Connection 2V 50ns 200mV 100 100 90 90 10 10 0% 0% 2V 200mV Figure 29. Inverter Large Signal Pulse Response ± 5 VS, CF = 1 pF, RL = 1 kΩ 200mV 10ns Figure 32. Inverter Small Signal Pulse Response ± 15 VS, CF = 1 pF, RL= 1500 Ω 10ns 200mV 100 100 90 90 10 10 0% 0% 200mV 10ns 200mV Figure 30. Inverter Small Signal Pulse Response ± 5 VS, CF = 1 pF, RL = 150 Ω Figure 33. Inverter Small Signal Pulse Response ± 5 VS, CF = 0 pF, RL = 150 Ω –8– REV. B AD828 CF 5V 1k 50ns 1k 100 +VS 90 3.3F 0.01F 2 HP PULSE (LS) VIN OR FUNCTION (SS) GENERATOR 8 1/2 AD828 100 3 4 VOUT 1 TEKTRONIX P6201 FET PROBE TEKTRONIX 7A24 PREAMP 10 0.01F 50 0% RL 5V 3.3F –VS Figure 37. Noninverting Large Signal Pulse Response ± 15 VS, CF = 1 pF, RL = 1 kΩ Figure 34. Noninverting Amplifier Connection 1V 50ns 100mV 100 100 90 90 10 10 0% 0% 2V 200mV Figure 38. Noninverting Small Signal Pulse Response ± 15 VS, CF = 1 pF, RL = 150 Ω Figure 35. Noninverting Large Signal Pulse Response ± 5 VS, CF = 1 pF, RL = 1 kΩ 100mV 100mV 10ns 100 100 90 90 10 10 0% 0% 200mV 10ns 200mV Figure 39. Noninverting Small Signal Pulse Response ± 5 VS, CF = 0 pF, RL = 150 Ω Figure 36. Noninverting Small Signal Pulse Response ± 5 VS, CF = 1 pF, RL = 150 Ω REV. B 10ns –9– AD828 THEORY OF OPERATION Circuit Board Layout The AD828 is a low cost, dual video operational amplifier designed to excel in high performance, high output current video applications. Input and output runs should be laid out so as to physically isolate them from remaining runs. In addition, the feedback resistor of each amplifier should be placed away from the feedback resistor of the other amplifier, since this greatly reduces interamp coupling. The AD828 (Figure 40) consists of a degenerated NPN differential pair driving matched PNPs in a folded-cascode gain stage. The output buffer stage employs emitter followers in a class AB amplifier that delivers the necessary current to the load while maintaining low levels of distortion. The AD828 will drive terminated cables and capacitive loads of 10 pF or less. As the closed-loop gain is increased, the AD828 will drive heavier cap loads without oscillating. +VS Choosing Feedback and Gain Resistors In order to prevent the stray capacitance present at each amplifier’s summing junction from limiting its performance, the feedback resistors should be ≤ 1 kΩ. Since the summing junction capacitance may cause peaking, a small capacitor (1 pF–5 pF) may be paralleled with Rf to neutralize this effect. Finally, sockets should be avoided, because of their tendency to increase interlead capacitance. Power Supply Bypassing Proper power supply decoupling is critical to preserve the integrity of high frequency signals. In carefully laid out designs, decoupling capacitors should be placed in close proximity to the supply pins, while their lead lengths should be kept to a minimum. These measures greatly reduce undesired inductive effects on the amplifier’s response. OUTPUT –IN Though two 0.1 µF capacitors will typically be effective in decoupling the supplies, several capacitors of different values can be paralleled to cover a wider frequency range. +IN PARALLEL AMPS PROVIDE 100 mA TO LOAD –VS Figure 40. AD828 Simplified Schematic INPUT CONSIDERATIONS An input protection resistor (RIN in Figure 34) is required in circuits where the input to the AD828 will be subjected to transient or continuous overload voltages exceeding the ± 6 V maximum differential limit. This resistor provides protection for the input transistors by limiting their maximum base current. By taking advantage of the superior matching characteristics of the AD828, enhanced performance can easily be achieved by employing the circuit in Figure 41. Here, two identical cells are paralleled to obtain even higher load driving capability than that of a single amplifier (100 mA min guaranteed). R1 and R2 are included to limit current flow between amplifier outputs that would arise in the presence of any residual mismatch. For high performance circuits, it is recommended that a “balancing” resistor be used to reduce the offset errors caused by bias current flowing through the input and feedback resistors. The balancing resistor equals the parallel combination of RIN and RF and thus provides a matched impedance at each input terminal. The offset voltage error will then be reduced by more than an order of magnitude. 1k +VS 1F 0.1F 1k 2 R1 5 8 1/2 AD828 1 3 VOUT VIN R2 5 5 APPLYING THE AD828 The AD828 is a breakthrough dual amp that delivers precision and speed at low cost with low power consumption. The AD828 offers excellent static and dynamic matching characteristics, combined with the ability to drive heavy resistive loads. As with all high frequency circuits, care should be taken to maintain overall device performance as well as their matching. The following items are presented as general design considerations. 1/2 AD828 1k 6 4 RL 7 0.1F 1F 1k –VS Figure 41. Parallel Amp Configuration –10– REV. B AD828 AIN 3 3 RZ RZ 1/2 AD828 510 1/2 AD828 1 1 2 2 510 510 510 100FT RG59A/U RZ = 75 510 536 536 6 BOUT BIN 510 7 6 1/2 AD828 1/2 AD828 5 7 AOUT 5 Figure 42. Bidirectional Transmission CKT Full-Duplex Transmission Superior load handling capability (50 mA min/amp), high bandwidth, wide supply voltage range and excellent crosstalk rejection makes the AD828 an ideal choice even for the most demanding high speed transmission applications. The schematic below shows a pair of AD828s configured to drive 100 feet of coaxial cable in a full-duplex fashion. Two different NTSC video signals are simultaneously applied at AIN and BIN and are recovered at AOUT and BOUT, respectively. This situation is illustrated in Figures 43 and 44. These pictures clearly show that each input signal appears undisturbed at its output, while the unwanted signal is eliminated at either receiver. The transmitters operate as followers, while the receivers’ gain is chosen to take full advantage of the AD828’s unparalleled CMRR. (In practice this gain is adjusted slightly from its theoretical value to compensate for cable nonidealities and losses.) RZ is chosen to match the characteristic impedance of the cable employed. Finally, although a coaxial cable was used, the same topology applies unmodified to a variety of cables (such, as twisted pairs often used in telephony). 500mV 500mV 100 100 90 AIN 90 BIN BOUT AOUT 10 10 0% 0% 500mV 10µs 500mV 10µs Figure 44. B Transmission/A Reception Figure 43. A Transmission/B Reception +15V A High Performance Video Line Driver 0.1F The buffer circuit shown in Figure 45 will drive a backterminated 75 Ω video line to standard video levels (1 V p-p) with 0.1 dB gain flatness to 40 MHz with only 0.05° and 0.01% differential phase and gain at the 3.58 MHz NTSC subcarrier frequency. This level of performance, which meets the requirements for high-definition video displays and test equipment, is achieved using only 7 mA quiescent current/amplifier. VIN 2 RT 75 1.0F 8 1/2 AD828 75 1 RBT 75 3 4 –15V 0.1F 1.0F 1k 1k Figure 45. Video Line Driver REV. B –11– RT 75 AD828 LOW DISTORTION LINE DRIVER The AD828 can quickly be turned into a powerful, low distortion line driver (see Figure 46). In this arrangement the AD828 can comfortably drive a 75 Ω back-terminated cable, with a 5 MHz, 2 V p-p input; all of this while achieving the harmonic distortion performance outlined in the following table. 2nd Harmonic 1. No Load 2. 150 Ω RL Only 3. 150 Ω RL 7.5 Ω RC –78.5 dBm –63.8 dBm –70.4 dBm +VS 1k 1F 0.1F 3 8 1/2 AD828 1 2 RC 7.5 1k 1k In this application one half of the AD828 operates at a gain of 2.1 and supplies the current to the load, while the other provides the overall system gain of 2. This is important for two reasons: the first is to keep the bandwidth of both amplifiers the same, and the second is to preserve the AD828’s ability to operate from low supply voltage. RC varies with the load and must be chosen to satisfy the following equation: 6 1/2 VIN AD828 5 4 75 75 RL 7 75 1F C1823a–0–6/00 (rev. B) 00879 Configuration 1.1k 0.1F –VS RC = MRL, where M is defined by [(M + 1) GS = GD] and GD = Driver's Gain, GS = System Gain. Figure 46. Low Distortion Amplifier OUTLINE DIMENSIONS Dimensions shown in inches and (mm). 8-Lead Plastic Mini-DIP (N) Package 8 5 1 4 PIN 1 0.25 (6.35) 0.1968 (5.00) 0.1890 (4.80) 0.31 (7.87) 0.1574 (4.00) 0.1497 (3.80) 0.30 (7.62) REF 0.39 (9.91) MAX 0.180.03 (4.570.76) 0.125 (3.18) MIN 1 4 0.2440 (6.20) 0.2284 (5.80) 0.0196 (0.50) 45 0.0099 (0.25) 0.0098 (0.25) 0.0040 (0.10) 0.0110.003 (0.280.08) SEATING PLANE 0.0688 (1.75) 0.0532 (1.35) 0.0192 (0.49) 0.0138 (0.35) 8 0.0098 (0.25) 0 0.0500 (1.27) 0.0160 (0.41) 0.0075 (0.19) 0° PRINTED IN U.S.A. SEATING PLANE 5 0.0500 (1.27) BSC 15° 0.033 (0.84) NOM 8 PIN 1 0.0350.01 (0.890.25) 0.1650.01 (4.190.25) 0.0180.003 0.10 (0.460.08) (2.54) BSC 8-Lead SO (R) Package –12– REV. B