A 1.1-Gbit/s, 23-dBm, 10-GHz Outphasing Modulator with 60

advertisement

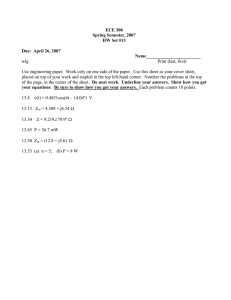

A 1.1-Gbit/s, 23-dBm, 10-GHz Outphasing Modulator with 60-dB Dynamic Range Mohammad Mehrjoo, Samet Zihir Gabriel Rebeiz, James Buckwalter Department of Electrical and Computer Engineering University of California, San Diego Outline • Introduction • System level of the proposed modulator • Circuit design of the key building blocks • Measurement results • Conclusion Slide 2 Introduction n Tradeoff between linearity and efficiency in PAs. Linearity Efficiency Modulation PA class A, AB high low Amplitude PA class D, E low high Phase OFDM, multi-channels of QAM, high PAPR High linear PAs n Two low linearity high efficiency PAs, rather than one high linearity low efficiency PA. n Outphasing, Linear Amplification with Nonlinear Components (LINC) Slide 3 Outphasing Concept Amplitude / Phase Modulation Slide 4 Phase Modulation High Efficiency Low Linearity Power Combiner Block Diagram Slide 5 Submitted, JSSC Key Building Blocks (Baseband) • Digital-to-analog-converter (DAC) • How many bits are needed? • DR Phase Error • Phase Resolution • DAC floor plan. Slide 6 DAC number of bits DR as a Function of the Phase Error Outphased signals in the presence of phase error: DR as a function of δ Slide 7 Phase Res. vs Outphasing Angle The phase resolution provided by a DAC is higher as Φ increases. Phase resolution at Φ close to 90o determines the DR. Minimum 10 bits are needed for a phase resolution better than 0.1o. Slide 8 DAC Floor Plan 5 thermometer MSB and 5 binary LSB bits. Slide 9 Mehrjoo and Buckwalter, JSSC 14 Key Building Blocks (RF) • Quadrature double-balanced mixer • How linear is the mixer? • LO routing on the chip Slide 10 Mixer and Stacked-FET Buffer Each channel generates 20 dBm to derive off-chip GaN/GaAs PA. Stacked-FET current buffer to prevent from break down. Current Bleeder for high linearity. Slide 11 Mixer Linearity Simulated OIP3 and P1dB. Two-tone test with LO at 10 GHz and IF at 10 and 11 MHz. One-tone test with LO at 10 GHz and IF at 10 MHz. Slide 12 LO Chain Single-ended external LO Slide 13 Send the LO to both channels Chip Photo Block Power Consumption Staked-FET + Mixer + DAC 280mA From 4V DAC LO Chain Digital Total 235mA from 1.5V 78mA from 1.5V 135mA from 1V 1.72W n 45nm SOI technology n Area = 9 mm2 n Testing on board Slide 14 Measurement Setup 30GHz 16GHz 20GHz 16GHz DEMUX limits the bandwidth to 400MHz. Slide 15 Calibration Calibrating both I/Q channels. LO at 10GHz and IF at 10MHz. High resolution DACs can adjust the dc level and swing amplitude to improve the measured LO leakage and sideband suppression. Slide 16 Measured P1dB and OIP3 Current Swing is limited by DAC current. P1dB is slightly larger than 20dBm. (Simulated P1dB=21.8dBm) (Simulated OIP3=34.2dBm) Slide 17 Measured Dynamic Range 60.3 dB DR with less than 1-dB steps. Slide 18 Constant Envelop Outphased Signals 10MHz 256QAM waveform at 10GHz. Slide 19 Measured 16QAM 10MHz 6.1dB PAPR 2.1% EVM -37.0dBc ACLR 133MHz 6.6dB PAPR 3.4% EVM -35.1dBc ACLR Slide 20 Measured 64QAM 10MHz 6.6dB PAPR 2.2% EVM -36.9dBc ACLR 133MHz 7.1dB PAPR 3.5% EVM -35.2dBc ACLR Slide 21 Measured 256QAM 10MHz 6.3dB PAPR 2.2% EVM -37dBc ACLR 133MHz 7.2dB PAPR 3.5% EVM -35.2dBc ACLR Capable of 1.1Gbit/s data transmission. Slide 22 Measured LTE 100-MHz LTE carrier aggregation. 8.3dB PAPR. -35.9dBc ACLR. Slide 23 Conclusion • Microwave outphasing modulator including all the system blocks from digital to RF on-chip. • Using 10-bit DACs, modulator provides a 60dB dynamic range. • Modulator is capable of transmitting 100-MHz LTE and 1.1Gbit/s 256QAM waveforms. • Each channel delivers 20dBm which is sufficient to drive high-power off-chip PAs without need for any pre-amplification. Slide 24 Back up Slides • Stacked-FET Structure • SOI vs Bulk CMOS • How does current bleeder improve the linearity? Slide 25 Stacked-FET Current Buffer Keeping the voltage across the individual transistors below the breakdown. D RL ⎛ C ⎞ ⎛ 1 1 ⎞ Z i = ⎜1 + gsi ⎟ .⎜ || ⎟⎟ ⎜ C g sC i ⎠ ⎝ mi gsi ⎠ ⎝ RL M3 M3 C3 Pornpromlikit et al., TMTT 2010 C3 C M2 M2 C2 Z3 > Z 2 > Z1 C2 B M1 M1 C1 A 6 C1 IB IB 4 3 1 V 3V V 1.5 2 0.5 vds vdg vgs 0 .5 1 0 1 Time (ns) Slide 26 D C B A 5 Iu -0.5 0 v3 > v2 > v1 1.5 .5 1 Time (ns) 1.5 CMOS SOI for Stacking Triple Well Bulk CMOS • No shared body. – Necessary for stacking – Triple well in bulk CMOS or CMOS SOI • Buried oxide is much thicker than depletion region. – Lower parasitic capacitances for SOI Slide 27 Bulk CMOS SOI CMOS Current Bleeder VD M1 M1 VG Zin IB IB Iu 0.67WLCOX+WCOV 0.5WLCOX+WCOV Lin et al., JSSC’ 2009 CGS Saturation Triode WCOV Current bleeder improves the linearity: n M1 always on, constant parasitic capacitance n Zin Slide 28 Off CGD VTH VD+VTH VGS Current Bleeder 24 |Zin| (Ohm) SFDR (dB) 70 65 68.6 dB at 10mA I =1m b 22 I =5m 20 Ib=10m 18 I =15m b b 16 14 12 60 0 10 20 30 40 I (mA), f=500 MHz 50 60 u 55 0 10 20 30 I (mA) B Current bleeder improves the linearity: n Less variation in Zin Slide 29 higher IB higher gm lower Zin higher IB triode, lower gm higher Zin