digital design and implementaion of proportional-integral

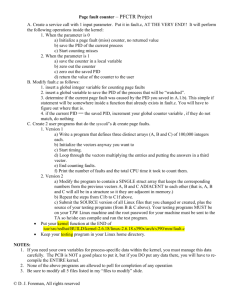

advertisement