I/Q transmit modulator

advertisement

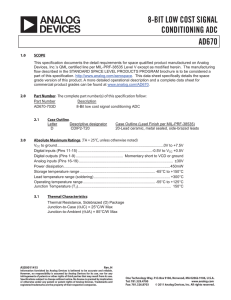

INTEGRATED CIRCUITS SA900 I/Q transmit modulator Preliminary specification IC17 Data Handbook 1997 Sept 16 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 DO NOT DISTRIBUTE WITHOUT ECN DATED AFTER Sept 16, 1997 DESCRIPTION PIN CONFIGURATION The SA900 is a monolithic high performance, multi-function transmit modulator for use in cellular radio applications, fabricated in QUBiC BiCMOS technology. The SA900 features both analog (AMPS) mode and complex, I/Q digital (NADC IS–136) mode quadrature modulation functions, a PLL synthesizer with VCO, crystal oscillator, programmable prescalers and Gilbert cell multiplier phase detector with programmable charge pump output. The DUALTX output can be used in DUAL mode cellular phone applications with the AMPS and NADC modulation being applied to the I/Q baseband inputs. The DUALTX output also provides 6-bit power control with 40dB of gain control in 0.63dB steps. In addition, buffered crystal oscillator programmable prescaler outputs are provided to support system clock reference needs. Programming of the SA900 functions are realized by a high speed 3-wire serial interface. The SA900 can be programmed into a sleep mode (low current mode providing crystal oscillator and Master Clock functions), a standby mode (providing crystal oscillator, Master Clock, System Clock 1 and Transmit LO buffer functions), and the AMPS mode and the DUAL mode configurations. GND TXLO_2 TXLO_1 Vcc PHSOUT GND Vcc 3 5 Vcc GND 2 4 TANK_2 41 40 39 38 37 1 GND TANK_1 Q I 48 47 46 45 44 43 42 Q I Vcc GND LO_1 LO_2 Vcc BE Package 6 7 8 9 IPEAK 10 GND 11 XTAL_1 12 FEATURES 36 Vcc 35 GND 34 DUALTX 33 GND 32 Vcc 31 AMPSTX 30 GND 29 Vcc 28 GND 27 Vcc 26 Vcc 25 GND TXEN STROBE DATA CLOCK CLKSET MCLK GND CLK2 GND CLK1 XTAL_2 Vcc 13 14 15 16 17 18 19 20 21 22 23 24 • VCC = 4.0V • Tx output frequency = 900MHz • Direct modulation of RF • DUAL mode, on-chip PA control • I/Q modulator • Single sideband quadrature LO generation with no external SR00636 Figure 1. Pin Configuration • Selective power-down – Low power AMPS/TACS mode – Low power dual mode NADC adjustments required • On-chip crystal oscillator with 3 buffered outputs • AMPS/TACS compatible • On-chip VCO • 48-Pin TQFP package APPLICATIONS • North American Digital Cellular (TDMA IS-136) ORDERING INFORMATION DESCRIPTION 48-Pin Plastic Low Profile Quad Flat Package (LQFP) 1997 Sept 16 2 TEMPERATURE RANGE ORDER CODE DWG # -40 to +85°C SA900BE SOT313-2 853- Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 BLOCK DIAGRAM LO_2 I LO_1 TXLO_2 TXLO LPF TXLO_1 PHASE I QQ VGA LPF PA DUALTX PA AMPSTX SHIFT TANK_1 NETWORK IMAGE REJECT MIXER VCO LPF TANK_2 VCO ÷N ÷A8/1 PHSOUT PHS DET VGA CONTROL AD BIAS BG AD ÷B8/1 IPEAK 2 SE N<0:1> AD SM1 SM2 Y X AD 6 XTAL_1 XTAL_2 XTAL OSC ÷ 3/1 X SM1 ÷ 2/1 Y SM2 ÷4/5/1 CONTROL LOGIC CONV2 SM1 CLK1 SM2 CLK2 MCLK CLKSET DATA CLOCK STROBE TXEN SR00637 Figure 2. Block Diagram 1997 Sept 16 3 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 PIN DESCRIPTIONS Pin Description I Non-inverting I Mod Signal I Inverting I Mod Signal TXLO_1/2 DUALTX Second LO Input (differential/single-ended input) RF output (850MHz) digital (DUAL) mode, complex modulated output Q Non-inverting Q Mod Signal Q Inverting Q Mod Signal CLK1 Buffered oscillator output (XO ÷3/÷1) MCLK Buffered oscillator output (XO ÷4/÷5/÷1) CLK2 Buffered oscillator output (XO ÷2/÷1) AMPSTX RF output (850MHz) AMPS mode VCC +5VDC power supply GND Ground Data Serial data input Clock Serial clock input Strobe Data strobe input TXEN AMPS and Dual Mode transmit enable CLKSET Program control pin for MCLK prescaler XTAL1 Crystal oscillator base input XTAL2 Crystal oscillator emitter output PHSOUT Phase comparator charge pump output TANK_1 VCO differential tank TANK_2 VCO differential tank LO_1/2 Buffered differential TXLO output IPEAK 1997 Sept 16 Phase comparator current programming 4 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 GND_LO GND GND GND GND GND_CTRL GND GND GND GND GND GND GND 1 4 11 16 18 25 28 30 33 35 37 39 45 GND VCC_LO VCC VCC VCC VCC VCC VCC VCC VCC VCC VCC_CTRL 48 5 8 14 27 29 32 36 38 44 26 VCC 2 50Ω VCC 50Ω 3 VCC 6 VCC 7 VCC VCC 12 0.1/6.4 mA 9 VCC 0.1/6.4 mA 13 SR00638 Figure 3. Pin Diagrams 1997 Sept 16 5 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 VCC VCC 500Ω 15 17 19 20 VCC 500Ω 21 22 23 24 VCC VCC 600Ω 30Ω 31 34 VCC 40 42 680Ω 680Ω VCC 41 43 VCC 20Ω 46 47 SR00639 Figure 4. Pin Diagrams (cont.) 1997 Sept 16 6 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 ABSOLUTE MAXIMUM RATINGS SYMBOL PARAMETER VCC Supply voltage VIN Voltage applied to any other pin PD Power dissipation, TA = 25°C (still air) RATING UNITS -0.3 to +6 V -0.3 to (VCC + 0.3) V 600 mW TJMAX Maximum operating junction temperature 150 °C PMAX Maximum power input/output +10 dBm TSTG Storage temperature range –65 to +150 °C NOTE: 1. Maximum dissipation is determined by the operating ambient temperature and the thermal resistance, θJA. 48-pin LQFP: θJA = 67°C/W RECOMMENDED OPERATING CONDITIONS SYMBOL VCC PARAMETER RATING UNITS Supply voltage 3.9 to 5.1 V TA Operating ambient temperature range -40 to +85 °C TJ Operating junction temperature -40 to +105 °C DC ELECTRICAL CHARACTERISTICS VCC = +4.0V, TA = 25°C; unless otherwise stated. SYMBOL VCC PARAMETER TEST CONDITIONS Power supply range LIMITS MIN TYP 3.9 Sleep mode MAX 5.1 UNITS V 3.1 Standby mode 8.2 AMPS mode 27.5 ICC Supply current DUAL mode 64 I/I In-phase differential baseband input DC 0.5VCC V Quadraphase differential baseband input DC 0.5VCC V Divide by 4/5/1 ÷4 ÷5 ÷1 Q/Q CLKSET mA VCC 0.5VCC V 0 VIL Clock, data, strobe, TXEN Input low –0.3 0.3VCC V VIH Clock, data, strobe, TXEN Input high 0.7VCC VCC+0.3 V 1997 Sept 16 7 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 AC ELECTRICAL CHARACTERISTICS VCC = +4.0V, TA = 25°C; TANK_1 = 120MHz @ 0 dBm; XO_REF = 30MHz @ –5 dBm; TxLO2 = –13 dBm, unless otherwise stated. SYMBOL PARAMETER TEST CONDITIONS Input power TXLO_1/2 Transmit LO input (AC couple) (50Ω) TANK_1/2 VCO tank differential inputs PHSOUT IPEAK XTAL 1 XTAL_1 CLK1 Phase detector charge pump output PHSOUT programming XO transistor base XO divide 3/1, power down SM1=0, 50% duty cycle ÷3, X=1, ÷1, X=0 CLK2 XO divide 2/1, power down SM2=0 ÷2, Y=1, ÷1, Y=0 XO divide 4/5/1, 50% duty cycle MCLK ÷4, CLKSET = VCC, ÷5, CLKSET = 0.5VCC, ÷1, CLKSET = 0V Serial data clock input, 33% duty cycle CLOCK LIMITS MIN 900 Frequency range 901 Output level 0.5 RSET = 24kΩ, AD=0 200 300 RSET = 24kΩ, AD=1 0.9 1.2 1.5 mA XO frequency 101 30 451 MHz External drive 1501 350 5001 mVP-P Frequency range 3.331 30 451 MHz Output level, 5kΩ || 7pF 0.7 1 1.4 VP-P Frequency range 51 30 451 MHz Output level, 5kΩ || 7pF 0.7 1 Frequency range 21 Output level, 5kΩ || 7pF 0.7 Logic LOW 0.7VCC Frequency range 820 DUAL output, SE=1, AD=1, TXEN=1 (with external matching Figure 9) DUALTX V 400 µA 1.4 VP-P 451 MHz 1.4 VP-P MHz 1 V V 860 MHz +2 dBm 869 to 894MHz -104 dBm 824 to 849MHz -47 dBc 2 to 824MHz -41 dBc 849 to 869MHz -41 dBc 894MHz to 8.49GHz -41 dBc -21 dBc @30kHz -95 dBc/Hz @60kHz -101 dBc/Hz 869 to 894MHz -136 dBm/Hz Frequency range 8 9202 820 VSWR Output level (avg) (I and Q quad, 0dB VGA) Gain flatness 1997 Sept 16 MHz VCC–0.5 2:1 –1.5 TXLO and harmonics Broadband noise power MHz 1401 0.3VCC VSWR Alternate channel noise power 1 1040 101 Logic HIGH Adjacent channel noise power 120 Max clock rate DATA, CLOCK, STROBE, TXEN Spurious output dBm 2:1 Frequency range Output level AMPSTX UNITS MAX -101 -13 VSWR (50Ω) Serial interface (CMOS levels) AMPS output, SE=1, AD=0, TXEN=1 (AC couple) TYP MHz 2:1 0 +2 dBm 1 dB Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 AC ELECTRICAL CHARACTERISTICS (continued) SYMBOL PARAMETER TEST CONDITIONS DUALTX (cont.) 3rd order Linearity (0dB VGA, I and Q inphase) LIMITS TYP -35 -42 dBc -55 dBc 5th order 7th order -65 dBc Carrier suppression (I and Q quadrature) VGA = 0dB -35 -45 dBc Carrier suppression (I and Q quadrature) VGA = –40dB -28 -33 dBc I and Q quadrature -35 -45 dBc 869 to 894MHz –104 dBm 824 to 849MHz –47 dBc 2 to 824MHz –41 dBc 849 to 869MHz –41 dBc 894MHz to 8.49GHz –41 dBc Sideband suppression Spurious output TXLO and harmonics Broadband noise (0dB VGA) Q/Q –21 dBc 869 to 894MHz –136 dBm/Hz 935 to 960MHz –136 dBm/Hz Adjacent channel noise power @30kHz –95 dBc/Hz Alternate channel noise power @60kHz –101 Max frequency 0.8 21 MHz 0.8 1.01 VP-P 0.8 21 MHz 0.8 1.01 VP-P Baseband quadrature differential input Differential modulation level 0.61 Differential input impedance 101 Max frequency I/I Baseband inphase differential input Differential modulation level 0.61 Differential input impedance 10 Frequency range 900 Buffered TXLO differential outputs (AC coupled) LO_1/2 _ MAX UNITS MIN kΩ kΩ 1040 VSWR (single-ended) 2:1 single-ended 50 Output impedance Output Out ut level dBc/Hz MHz Ω 100 Ω single-ended, 50Ω 50 90 mVP-P differential, 100Ω 100 180 mVP-P differential NOTES: 1. Guaranteed by design. 2. Needs a different matching component. Max test frequency is 850MHz with test circuit shown in Figure 11. mode function. The transition of the TXEN, from low to high turns on the modulator. The falling edge of the TXEN signal disables the synthesizer and modulator. The TXLO is a system supplied LO signal. The SA900 buffers the TXLO signal (LO_1/2) for use with the system synthesizer (such as the SA7025) to form the system LO synthesizer loop. The DUAL mode can also be used for AMPS operation. The AMPS and DUAL mode modulation is generated by the system DSP IC to provide the required I/Q baseband modulation for the SA900. The DUAL output provides low broadband noise output power (so that the receiver sensitivity is not degraded) and high linearity to meet cellular phone system needs. Table 1 provides the VGA power control limits. FUNCTIONAL DESCRIPTION Dual Mode Operation The SA900 transmit modulator provides direct single sideband quadrature modulation of the difference of the TXLO and VCO frequencies, while providing quadrature LO signals for the I/Q modulator. The quadrature LO signals are modulated with high linearity by the baseband inphase (I) and quadrature (Q) signals. The summed modulator output produces the lower sideband, while rejecting the upper sideband. The I and Q inputs also provide DC biasing for the modulator inputs. The summed output of the modulator goes to a variable gain amplifier (VGA) to control the output level, it has 40.0dB of attenuation control range, with 0.63dB steps. The power control function is programmed by means of a 6-bit word (see Table 3). The VGA output drives the power amp output stage to provide +2dBm average minimum power level (at 0dB power control) into 50Ω, in conjunction with external matching components on DUALTX. The AD (AMPS/DUAL) and the SE (synthesizer enable) bit control the power up/down of the DUAL 1997 Sept 16 The SA900 DUALTX output is externally matched with either a shunt inductor to VCC and a series capacitor or a shunt inductor to VCC and a series inductor. This matches the DUALTX output to 50Ω. Values of the matching components are dependent on PCB layout, typical values are shown in Figure 9. 9 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 the AMPS mode (AD=0) to a maximum of 6.4mA for the DUAL mode (AD=1) by way of an external current setting resistor placed from IPEAK to circuit ground. The typical loop filter network is shown in Figure 5. The charge pump current output is programmed by Table 1. VGA Power Control Limits VGA Min. Typ. Max. Relative VGA 0 0 0 0 0 1 -1 -.63 -.2 0 2 -1 -.63 -.2 1 3 -1 -.63 -.2 2 4 -1 -.63 -.2 3 5 -1 -.63 -.2 4 6 -1 -.63 -.2 5 7 -1 -.63 -.2 6 where RSET is placed between IPEAK and GROUND. 15 -6.6 -5 -3 7 The PLL frequency is determined by 23 -6.6 -5 -3 15 31 -6.6 -5 -3 23 39 -6.6 -5 -3 31 47 -6.6 -5 -3 39 55 -6.6 -5 -3 47 63 -6.6 -5 -3 55 63 -43.2 -40.4 -37.2 0 AD 0 I OUT 6 AD 1 I OUT 24 VCO XO N 1.25V R SET 1.25V R SET A8 ) 1 B8 ( ) 1 ( where N=6, 7, 8, 9 and A8/1 and B8/1 are controlled by the AD bit (AD=1 A8/1 and B8/1 are divide by 1, AD=0 A8/1 and B8/1 are divide 8). Table 2. Data Word Format 1. Guaranteed to be monotonic. Mnemonics Bits A0 1 (MSB) Address bit 0 (1) A1 2 Address bit 1 (0) A2 3 Address bit 2 (1) A3 4 Address bit 4 (1) PC0 5 Power control bit 0 PC1 6 Power control bit 1 PC2 7 Power control bit 2 PC3 8 Power control bit 3 PC4 9 Power control bit 4 PC5 10 Power control bit 5 N0 11 Divide N bit 0 Synthesizer Operation N1 12 Divide N bit 1 The SA900 synthesizer is comprised of the differential VCO circuit, with external tank components, the Gilbert cell multiplier phase detector with programmable charge pump current, crystal oscillator and programmable prescalers. The charge pump output drives an external second order loop filter. The output of the loop filter is used to provide the control voltage to the VCO tuning varactor to complete the PLL synthesizer. The synthesized VCO output frequency is mixed with the TXLO signal to generate the transmit LO from the lower sideband (the difference of the VCO and TXLO frequencies). The output of VCO is fed to a programmable /N prescaler with user selectable divides of 6, 7, 8 and 9 (all divides configured to provide 50% duty cycle). The output of the /N divider drives the A8/1 prescaler. The A8/1 divide is selected by the AD control bit (AD=1 for /1, and AD=0 for /8). The output of the divide A8/1 is fed into one input of the phase detector. The reference input for the phase comparator is generated from the crystal oscillator (XO) output from the B8/1 prescaler. The B8/1 divide is selected by the AD control bit (AD=0 for /8, and AD=1 for /1). The phase detector compares the prescaled XO reference phase to the VCO prescaled phase, to generate a charge pump output current proportional to the phase error. The phase detector, a Gilbert cell multiplier type, having a linear output from 0 to π (π/2 ± π/2). The charge pump peak output current is programmable from 100µA for AD 13 AMPS/DUAL mode select bit SE 14 Synthesizer enable bit NA 15 NA SM1 16 Sleep mode 1 control bit SM2 17 Sleep mode 2 control bit X 18 Divide 3/1 control bit AMPS Mode Operation The SA900 can be configured to operate in the AMPS mode, where FM modulation is applied to the SA900’s VCO. For the AMPS mode, the VCO is configured with the proper synthesizer bandwidth to allow the application of the AMPS modulation to the VCO varactor tuned tank circuit. The modulated VCO signal is input into an image reject mixer along with the TXLO signal, where the upper sideband is rejected. This single sideband modulated signal then drives the AMPS output power amplifier. The PA provides +2dBm power level into 50Ω, with no external matching components required. The AD (AMPS/DUAL) and the SE (synthesizer enable) bit control the power up/down of the AMPS mode function. The transition of the TXEN signal from low to high turns on the modulator. The falling edge of TXEN signal disables the synthesizer and the modulator. 1997 Sept 16 Function Y 19 Divide 2/1 control bit NA 20 NA NA 21 NA NA 22 NA NA 23 NA NA 24 (LSB) NA VCO Operation The VCO is designed to operate from 90MHz to 140MHz. The VCO tank is configured using a parallel inductor and a dual common cathode tuning varactor diodes. DC blocking capacitors are used to isolate the varactor 10 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 control voltage from the VCO tank DC bias voltages. The VCO tuning voltage is generated from the output of the PLL loop filter. The VCO tank configuration is shown in Figure 6. AMPS/DUAL Mode The A/D mode select enables or disables that portion of the circuitry used for either the AMPS or DUAL mode of operation. Crystal Oscillator (XO) Operation AD 0 1 For cellular radio applications, the SA900 will most likely utilize an external reference TCXO in order to provide the frequency stability necessary to operate to system requirements. The output of the system TCXO can be AC coupled to the XTAL_1 input. However, for applications that do not require such accuracy the XO circuit can be configured as a Colpitts type oscillator with the addition of two external capacitors along with the reference crystal and a trim capacitor as shown in Figure 7. Synthesizer Enable The SE bit turns on and off the synthesizer circuitry. SE 0 1 Programmable Clock Outputs The SM1 bit is used to power down the TXLO buffer, the divide 3/1 prescaler and the CLK1 output buffer. SM1 0 1 The SM2 bit is used to power down the divide 2/1 prescaler and the CLK2. SM2 0 1 The SA900 is configured by means of a 3-wire input (CLOCK, STROBE, DATA) to program the AMPS and DUAL modes, in addition there are two power saving modes of operation, SLEEP and STANDBY. The control logic section of the SA900 is designed using low power CMOS logic. During SLEEP mode only the circuitry required to provide a master clock (MCLK) to the digital portion of the system is enabled. During the STANDBY mode of operation MCLK, CLK1 and the TXLO and buffered LO outputs are powered on, which may be the case when the system is in the receive only mode. In the AMPS or DUAL operational modes all functions of the SA900 are powered on to support receive, transmit and system clock functions. The programming of the SA900 is identical to the programming format of the SA7025 low-voltage 1GHz fractional-N synthesizer, that can be used in conjunction with the SA900 to provide the cellular radio channel selection. A3 1 Divide By N N1 0 0 1 1 1997 Sept 16 X 0 1 Operation Divide 1 Divide 3 Y 0 1 Operation Divide 1 Divide 2 Divide 2 Address N0 0 1 0 1 Operation Power down Power up (with SM1=1 normal operation) Divide 3 The programming data is structured as a 24 bit long serial data word; the word includes 4 address bits (dedicated 1 0 1 1) for chip select. Data bits are shifted in on the leading edge of the clock, with the least significant bit (LSB) first and the most significant bit (MSB) last. Table 2 shows data word format, the 15th and last 5 bits are not used. Figure 8 shows the chip timing diagram. A2 1 Operation Power down Power up (STANDBY) Sleep Mode 2 Programming Operation A1 0 Operation Disabled Enabled Sleep Mode 1 The SA900 generates three buffered XO outputs used for external reference signals. The XO feeds three sets of programmable prescalers, the prescaler outputs are buffered to provide the CLK1, CLK2 and MCLK signals. The CLK1 signal is a selectable divide 3/1 (X=1 divide 3, X=0 divide 1), 50% duty cycle, of the XO reference signal. The CLK2 signal is a selectable divide 2/1 (Y=1 divide 2, Y=0 divide 1), 50% duty cycle, of the XO reference signal. The MCLK signal is a selectable divide 4/5/1 (CLKSET = VCC divide 4, CLKSET = VCC/2 divide 5, and CLKSET = 0V divide 1), 50% duty cycle, of the XO reference signal. MCLK is externally set by means of the tri-level CLKSET input to provide a default master system clock prior to programming the SA900. A0 1 Mode AMPS DUAL Divide 6 7 8 9 11 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 Table 3. Power Control Attenuation (dB) PC0 (0.6dB) PC1 (1.3dB) PC2 (2.5dB) PC3 (5.0dB) PC4 (10.0dB) PC5 (20.0dB) 0 0 0 0 0 0 0 0.6 1 0 0 0 0 0 1.3 0 1 0 0 0 0 1.9 1 1 0 0 0 0 2.5 0 0 1 0 0 0 3.2 1 0 1 0 0 0 3.8 0 1 1 0 0 0 4.4 1 1 1 0 0 0 5.0 0 0 0 1 0 0 5.7 1 0 0 1 0 0 6.3 0 1 0 1 0 0 23.3 1 0 1 0 0 1 1 1 1 1 1 1 • • • • • • 39.7 Value Component Designator DUAL Mode AMPS Mode R1 560Ω 560Ω R2 1kΩ 5.6kΩ C1 2.2nF 2.7µF C2 No Load .27µF C3 33pF 6.8nF RSET 15kΩ 75kΩ Typical Filter Network R2 PHSOUT VCTRL R1 C2 C3 C1 SR00640 Figure 5. PLL Loop Filter (AMPS MODULATION) C1 TANK_1 f L1 C3 VCC VCO + VR1 VCTRL C1 = C2 = 33pF [ 120MHz C3 = 12pF L1 = 82nH 1 2 ǸL1CȀ CȀ + C3 ) C2 VR1 TOKO KV1470 ǒC11 ) 1 1 ) C2 CVRI Ǔ *1 TANK_2 SR00641 Figure 6. VCO Tank Configuration 1997 Sept 16 12 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 XTAL_1 C1 XO CVAR XTAL_2 C2 SR00642 Figure 7. Crystal Oscillator Configuration TXEN TRANSMIT ENABLED LSB DATA MSB CLOCK T1 T2 T4 T3 STROBE SYN_EN SYNTHESIZER ENABLED 1 1 T1 T2 T3 , T4 3CLOCK 3CLOCK SR00643 Figure 8. Chip Timing Diagram VCC VCC 100pF 100pF 1nF 1nF L3 L1 L2 C1 1000pF OR 34 SA900 34 SA900 TYPICAL VALUES TYPICAL VALUES 50Ω L1 = 39nH L2 = 22nH 50Ω L3 = 12nH C1 = 1.5pF SR00644 Figure 9. DUALTX Output Matching 1997 Sept 16 13 1997 Sept 16 C269 33pF JMP JMP PHS-OUT P1-14 JP5 VCO-TUNE P1-15 JP4 J8 LO2PS1 14 Figure 10. SA900 Application Circuit J2 XO-REF T1-1 KK81 J18 VCO-REF C265 NL R333 1k R258 1k J1 TXLO2 R264 1k P1-1,2,3 GND Vcc R266 560 D1 NL R268 R260 51 R284 NL R352 100 C371 100pF C370 100pF C263 .01uF L252 100nH 5.6pF 1 C249 100pF C247 100pF C246 4.7uF C253 + C267 220pF R274 0 C255 33pF 2 C254 33pF ZO=50 KV1470 1 W3 P1-4,5,6,11,12,13 J7 LO2PS2 1 W1 C283 NL W2 2 2 1 2 3 4 5 6 7 8 9 10 11 12 NL R279 C243 100pF P2 CLK1 R293 NL NL C299 C292 NL C289 NL P3 CLK1 L290 NL 36 35 34 33 32 31 30 29 28 27 26 25 C294 NL R297 NL L296 NL C295 NL Vcc GND DUALTX GND Vcc AMPSTX GND Vcc GND Vcc Vcc GND P4 MCLK C288 .010uF 1 11 11 11 22 22 2 3 45 67 89 01 23 4 C S X L CT T C C MK D L R T A V L GL GC S A OOX L c KNK NL ET CBE 1 c 1 D2 DKT AKEN V L L GV I I QQGV G c OON c 1 2 1 2 N c N c 2 1 Dc Dc D 4 44 44 44 44 33 3 8 76 54 32 10 98 7 C287 .010uF GND TXLO2 TXLO1 GND Vcc TANK1 TANK2 Vcc PHS OUT IPEAK GND XTAL1 U1 SA900BE C314 100pF C313 100pF C245 .010uF 2 1 JP3 JMP JP2 JMP JP1 JMP P1-10 TXENABLE P1-9 STROBE P1-8 CLOCK P1-7 DATA C242 100pF W5 C301 100pF C305 100pF ZO=50 J4 Q1 C300 .010uF 1 L372 22nH L304 39nH C241 100PF C312 100pF J3 Q2 J5 I2 2 R350 100k R349 100k J10 AMPSTXRF ZO=50 W4 C306 .010uF J6 I1 J9 DIGTXRF I/Q transmit modulator C282 NL L280 NL C281 .010uF R262 15k ZO=50 ZO=50 Philips Semiconductors Preliminary specification SA900 NOTE: VCO-REF circuit is optional L372 is C307 on the PCB C246 combines C240 and C244 on the PCB SR00645 1997 Sept 16 Figure 11. SA900 Test Circuit 15 XO-REF PHASE OUT T1-1 KK81 TANK–1 TXLO2 W3 2 + R260 51 1K R300 1K C371 100pF C370 100pF ZO=50 C280 1000pF 1 GND Vcc R301 C263 .01uF R262 24K C249 100pF C247 270pF C246 1000pF LO_1 2 ZO=50 LO_2 2 C314 270pF R304 4.7K C402 7pF C401 7pF R305 4.7K S C X L CT T C C MKDL R T A V L G L G C SA OOX L c K N K N L ET CB E 1 c 1 D 2 D KTAKEN 1 11 11 11 22 22 2 3 45 67 89 01 23 4 SA900 V L L GV I I QQGV G c OON c 1 2 1 2 N c N c 2 1 Dc Dc D 4 44 44 44 44 33 3 8 76 54 32 10 98 7 C400 7pF R303 4.7K GND TXLO2 TXLO1 GND Vcc TANK1 TANK2 Vcc PHS OUT IPEAK GND XTAL1 CLOCK2 CLOCK1 C243 100pF 1 2 3 4 5 6 7 8 9 10 11 12 1 C315 270pF ZO=50 1 36 35 34 33 32 31 30 29 28 27 26 25 MCLK Vcc GND DUALTX GND Vcc AMPSTX GND Vcc GND Vcc Vcc GND Q1 C305 100pF TXENABLE 1 1 C245 .010uF C312 100pF C301 100pF C300 .010uF L372 22nH L304 39nH C241 100PF STROBE CLOCK DATA CLKSET C242 100pF Q2 I2 ZO=50 ZO=50 C306 .010uF I1 2 2 AMPSTX DIGTXRF Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 SR00646 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 PERFORMANCE CHARACTERISTICS –16.00 3.50 3.00 –17.00 POWER (dBm) POWER (dBm) 4.00 VCC = 3.9V VCC = 4.0V VCC = 4.5V –16.50 –17.50 –18.00 2.50 2.00 1.50 T = +85°C T = +27°C T = –45°C 1.00 0.50 –18.50 –19.00 900 0.00 –0.50 970 –1.00 1040 820 FREQUENCY (MHz) LO Buffer vs. Frequency (27°C, TXLO = –10dBm) VCC = 3.9V VCC = 4.0V VCC = 4.5V 2.80 2.60 2.80 2.40 VCC = 4.5V VCC = 3.9V VCC = 4.0V 2.20 2.00 POWER (dBm) POWER (dBm) 860 AMPTX vs. Frequency (VCC = 4.0V, TXLO = –10dBm) 3.00 1.80 1.60 1.40 1.20 1.00 820 836 FREQUENCY (MHz) 2.60 2.40 2.20 860 AMPTX vs. Frequency (27°C, TXLO = –10dBm) 2.00 820 3.50 836 FREQUENCY (MHz) 850 DUALTX vs. Frequency (TEMP 27°C, TXLO = –10dBm) 3.00 2.50 2.00 72 VCC = –40°C VCC = 27°C VCC = 85°C 1.50 1.00 0.50 0.00 820 836 850 FREQUENCY (MHz) CURRENT (AMPERES) POWER (dBm) 836 FREQUENCY (MHz) DUALTX vs. Frequency (VCC = 4.0V, TXLO = –10dBm) 70 68 66 64 VCC = 4.5V VCC = 4.0V VCC = 3.9V 62 –16.00 T = +85°C T = +27°C T = –45°C POWER (dBm) –16.50 60 –40 27 –17.00 TEMPERATURE (°C) –17.50 DUAL ICC vs. Temperature 85 –18.00 –18.50 –19.00 –19.50 –20.00 900 970 1040 FREQUENCY (MHz) LO Buffer vs. Frequency (VCC = 4.0V, TXLO = –10dBm) SR00647 Figure 12. Performance Characteristics 1997 Sept 16 16 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 PERFORMANCE CHARACTERISTICS –44.50 VCC = –40°C VCC = 85°C VCC = 27°C SUPPRESSION (dBc) –44.00 –44.50 –45.00 –45.50 –46.00 SUPPRESSION (dBc) –43.00 –43.50 –45.50 –46.00 –46.50 –47.00 –46.50 –47.00 –47.50 820 –47.50 820 836 –34.00 –32 –33 VCC = –85°C VCC = –40°C VCC = 27°C –38.00 VCC = 3.9V VCC = 4.0V VCC = 4.5V –34 –35 –36 dBc –40.00 –37 –42.00 –38 –39 –44.00 –40 –46.00 –41 –42 –40 –48.00 820 836 850 85 27 TEMPERATURE (°C) FREQUENCY (MHz) DUALTX 3rd Order Products vs Temperature (TXLO = –10dBm, f = 836MHz, 0dB VGA I/Q Inphase) DUALTX Sideband Suppression vs Frequency (VCC = 4.0V, TXLO = –10dBm Single Sideband Mode, With Respect to Lower Sideband) –30.00 –30.00 VCC = 3.9V VCC = 4.0V VCC = 4.5V T = +85°C T = +27°C T = –45°C –35.00 ATTENUATION (dB) –35.00 ATTENUATION (dB) 850 DUALTX Sideband Suppression vs. Frequency (Temperature = 27°C, TXLO = –10dBm Single Sideband Mode, With Respect to Lower Sideband) FREQUENCY (MHz) –36.00 836 FREQUENCY (MHz) 850 DUALTX Carrier Suppression vs. Frequency (VCC = 4.0, TXLO = –10dBm Single Sideband Mode, With Respect to Lower Sideband) SUPPRESSION (dBc) VCC = 4.5V VCC = 4.0V VCC = 3.9V –45.00 –40.00 –45.00 –40.00 –45.00 –50.00 –55.00 –50.00 –60.00 –55.00 0 2 5 7 10 13 15 18 20 23 25 26 29 33 37 40 44 48 51 55 59 63 0 2 5 7 10 13 15 18 20 23 25 26 29 33 37 40 44 48 51 55 59 63 VGA 6-BIT WORD VALUE (LSBs) VGA 6-BIT WORD VALUE (LSBs) DUALTX Carrier Suppression vs VGA Range (VCC = 4.0V, f = 836MHz, TXLO = –10dBm) DUALTX Carrier Suppression vs VGA Range (27°C, f = 836MHz, TXLO = –10dBm) SR00648 Figure 13. Performance Characteristics 1997 Sept 16 17 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 PERFORMANCE CHARACTERISTICS 0 –5 ATTENUATION (dB) –10 –15 27°C –20 –40°C –25 85°C –30 –35 –40 –45 0 4 2 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 46 48 50 52 54 56 58 60 62 VGA 6-BIT WORD VALUE (LSBs) DUALTX VGA Attenuation Profile vs. Temperature (VCC = 4.0V, F = 836MHz) 0 –5 –10 3.9V ATTENUATION (dB) –15 4.0V –20 4.6V –25 –30 –35 –40 –45 0 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 46 48 50 52 54 56 58 60 62 VGA 6-BIT WORD VALUE (LSBs) DUALTX VGA Attenuation Profile vs. VCC (T = 27°C, F = 836MHz) SR00649 Figure 14. Performance Characteristics 1997 Sept 16 18 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 LQFP48: plastic low profile quad flat package; 48 leads; body 7 x 7 x 1.4 mm 1997 Sept 16 19 SOT313-2 Philips Semiconductors Preliminary specification I/Q transmit modulator SA900 DEFINITIONS Data Sheet Identification Product Status Definition Objective Specification Formative or in Design This data sheet contains the design target or goal specifications for product development. Specifications may change in any manner without notice. Preliminary Specification Preproduction Product This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product. Product Specification Full Production This data sheet contains Final Specifications. Philips Semiconductors reserves the right to make changes at any time without notice, in order to improve design and supply the best possible product. Philips Semiconductors and Philips Electronics North America Corporation reserve the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. LIFE SUPPORT APPLICATIONS Philips Semiconductors and Philips Electronics North America Corporation Products are not designed for use in life support appliances, devices, or systems where malfunction of a Philips Semiconductors and Philips Electronics North America Corporation Product can reasonably be expected to result in a personal injury. Philips Semiconductors and Philips Electronics North America Corporation customers using or selling Philips Semiconductors and Philips Electronics North America Corporation Products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors and Philips Electronics North America Corporation for any damages resulting from such improper use or sale. Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 Philips Semiconductors and Philips Electronics North America Corporation register eligible circuits under the Semiconductor Chip Protection Act. Copyright Philips Electronics North America Corporation 1996 All rights reserved. Printed in U.S.A. 1997 Sept 16 20