FinFET domino logic with independent gate keepers

advertisement

ARTICLE IN PRESS

Microelectronics Journal ] (]]]]) ]]]–]]]

Contents lists available at ScienceDirect

Microelectronics Journal

journal homepage: www.elsevier.com/locate/mejo

FinFET domino logic with independent gate keepers

Sherif A. Tawfik a,, Volkan Kursun b

a

b

Department of Electrical and Computer Engineering, University of Wisconsin-Madison, Madison, WI 53706-1691, United States

Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Clear Water Bay, Kowloon, Hong Kong

a r t i c l e in fo

abstract

Article history:

Received 12 April 2008

Received in revised form

7 December 2008

Accepted 29 January 2009

Scaling of single-gate MOSFET faces great challenges in the nanometer regime due to the severe shortchannel effects that cause an exponential increase in the sub-threshold and gate-oxide leakage currents.

Double-gate FinFET technology mitigates these limitations by the excellent control over a thin silicon

body by two electrically coupled gates. In this paper a variable threshold voltage keeper circuit

technique using independent-gate FinFET technology is proposed for simultaneous power reduction

and speed enhancement in domino logic circuits. The threshold voltage of a keeper transistor is

dynamically modified during circuit operation to reduce contention current without sacrificing noise

immunity. The optimum independent-gate keeper gate bias conditions are identified for achieving

maximum savings in delay and power while maintaining identical noise immunity as compared to the

standard tied-gate FinFET domino circuits. With the variable threshold voltage double-gate keeper

circuit technique the evaluation speed is enhanced by up to 49% and the power consumption is reduced

by up to 46% as compared to the standard domino logic circuits designed for similar noise margin in a

32 nm FinFET technology.

& 2009 Elsevier Ltd. All rights reserved.

Keywords:

Low-power

High-speed

FinFET

Dynamic threshold voltage

Independent-gate bias

1. Introduction

Scaling is the primary thrust behind the advancement of CMOS

technology. The increased leakage currents and the enhanced

device sensitivity to process parameter fluctuations have become

the primary barriers against further CMOS technology scaling into

the sub-45 nm regime. The double-gate FinFET offers distinct

advantages for simultaneously suppressing the sub-threshold and

gate dielectric leakage currents as compared to the traditional

single-gate MOSFETs [2,18–20]. The two electrically coupled gates

and the thin silicon body suppress the short-channel effects of a

double-gate FinFET, thereby reducing the sub-threshold leakage

current [2]. The suppressed short-channel effects and the

enhanced gate control over the channel (lower sub-threshold

swing) permit the use of a thicker gate oxide in a double-gate

FinFET as compared to a conventional single-gate transistor. The

gate-oxide leakage current of a double-gate transistor is thereby

significantly reduced. The thin body of a double-gate device is

typically undoped or lightly doped. The carrier mobility is

therefore enhanced and the device variations due to doping

fluctuations are reduced in a double-gate MOSFET as compared to

a single-gate bulk transistor. Successful fabrication of tied-gate

and independent-gate FinFETs has been demonstrated [3–5].

Corresponding author.

E-mail address: tawfik@wisc.edu (S.A. Tawfik).

Domino logic circuit techniques are extensively applied in

high-performance microprocessors due to the superior speed and

area characteristics of dynamic CMOS circuits as compared to

static CMOS circuits [1]. High-speed operation of domino logic

circuits is primarily due to the lower noise margins of domino

circuits as compared to static gates. As on-chip noise becomes

more severe with technology scaling and increasing operating

frequencies, error-free operation of domino logic circuits has

become a major challenge [6,9].

In a standard domino logic gate, a feedback keeper is employed

to maintain the state of the dynamic node against coupling

noise, charge sharing, and sub-threshold leakage current. The

keeper transistor is fully turned on at the beginning of the

evaluation phase. Provided that the necessary input combination

to discharge the dynamic node is applied, the keeper and the

pull-down network transistors compete to determine the logical

state of the dynamic node. This contention between the keeper

and the pull-down network transistors degrades the circuit speed

while increasing the power consumption [1,6]. The keeper

transistor is typically sized smaller than the pull-down network

transistors in order to minimize the delay and power penalty

caused by the keeper contention current. A small keeper, however,

cannot provide the necessary noise immunity for reliable

operation in an increasingly noisy and noise sensitive on-chip

environment in the scaled CMOS technologies [6,7,9,12,13]. There

is, therefore, a tradeoff between reliability and high-speed/

energy-efficient operation in domino logic circuits. New dynamic

circuit techniques which can suppress the keeper contention

0026-2692/$ - see front matter & 2009 Elsevier Ltd. All rights reserved.

doi:10.1016/j.mejo.2009.01.011

Please cite this article as: S.A. Tawfik, V. Kursun, FinFET domino logic with independent gate keepers, Microelectron. J (2009),

doi:10.1016/j.mejo.2009.01.011

ARTICLE IN PRESS

2

S.A. Tawfik, V. Kursun / Microelectronics Journal ] (]]]]) ]]]–]]]

current while maintaining a high noise immunity are highly

desirable.

In [6], a variable-threshold-voltage keeper is proposed for

enhancing the evaluation speed and lowering the power consumption of domino logic circuits in a standard single-gate bulk

CMOS technology. The threshold voltage of a keeper transistor is

dynamically adjusted by body-bias with this technique. The high

capacitance of an n-well, however, may prohibit the alteration of

the body voltage of the keeper transistor every clock cycle.

Furthermore, dual supply voltages are required for providing the

necessary body-bias voltages with the technique described in [6].

An alternative multi-phase keeper technique employing two

keeper transistors is presented in [7,12,13] to reduce the contention current in a domino circuit. With this technique, one of the

keeper transistors operates unconditionally similar to a standard

domino circuit. The other keeper transistor is conditionally turned

on if the dynamic node is not discharged during the evaluation

phase. The use of multiple keepers increases the circuit area.

Furthermore, the unconditional keeper, when implemented even

with a minimum-sized tied-gate FinFET, produces significant

contention current. The power reduction and the speed enhancement provided with this conditional keeper technique are therefore limited, particularly in a standard tied-gate FinFET

technology.

In this paper, a new variable threshold voltage keeper

technique based on an independent-gate FinFET (IG-FinFET)

technology is proposed for simultaneous enhancement of the

evaluation speed and reduction of the power consumption

without sacrificing the noise immunity in FinFET domino logic

circuits. A single tunable-strength keeper transistor is utilized

with the proposed technique, unlike the technique presented in

[7,12,13] which requires multiple keeper transistors. Furthermore,

the threshold voltage of the keeper transistor is adjusted with a

simple independent-gate-bias mechanism utilizing only the

standard voltage references (VGND and VDD) that are readily

available in the system, unlike the technique presented in [6]

which requires multiple power supplies and periodic switching of

the bias voltage of the high capacitance n-wells.

The paper is organized as follows. The FinFET operation is

described in Section 2. The standard tied-gate and the proposed

independent-gate FinFET domino logic circuits are presented in

Section 3. Power, delay, and noise immunity characteristics of the

standard and the proposed FinFET domino circuits are compared

in Section 4. Finally, conclusions are offered in Section 5.

2. FinFET technology

In this section the device architectures for tied-gate and

independent-gate FinFETs are presented. N-type and P-type

FinFETs with a 32 nm channel length are designed and characterized using MEDICI, a physics-based device simulator [8]. The

effect of different gate bias conditions on the I–V characteristics of

independent-gate FinFETs is provided. The 3D architectures of the

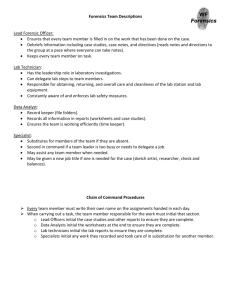

tied-gate and the independent-gate FinFETs are shown in Fig. 1.

A top view of a FinFET indicating the critical physical dimensions

is shown in Fig. 1c. The technology parameters of the FinFETs

considered in this paper are listed in Table 1 [14–16].

The width of a FinFET is quantized due to the vertical gate

structure. The fin height determines the minimum transistor

width (Wmin). With the two gates of a single-fin FET tied together,

Wmin is

W min ¼ 2 Hfin þ t si ,

(1)

where Hfin is the height of the fin and tsi is the thickness of the

silicon body as shown in Fig. 1. The fin thickness is typically much

smaller than the fin height in order to effectively suppress the

short-channel effects and to enhance the area efficiency in a

Table 1

Device technology parameters.

Parameter

Value

Channel length (L)

Effective channel length (Leff)

Fin thickness (tsi)

Fin height (Hfin)

Oxide thickness (tox)

Channel doping

Source/drain doping (N-type and P-type FinFETs)

Gates work function (N-type FinFET)

Gates work function (P-type FinFET)

Supply voltage (VDD)

32 nm

25.6 nm

8 nm

32 nm

1.6 nm

1015 cm3

2 1020 cm3

4.5 eV

4.9 eV

0.8 V

Back Gate

Gate

tsi

Source

Drain

Source

Drain

Hfin

L

Drain

Front Gate

Front Gate

Insulator

Source

t si = 8nm

t ox = 1.6nm

Back Gate

Gate

25.6nm

L = 32nm

Oxide

Heavily doped Si

Lightly doped Si

Fig. 1. The device architectures of FinFETs. (a) 3D structure of a one-fin tied-gate FinFET. (b) 3D structure of a one-fin independent-gate FinFET. (c) Cross-sectional top view

of a FinFET with a drawn channel length of 32 nm.

Please cite this article as: S.A. Tawfik, V. Kursun, FinFET domino logic with independent gate keepers, Microelectron. J (2009),

doi:10.1016/j.mejo.2009.01.011

ARTICLE IN PRESS

S.A. Tawfik, V. Kursun / Microelectronics Journal ] (]]]]) ]]]–]]]

3

double-gate FinFET [21]. Hfin is therefore the dominant component

of the transistor width. Since Hfin and tsi are fixed in a FinFET

technology, multiple parallel fins are utilized to increase the width

of a FinFET as shown in Fig. 2. The total physical transistor width

(Wtotal) of a tied-gate FinFET with n parallel fins is

speed and reduce the power consumption without sacrificing the

noise immunity in FinFET domino logic circuits.

W total ¼ n W min ¼ n ð2 Hfin þ t si Þ.

Performance critical paths in high-performance integrated

circuits are often implemented with domino logic circuits

[1,6,7,9–13]. Although domino logic circuits are preferable in

high-speed applications, the reliability of domino circuits is

seriously degraded with technology scaling. The operating

principles of domino logic circuits are reviewed in this section.

The noise immunity vs. the speed and power tradeoffs in standard

domino logic circuits are discussed in Section 3.1. The new

variable threshold voltage independent-gate FinFET keeper technique for simultaneously enhancing the evaluation speed and

lowering the power consumption in FinFET domino logic circuits

is described in Section 3.2.

(2)

The two vertical gates of a single-fin FET can be separated by an

oxide on top of the silicon fin, thereby forming an independentgate FinFET as shown in Fig. 1b. An independent-gate FinFET

provides two different active modes of operation with significantly different current characteristics determined by the independent bias conditions of the two gates as shown in Fig. 3. In the

dual-gate-mode, the two gates are biased with the same signal to

control the formation of a channel. Alternatively, in the singlegate-mode, one gate is biased with the input signal to induce

channel inversion while the other gate is disabled (disabled gate:

biased with VGND in an N-type FinFET and with VDD in a P-type

FinFET). The two gates are strongly coupled in the dualgate-mode, thereby lowering the threshold voltage |Vth| as

compared to the single-gate-mode. For example, the maximum

drain current produced in the dual-gate-mode is 2.77 times higher

as compared to the single-gate-mode in a minimum-sized

P-channel FinFET as shown in Fig. 3. The switched gate

capacitance of the FinFET is also halved in the single-gate-mode.

The unique Vth modulation aspect of IG-FinFETs through selective

gate bias is exploited in this paper to simultaneously enhance the

at

e

tsi

Drain

G

Source

Hfin

L

Fig. 2. Three-fin FET. Wtotal ¼ 3 (2 Hfin+tsi).

Single-Gate-Mode

Dual-Gate-Mode

1.E-02

1.E-04

1.E-05

ISD (A/µm)

1.E-03

2.77X

1.E-06

Vth-high = -0.46V

-0.8

-0.6

3. Domino logic circuits

3.1. Standard tied-gate FinFET domino logic circuits

A standard footless FinFET domino gate is shown in Fig. 4.

Domino circuits behave in the following manner. When the clock

signal is low, the domino logic circuit is in the precharge phase.

The inputs must be low in this phase to avoid a short-circuit

current in footless domino logic circuits [1,6]. This requirement is

satisfied by intentionally delaying the clock signal from the

preceding domino stages in a multi-stage domino logic circuit.

During the precharge phase, the dynamic node is charged to VDD

by the precharge transistor. The output transitions low, turning on

the keeper transistor. When the clock transitions high, the circuit

enters the evaluation phase. In this phase, provided that the

necessary input combination to discharge the dynamic node is

applied, the circuit evaluates and the dynamic node is discharged

to ground. Alternatively, if the circuit does not evaluate in the

evaluation phase, the high state of the dynamic node is preserved

against coupling noise, charge sharing, and sub-threshold leakage

current by the keeper transistor until the precharge transistor is

turned on at the beginning of the subsequent precharge phase.

The keeper transistor is fully turned on as the output goes low

during the precharge phase. When the clock signal transitions

high, the precharge transistor turns off and the keeper transistor

provides the only conductive path between the dynamic node and

VDD, preserving the logical state of the dynamic node in the

evaluation phase. Provided that the necessary input combination

to discharge the dynamic node is applied during the evaluation

phase, the keeper transistor opposes the evaluation of the inputs,

thereby degrading the speed and increasing the power consumption of a domino logic circuit. The current provided by the keeper

transistor to charge the dynamic node while the pull-down

network transistors are attempting to discharge the dynamic node

is called the contention current [1,6].

Precharge Transistor

VDD

VDD

Standard Keeper

CLK

Vth-low = -0.27V

-0.4

VGS (V)

-0.2

1.E-07

0.0

Fig. 3. Drain current characteristics of a single-fin P-type IG-FinFET. The source-todrain voltage is 0.8 V. T ¼ 110 1C. Ioff ¼ 216 nA/mm. Ion (single-gate-mode) ¼ 0.422

mA/mm. Ion (dual-gate-mode) ¼ 1.17 mA/mm. The threshold voltage is the gate-tosource voltage at which the drain current per fin height is 104 A/mm for

|VDS| ¼ VDD.

Output

.

Inputs ..

Pull-down

Network

Dynamic Node

Fig. 4. A standard footless domino circuit in a tied-gate FinFET technology.

Please cite this article as: S.A. Tawfik, V. Kursun, FinFET domino logic with independent gate keepers, Microelectron. J (2009),

doi:10.1016/j.mejo.2009.01.011

ARTICLE IN PRESS

4

S.A. Tawfik, V. Kursun / Microelectronics Journal ] (]]]]) ]]]–]]]

The effect of the keeper transistor on the noise immunity and

the evaluation delay of a domino logic circuit is evaluated next.

The low noise margin (NML) is the noise immunity metric used in

this paper. The NML is

NML ¼ V IL V OL ,

(3)

25

250

NML

20

200

15

Delay

150

Power

10

100

5

NML (mV)

Delay (ps) and Power (µW)

where VIL is the voltage amplitude of the DC noise signal applied

to the inputs (from the beginning to the end of the evaluation

phase) that produces a signal with the same amplitude at the

output of a domino logic circuit [10–13]. VOL is the output low

voltage.

Simulation results for a 16-input footless domino OR gate are

shown in Fig. 5 for various keeper sizes. The worst-case evaluation

speed is observed when a single input signal transitions to VDD

while the other gate inputs are maintained at VGND. The NML is

measured for a worst-case noise scenario assuming all the inputs

of the OR gate are simultaneously excited by the same noise

signal. As shown in Fig. 5, the NML is enhanced by 70% when KPR

(ratio of keeper size to the size of one of the pull-down network

transistors) is increased from 0.25 to 1.5. The penalty for this

noise immunity enhancement with keeper sizing, however, is the

degradation of the evaluation speed and the increase in the power

consumption due to the higher contention current produced by a

larger keeper transistor. The evaluation delay and the power

consumption are increased by 3.3 and 3 , respectively, when

KPR is increased from 0.25 to 1.5. There is, therefore, a tradeoff

50

0

0

0.25

between high noise immunity and high-speed/low-power operation of domino logic gates. New dynamic circuit techniques which

can suppress the keeper contention current while maintaining a

high noise immunity are, therefore, highly desirable.

0.5

1

1.5

KPR

Fig. 5. Evaluation delay, power consumption, and NML of a standard 16-input

domino OR gate in a 32 nm tied-gate FinFET technology. KPR: ratio of keeper size

to the size of one of the pull-down network transistors. Frequency ¼ 4 GHz.

T ¼ 110 1C.

3.2. FinFET domino with variable-threshold-voltage keeper

A variable threshold voltage keeper circuit technique based on

an independent-gate FinFET technology is presented in this

section for simultaneous delay and power reduction without

sacrificing noise immunity in domino logic circuits. The schematic

of the proposed technique is shown in Fig. 6.

The operation of the proposed domino logic circuit is as

follows. In the precharge phase, the clock signal is low. The pulldown network is cut-off. The dynamic and output node are

charged and discharged to VDD and VGND, respectively. The keeper

control signal (N1) transitions to VDD, disabling one of the gates of

the keeper transistor. The other gate of the keeper is activated by

the discharged output node. The keeper operates in the singlegate-mode with a high threshold voltage (high-Vth).

The evaluation phase begins when the clock signal transitions

to high. The precharge device is cut-off. Provided that the pulldown network is activated by asserting the inputs, the dynamic

node is discharged to VGND. Since the keeper threshold voltage is

increased with single-gate-bias, the contention current produced

by the keeper is significantly reduced. The evaluation speed is

enhanced and the short-circuit power consumption is reduced

due to the lower keeper contention current. After the output node

is charged to VDD, the keeper is fully cut-off. Alternatively,

provided that the pull-down network is not activated for certain

input combinations, the dynamic node is maintained at VDD in the

evaluation phase. After some delay, the keeper control signal (N1)

transitions to VGND. Both gates of the keeper are fully activated for

strongly maintaining the high voltage state of the dynamic node.

The keeper transistor operates in the dual-gate-mode with a low

threshold voltage (low-Vth), thereby providing similar noise

immunity as compared to a standard tied-gate FinFET domino

circuit with the same size keeper transistor.

The non-inverting delay element used with the proposed

technique is composed of cascaded transmission gates as shown

in Fig. 7. The number of stages of the delay circuit is determined

such that the combined delay of the delay element and the NAND

gate (NAND1) is equal to the evaluation delay of the domino gate.

Non-inverting Delay

VDD

VDD

Independent-Gate

FinFET Keeper

N1

CLK

NAND1

Output

Dynamic Node

Inputs

.

.

.

Pull-down

Network

Fig. 6. Schematic of the proposed variable threshold voltage keeper independent-gate FinFET domino logic circuit technique.

Please cite this article as: S.A. Tawfik, V. Kursun, FinFET domino logic with independent gate keepers, Microelectron. J (2009),

doi:10.1016/j.mejo.2009.01.011

ARTICLE IN PRESS

S.A. Tawfik, V. Kursun / Microelectronics Journal ] (]]]]) ]]]–]]]

Other implementations such as cascaded inverters are also

possible for the delay element. The use of cascaded transmission

gates has the advantage of reducing the power consumption as

VDD

VDD

…

Vin

Vout

Fig. 7. The delay element. The required number of stages is determined by the

evaluation delay of a specific domino gate.

compared to using cascaded inverters due to the reduction of the

switched gate capacitances. Furthermore, the necessary delay is

typically small since the domino circuits evaluate the inputs with

high-speed. Using a small number of cascaded transmission gates

therefore does not degrade the slew rate of the delayed signal. The

signal waveforms representing the operation of a domino logic

circuit with a dynamically controlled keeper in a double-gate

FinFET technology are shown in Fig. 8.

4. Simulation results

The standard tied-gate and the proposed independent-gate

FinFET domino circuit techniques are compared in this section for

the evaluation delay, the power consumption, and the noise

immunity in a 32 nm FinFET technology using Taurus-Medici [8].

Pull-down network

is activated

Pull-down

network

is not activated

Pre-charge Phase

5

Evaluation Phase

Pre-charge Phase

Evaluation Phase

Pre-charge Phase

Clock

Dynamic Node

tkeeper-delay

Dynamic Keeper

Control (N1)

Output Node

Fig. 8. The signal waveforms of the proposed domino logic circuit technique with a dynamically tunable threshold voltage keeper in a double-gate FinFET technology. The

tkeeper-delay is determined by the keeper gate delay control circuitry composed of the delay element and the NAND gate.

25

Standard Tied-Gate

Proposed Independent-Gate

-55%

20

Delay (ps)

-54%

15

10

5

0

0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5

2-input AND

4-input OR

16-input OR

8-bit

Multiplexer

32-bit

Multiplexer

KPR

Fig. 9. Comparison of the evaluation delay of the standard tied-gate and the proposed variable threshold voltage keeper independent-gate FinFET techniques for different

domino circuits and KPR.

Please cite this article as: S.A. Tawfik, V. Kursun, FinFET domino logic with independent gate keepers, Microelectron. J (2009),

doi:10.1016/j.mejo.2009.01.011

ARTICLE IN PRESS

6

S.A. Tawfik, V. Kursun / Microelectronics Journal ] (]]]]) ]]]–]]]

The clock frequency is 4 GHz and the temperature is 110 1C for all

the simulations. 110 1C is a typical hot-spot temperature in the

state-of-the-art high-performance microprocessors [17]. A load

capacitance of 0.2 fF is assumed at the output of each circuit. The

test circuits evaluated in this section include 2-input AND gate,

4-input OR gate, 16-input OR gate, 8-bit multiplexer, and 32-bit

multiplexer. The worst-case evaluation delay and the power

consumption are measured when one input signal is driving one

of the parallel transistors (or transistor stacks) of the pull-down

network while the other inputs are connected to VGND. The NML is

measured for a worst-case noise scenario with a noise signal

coupling to all of the inputs. The evaluation delay is measured

from the time the input signal rises to VDD/2 (from 0 V) until the

output rises to VDD/2. The simulation results of the standard tiedgate and the proposed independent-gate FinFET domino circuits

are provided in Section 4.1. The different bias options of a multifin keeper transistor with the proposed independent-gate bias

technique are presented in Section 4.2.

4.1. Comparison of the FinFET domino circuits

The standard tied-gate and the proposed independent-gate

FinFET domino circuits are compared in this section for different

keeper sizes. Note that in a multi-fin independent-gate FET there

are multiple gate-bias options. The number of gates of the

25

Standard Tied-Gate

Proposed Independent-Gate

Power Consumption (µW)

20

-50%

15

-57%

10

5

0 0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5

2-input AND

16-input OR

4-input OR

8-bit

Multiplexer

32-bit

Multiplexer

KPR

Fig. 10. Comparison of the power consumption of the standard tied-gate and the proposed variable threshold voltage keeper independent-gate FinFET techniques for

different domino circuits and KPR.

750

Standard Tied-Gate

NML (mV)

600

Proposed Independent-Gate

-16%

450

-10%

300

150

0

0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5

2-input AND

4-input OR

16-input OR

KPR

8-bit

Multiplexer

32-bit

Multiplexer

Fig. 11. Comparison of the NML of the standard tied-gate and the proposed variable threshold voltage keeper independent-gate FinFET techniques for different domino

circuits and KPR.

Please cite this article as: S.A. Tawfik, V. Kursun, FinFET domino logic with independent gate keepers, Microelectron. J (2009),

doi:10.1016/j.mejo.2009.01.011

ARTICLE IN PRESS

S.A. Tawfik, V. Kursun / Microelectronics Journal ] (]]]]) ]]]–]]]

independent-gate keeper transistors considered in this section is

equally divided in two for independent-gate bias. One half of the

keeper gates are driven by the output inverter. Alternatively, the

other half of the keeper gates is driven with some delay by NAND1

with the proposed technique.

The simulation results are shown in Figs. 9–11 for the

evaluation delay, the power consumption, and the NML, respectively. The evaluation delay is significantly reduced by up to 55%

(16-input OR with KPR ¼ 1.5) with the proposed dynamic threshold voltage keeper technique as compared to the standard domino

circuits, as shown in Fig. 9. Similarly, the power consumption is

significantly reduced by up to 57% (4-input OR with KPR ¼ 1.5)

with the proposed variable threshold voltage keeper technique as

compared to the standard domino circuits, as shown in Fig. 10. The

speed enhancement and the power reduction with the proposed technique are more pronounced as the contention current

increases with a larger keeper transistor. For the domino gates

with a wide pull-down network (such as the 16-input OR gate and

the multiplexers) the NML with the new variable threshold

voltage keeper technique is slightly degraded (o5%) as compared

to the standard tied-gate FinFET domino circuits, as shown in

Fig. 11. The NML of the 2-input AND gate is degraded by up to 16%

(KPR ¼ 1.5) with the proposed technique.

7

Lowest delay and power with

no degradation in NML

G1 = 5

G2 = 1

G1 = 6

G2 = 0

G1 = 4

G2 = 2

G1 = 1

G2 = 5

G1 = 2

G2 = 4

G1 = 3

G2 = 3

G1 = 0

G2 = 6

Fig. 13. Gate bias options of a three-fin independent-gate keeper FinFET. G1:

number of independent keeper gates driven by NAND1. G2: number of

independent keeper gates driven by the output.

4.2. Multi-fin keeper independent-gate bias options

0.45

0.40

|Vth (v)|

In this section different gate bias options of the multi-fin

keeper transistors with the proposed independent-gate biased

FinFET domino circuits are explored. A 16-bit domino OR gate

with KPR ¼ 0.75 is shown in Fig. 12. In this circuit the keeper

transistor has three fins. Each fin is controlled by two independent

gates. Seven configurations are examined in which the output

inverter drives different number of gates of the multi-fin keeper

transistor (G2 ¼ {0y6}). The other gates of the keeper transistor

are driven by the NAND1. The seven gate bias options for a 3-fin

keeper are illustrated in Fig. 13. The variation of the threshold

voltage of the 3-fin keeper transistor with G2 is shown in Fig. 14.

The simulations results for these different bias options are shown

in Fig. 15. The lowest power and delay are achieved with the first

bias option when all the gates of the keeper transistor are driven

by NAND1 (G1 ¼ 6 and G2 ¼ 0). The NML, however, is the lowest

for this bias option since the keeper is completely turned off at

the beginning of the evaluation phase. For G1 ¼ 6 and G2 ¼ 0 the

proposed technique becomes essentially an extension of the

technique presented in [8] to the FinFET domino logic circuits.

0.35

0.30

0.25

0.20

2

1

3

4

5

6

G2

Fig. 14. Variation of the keeper threshold voltage with G2. G1 is connected to VDD.

The threshold voltage is the gate-to-source voltage for which the drain current is

1 mA. VSD ¼ 0.8 V.

VDD

V DD

Independent-Gate

FinFET Keeper

N1

CLK

3fins

NAND1

1fin

Output

Dynamic Node

Vin0

…

4fins

Vin15

4fins

Fig. 12. A 16-input domino OR gate with KPR ¼ 0.75.

Please cite this article as: S.A. Tawfik, V. Kursun, FinFET domino logic with independent gate keepers, Microelectron. J (2009),

doi:10.1016/j.mejo.2009.01.011

ARTICLE IN PRESS

8

S.A. Tawfik, V. Kursun / Microelectronics Journal ] (]]]]) ]]]–]]]

Alternatively, when the output drives one gate of the keeper

transistor (G1 ¼ 5 and G2 ¼ 1), the NML is the same as a standard

tied-gate domino circuit with the same keeper size while the

power consumption and the evaluation delay are reduced by 20%

and 22%, respectively. Further increasing G2 does not enhance the

noise immunity. However, as G2 is increased beyond one, the

keeper contention current is enhanced due to the lower threshold

NML

182

9

179

8

Power

Delay

176

7

NML (mV)

Delay (ps), Power (µW)

10

173

6

5

170

0

1

2

3

G2

4

5

6

Fig. 15. Delay, power, and NML characteristics of a 16-input domino OR gate with

KPR ¼ 0.75. G2: number of independent keeper gates driven by the output. G2 ¼ 6

corresponds to the standard tied-gate FinFET domino circuit.

voltage of the keeper transistor. For G2 greater than one, therefore,

the delay and the power consumption savings are reduced with

no additional benefit in noise immunity for the circuit shown in

Fig. 12.

The domino test circuits presented in the previous section are

reevaluated in order to identify the optimum keeper gate bias

schemes with the proposed independent-gate FinFET technique to

minimize the evaluation delay and the power consumption while

maintaining identical noise immunity as compared to the

standard tied-gate FinFET circuits. The optimum biasing conditions for the different circuits with different KPR are listed in

Table 2. The optimum configurations with odd numbers for G1

and G2 (shown in bold in Table 2) can be achieved only with an

independent-gate FinFET technology. Alternatively, the optimum

configurations with even numbers for G1 and G2 (shown with

italicized bold numbers in Table 2) could be implemented either

with a single independent-gate FinFET keeper or with two

individual tied-gate FinFET keepers. The simulation results with

the optimum keeper gate bias conditions for different types

of domino circuits employing various keeper sizes are shown in

Figs. 16 and 17 for the evaluation delay and the power

consumption, respectively. The evaluation delay is significantly

reduced by up to 49% (16-input OR with KPR ¼ 1.5) with the

proposed dynamic threshold voltage keeper technique while

maintaining identical NML as compared to the standard domino

circuits, as shown in Fig. 16. Similarly, the power consumption is

significantly reduced by up to 46% (16-input OR with KPR ¼ 1.5)

Table 2

The independent-gate keeper optimum bias conditions for achieving minimum delay and power consumption with no degradation in NML.

KPR

0.25

0.5

1

1.5

Number of keeper fins

2-input AND

1

2

4

6

4-input OR

16-input OR

8-bit Multiplexer

32-bit Multiplexer

G1

G2

G1

G2

G1

G2

G1

G2

G1

G2

1

1

1

3

1

3

7

9

1

2

2

3

1

2

6

9

1

3

5

5

1

1

3

7

1

4

6

4

1

0

2

8

1

4

8

7

1

0

0

5

*

G1: number of independent keeper gates driven by NAND1. G2: number of independent keeper gates driven by the output.

25

Standard Tied-Gate

Proposed Independent-Gate

-49%

20

-33%

Delay (ps)

-32%

15

10

5

0

0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5

2-input AND

4-input OR

16-input OR

KPR

8-bit

Multiplexer

32-bit

Multiplexer

Fig. 16. Comparison of the evaluation delay of the standard tied-gate and the proposed variable threshold voltage keeper independent-gate FinFET techniques for different

domino circuits and various keeper sizes while maintaining identical NML.

Please cite this article as: S.A. Tawfik, V. Kursun, FinFET domino logic with independent gate keepers, Microelectron. J (2009),

doi:10.1016/j.mejo.2009.01.011

ARTICLE IN PRESS

S.A. Tawfik, V. Kursun / Microelectronics Journal ] (]]]]) ]]]–]]]

9

25

Standard Tied-Gate

Proposed Independent-Gate

-28%

Power Consumption (µW)

20

-46%

15

-33%

10

5

0

0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5 0.25 0.5 1 1.5

2-input AND

4-input OR

16-input OR

8-bit

Multiplexer

32-bit

Multiplexer

KPR

Fig. 17. Comparison of the power consumption of the standard tied-gate and the proposed variable threshold voltage keeper independent-gate FinFET techniques for

different domino circuits and various keeper sizes while maintaining identical NML.

with the proposed variable threshold voltage keeper technique as

compared to the standard domino circuits, as shown in Fig. 17.

5. Conclusions

A new high-speed and low-power domino logic circuit

technique based on an independent-gate FinFET technology is

presented in this paper. The proposed technique dynamically

changes the threshold voltage of the keeper transistor with a

specific delay after the beginning of each operational phase

(evaluation and precharge) of the domino circuit by independently biasing the multiple gates of the keeper transistor. The

keeper contention current is reduced by increasing the keeper

threshold voltage by operating the keeper in the single-gate-mode

at the beginning of the evaluation phase. Similarly, the degradation in noise immunity of the proposed technique as compared to

a standard tied-gate FinFET domino circuit is avoided by

dynamically and conditionally reducing the keeper threshold

voltage after a delay greater than the worst-case evaluation delay

of a domino logic circuit provided that the dynamic node is not

discharged. The new circuit technique is evaluated with different

logic gates for various keeper sizes. With the proposed technique,

the evaluation delay and the power consumption are simultaneously reduced by up to 49% and 46%, respectively, without

sacrificing the noise immunity as compared to the standard tiedgate FinFET domino logic circuits in a 32 nm FinFET technology.

References

[1] V. Kursun, E.G. Friedman, Multi-Voltage CMOS Circuit Design, Wiley, New

York, 2006, 242pp.

[2] E. Nowak, et al., Turning silicon on its edge, IEEE Circuits & Device Magazine

(2004) 20–31 (January/February).

[3] Y. Liu, et al., Cointegration of high-performance tied-gate three-terminal

FinFETs and variable threshold-voltage independent-gate four-terminal

FinFETs with asymmetric gate-oxide thicknesses, IEEE Electron Device Letters

28 (6) (2007) 517–519 (June).

[4] Y.X. Liu, et al., 4-terminal FinFETs with high threshold voltage controllability,

Proceedings of the IEEE Device Research Conference 1 (2004) 207–208 (June).

[5] J. Kedzierski, et al., Metal-gate FinFET and fully-depleted SOI devices using

total gate silicidation, Proceedings of the IEEE Electron Devices Meeting 4

(2002) 247–250 (December).

[6] V. Kursun, E.G. Friedman, Domino logic with variable threshold voltage

keeper, IEEE Transactions on Very Large Scale Integration (VLSI) Systems 11

(6) (2003) 1080–1093 (December).

[7] A. Alvandpour, P. Larsson-Edefors, C. Svensson, A leakage tolerant multi-phase

keeper for wide domino circuits, in: Proceedings of the IEEE International

Conference on Electronics Circuits Systems, September 1999, pp. 209–212.

[8] Medici Device Simulator, Synopsys, Inc., 2006.

[9] M.W. Allam, M.H. Anis, M.I. Elmasry, High-speed dynamic logic styles for

scaled-down CMOS and MTCMOS technologies, in: Proceedings of the IEEE

International Symposium on Low-Power Electronics Design, July 2000,

pp. 155–160.

[10] Z. Liu, V. Kursun, Robust dynamic node low voltage swing domino logic with

multiple threshold voltages, in: Proceedings of the IEEE/ACM International

Symposium on Quality Electronic Design, March 2006, pp. 31–36.

[11] B. Chatterjee, M. Sachdev, R. Krishnamurthy, Leakage control techniques for

designing robust, low power wide-OR domino logic for sub-130 nm CMOS

technologies, in: Proceedings of the IEEE/ACM International Symposium on

Quality Electronic Design, March 2004, pp. 415–420.

[12] A. Alvandpour, et al., A Sub-130-nm conditional keeper technique, IEEE

Journal of Solid-State Circuits 37 (5) (2002) 633–638 (May).

[13] A. Alvandpour, et al., A conditional keeper technique for sub-0.13 m wide

dynamic gates, in: Proceedings of the IEEE Symposium on VLSI Circuits, June

2001, pp. 29–30.

[14] S.A. Tawfik, V. Kursun, Low-power and compact sequential circuits with

independent-gate FinFETs, IEEE Transactions on Electron Devices 55 (1)

(2008) 60–70 (January).

[15] Meng-Hsueh Chiang, et al., High-density reduced-stack logic circuit techniques using independent-gate controlled double-gate devices, IEEE Transactions on Electron Devices 53 (9) (2006) 2370–2377 (September).

[16] K. Kim, et al., Leakage power analysis of 25-nm double-gate CMOS devices

and circuits, IEEE Transactions on Electron Devices 52 (5) (2005) 980–986

(May).

[17] S. Borkar, et al., Parameter variation and impact on circuits and microarchitecture, in: Proceedings of the IEEE/ACM International Design Automation Conference, June 2003, pp. 338–342.

[18] M. Agostinelli, M. Alioto, D. Esseni, L. Selmi, Trading off static power and

dynamic performance in CMOS digital circuits: bulk vs. double gate SOI

MOSFETs, in: Proceedings of the IEEE European Solid State Device Research

Conference, September 2007, pp. 191–194.

[19] S. A. Tawfik, V. Kursun, High speed FinFET domino logic circuits with

independent gate-biased double-gate keepers providing dynamically adjusted immunity to noise, in: Proceedings of the IEEE International

Conference on Microelectronics, December 2007, pp.175–178.

[20] S. A. Tawfik, V. Kursun, Asymmetric dual-gate multi-fin keeper bias options

and optimization for low power and robust FinFET domino logic, in:

Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems,

December 2008, pp. 1720–1723.

Please cite this article as: S.A. Tawfik, V. Kursun, FinFET domino logic with independent gate keepers, Microelectron. J (2009),

doi:10.1016/j.mejo.2009.01.011

ARTICLE IN PRESS

10

S.A. Tawfik, V. Kursun / Microelectronics Journal ] (]]]]) ]]]–]]]

[21] B.S. Doyle, et al., High performance fully-depleted tri-gate CMOS transistors,

IEEE electron Device Letters 24 (4) (2003) 263–265 (April).

Sherif Tawfik received the B.S. and M.S. degrees in

Electronics and Communications Engineering from

Cairo University, Cairo, Egypt, in 2003 and 2005,

respectively. He is currently pursuing a Ph.D. degree

in Electrical and Computer Engineering at the University of Wisconsin-Madison under the supervision of

Prof. Volkan Kursun. His research interests are in the

area of low-power and variations-tolerant integrated

circuit design and emerging integrated circuit technologies. He has more than twenty publications.

was a visiting professor at the Chuo University, Tokyo, Japan. He served as an

assistant professor in the Department of Electrical and Computer Engineering at

the University of Wisconsin-Madison, USA from August 2004 to August 2008. He

has been an assistant professor in the Department of Electronic and Computer

Engineering at the Hong Kong University of Science and Technology, People’s

Republic of China since August 2008.

His current research interests include low-voltage, low-power, and highperformance integrated circuit design, modeling of semiconductor devices, and

emerging integrated circuit technologies. He served on the editorial board of the

IEEE Transactions on Circuits and Systems II (TCAS-II) from 2005 to 2008. He is a

member of the technical program and organizing committees of a number of IEEE

and ACM conferences and serves on the editorial boards of the IEEE Transactions on

Very Large Scale Integration (VLSI) Systems (TVLSI), IEEE Transactions on Circuits and

Systems I (TCAS-I), and the Journal of Circuits, Systems, and Computers (JCSC). He has

more than eighty publications and four issued and two pending patents in the

areas of high-performance integrated circuits and emerging semiconductor

technologies. Dr. Kursun is the author of the books, Multi-Voltage CMOS Circuit

Design (John Wiley & Sons Ltd., August 2006) and

(China Machine Press, June 2008).

Volkan Kursun received the B.S. degree in Electrical

and Electronics Engineering from the Middle East

Technical University, Ankara, Turkey in 1999, and the

M.S. and Ph.D. degrees in Electrical and Computer

Engineering from the University of Rochester, New

York, USA in 2001 and 2004, respectively.

He performed research on mixed-signal thermal

inkjet integrated circuits with Xerox Corporation,

Webster, New York, USA in 2000. During summers

2001 and 2002, he was with Intel Microprocessor

Research Laboratories, Hillsboro, Oregon, USA responsible for the modeling and design of high-frequency

monolithic power supplies. During summer 2008, he

Please cite this article as: S.A. Tawfik, V. Kursun, FinFET domino logic with independent gate keepers, Microelectron. J (2009),

doi:10.1016/j.mejo.2009.01.011