Phototransistor Switching Time Analysis

advertisement

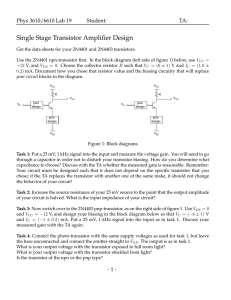

A p p l i c at i o n N o t e AN3009 Phototransistor Switching Time Analysis Authors: Van N. Tran Staff Application Engineer, CEL Opto Semiconductors Robert Stuart, CEL Product Marketing Manager Hardik Bhavsar, San Jose State University Introduction A standard optocoupler provides signal transfer between an isolated input and output via an infrared Emitting Diode (IRED) and a silicon phototransistor. Optical isolation sends a beam of infrared energy to an optical receiver in a single package with a light-conducting medium between the emitter and detector. This mechanism provides complete electrical isolation of electronic circuits from input to output while transmitting information from one side to the other, and from one voltage potential to another. This application note addresses the rise and fall time characteristics of a phototransistor used in common circuits, compared to an improved circuit. Most common optocouplers have a limited switching speed when used in generalpurpose applications. Here we explain the basic operating behavior and outline a method to increase the operating speed behavior of the optocoupler. This modified circuit may provide an alternative in some cases where faster switching edge times are required. Some 6-pin optocouplers provide an electrical access pin to the base of the phototransistor, allowing a bias voltage to the base, to improve response time. The drawback to a base pin is that it provides an access point for noise into the phototransistor. Any external bias configuration must consider noise limitation, as well as not loading capacitance onto the base pin, which will affect device performance. The circuit described here is one method for switching time improvement with a 4-pin package optocoupler without a base-bias pin. The optocoupler output transistor retains basic bipolar characteristics that may be leveraged for better circuit performance. This discussion is around NEC phototransistor optocoupler PS2501-1-A in DIP 4 package and general-purpose PNP transistor 2N4402 arbitrarily chosen; a load resistor of 4.7 k-Ohms, the IRED is pulsed at 1.0 kHz with 50% duty cycle for the measurements at nominal room temperature. The circuit is at 5 Volts, a common operating voltage for use with digital circuits, and other situations where data or pulse-edge events communicate between units. Parameter Definition Rise time is the interval of time it takes a waveform, here the output voltage (Vout) to increase from 10 percent to its 90 percent of its peak value, as shown in figure A. Fall time is the time interval required for a waveform, here the output voltage (Vout) to decrease from 90% to 10 percent of its peak value, as shown in figure A. 90% Output Waveforms 10% tr tf Signal Levels Figure A. Signal levels Current Transfer Ratio (CTR) is the gain of the optocoupler. It is the ratio of the phototransistor collector current compared to the IRED forward current. CTR = (IC / IF) * 100 and is expressed as a percentage. The CTR depends on the current gain (hfe) of the transistor, the voltage between its collector and emitter, the forward current through the IRED and operating temperature. When starting a new design, check the operating conditions and verify your assumptions and calculations by checking a few component samples to ensure the results are similar. Page 1 AN3009 Summary table of rise and fall time in different configurations Tr Tf CTR Common Collector (Fig 1) 4.6 µs 87.1 µs 331% Common Emitter (Fig 2) 89.5 µs 4.7 µs 335% Cascode Configuration with Rb = 1KΩ (Fig 3) 5.4 µs 37.7 µs 309% Cascode Configuration with rb = 1KΩ (Fig 4) 30.7 µs 5.8 µs 305% The data in the table were measured at Ta = 25˚C, Vcc = 5.0 V, If = 5.0 mA at RL = 100Ω for CTR measurement and 4.7kΩ for tr/tf measurement. Figure 1A: CTR, Tr and Tf vs. IF (mA) for Common Collector Configuration The Common Emitter Configuration The Common - Collector Configuration (Fig. 1.0) The collector is the common point of this transistor circuit, and the output taken at the emitter. The output transitions from a low state to a high state when the optocoupler input transitions high. IF VCC In contrast to the common-collector amplifier circuit, the common emitter amplifier circuit (Fig.2.0) has the output taken from the collector. This circuit output transitions from a high state to a low state when the input transitions high. The output resistor is between the voltage supply and the collector pin of the transistor, and the output voltage goes low when the phototransistor is on. The graph of CTR, rise time (tr) and fall time (tf ) as a function of forward current (If ) at Vcc = 5 V @Ta = 25°C is shown in Fig. 2A. VCC 100 Ω RL VOUT RL If VOUT D1 Q1 Common Collector Amplifier Figure 1.0: Common Collector Amplifier 100 Ω The output voltage is at the load resistor between the emitter pin and ground. The graph of CTR, rise time (tr) and fall time (tf ) as a function of forward current (IF) at Vcc = 5 V @Ta = 25°C is shown in Fig. 1A Figure 2.0: Common Emitter Amplifier Page 2 AN3009 Improved Circuit with Figure 4.0: Optocouplers used toCascode drive discreteTopology components forfor motor active high (Fig. 3.0)drive application. Figure 2A: CTR, Tr and Tf vs. IF (mA) for Common Emitter Configuration Rise and Fall Time considerations In the common collector configuration, the rise time performance is much better due to the absence of the Miller capacitance-multiplication effect. Miller C In the common emitter configuration, the transistor collector-base capacitance Ccb is the feedback capacitance. The Miller capacitance characteristic amplifies the capacitance seen by the input, and the result becomes much larger: C’1 = Ccb(1 + gm *RL) >> Ccb where gm is the transconductance of the phototransistor. As a result, C’1 becomes very large due to the gain characteristic of the transistor and limits the higher cutoff frequency of the signal. Circuit test data shows this effect. For the Common Emitter circuit, the output-signal rise time will be slow and the fall time will be faster. For the Common Collector, the Miller capacitance is absent. As a result, its bandwidth is greater. Here, the rise time is fast and the fall time is slow. The next step is to find a circuit that will improve the rise and fall time to meet overall speed requirements. The typical Cascode circuit topology overcomes the effects of Miller capacitance amplification. The Cascode topology is effective by implementing an additional PNP transistor, Q2, and a resistive divider network to bias the base of Q2. However, in the example, a bias resistor, Rb, enables the bias point on Q2 to demonstrate relative rise and fall time improvement. If the bias point needs to be pinned at a fixed voltage point, other bias methods such as including a Zener diode should be considered. 1. Placing VB of Q2 transistor at ground creates a groundedbase amplifier. Grounding either end of the Miller Capacitance helps eliminate its influence. However, the output signal will only go as high as ~0.7V. 2. Placing Rb to connect the base of Q2 to ground (another bias method would be a resistive divider network to the base of Q2) as a demonstration, it provides a bias where the output can swing to Vcc – Vbe( saturation of Q1) –Vbe (saturation of Q2) This is a self-bias configuration and the bias point on Q2 will change as base current changes. The Cascode configuration (Fig. 3) used in this design provides active high logic similar to the common collector configuration. The design used here incorporates a general-purpose PNP transistor Q2, 2N4402, placed as a common base amplifier, with the load connected to the collector of the 2N4402. VCC If Q1 D1 Vb Q2 100 Ω RL VOUT Rb Figure 3: Additonal Transistor with Common Base Configuration Page 3 AN3009 This configuration leads to overall improvement in rise and fall times of the signals under the same drive condition: Load resistor 4.7 kΩ, pulsed at 1.0 kHz with 50% duty cycle at room temperature TA=25°C, and Vcc = +5V. In this topology, the phototransistor does not see the load resistor RL, only the input resistance of the common base transistor Q2, This configuration is duality of the cascode topology in figure 3.0. An NPN transistor, 2N4400, is used and a resistor divider network may be used to bias the 2N4400. Following our previous example, for the purpose of measuring rise time (tr) and fall time (tf ), rb as shown in figure 4.0 is used. VCC re = 25 mV / Ic (in mA.) rb The switching time is strongly dependent on the photocurrent Ic. For example, at VB= 0V or grounded, IF = 5 mA, the photocurrent Ic = 5.16 mA (CTR = 103%), the phototransistor would see a load of re = 4.84 Ω instead of the actual load resistance RL= 4.7 kΩ. As a result, the rise time is faster and fall time is about the same in comparison to the common collector configuration data as shown in figure 1A. Figure 3 below shows the CTR, rise time (tr) and fall time (tf) as a function of forward current under Vcc = 5 V, RL = 4.7KΩ, pulsed at 1.0KHz with 50% duty cycle, Rb = 1KΩ @Ta = 25C. RL Q1 If VOUT 100 Ω Figure 4: Additonal Transistor with Common Base Configuration Either Cascode configuration leads to an overall improvement in rise and fall times of the signals under the same drive condition: Load resistor 4.7 kΩ, pulsed at 1.0 kHz with 50% duty cycle at TA=25°C, Rb = 1K Ω and Vcc = +5V. Figure 4A below shows the CTR, rise time (tr) and fall time (tf ) as a function of forward current under Vcc = 5 V @Ta = 25C Figure 3: Current Transfere Ratio (CTR), T and Tf VS. Forward Current (IF) for cascode configuration using PNP transistor for active high Improved Circuit with Cascode Topology for active low (Fig. 4.0) For certain applications where the designer would like to improve the switching time with similar common emitter topology that provides active low output, the Cascode topology using an additional NPN transistor is shown here. Figure 4A: Current Transfere Ratio (CTR), Tr and Tf VS. Forward Current (IF) for cascode configuration using NPN transistor for active low Page 4 AN3009 Additional info of the Rise Time, Fall Time and CTR vs. Forward Current, If (mA) from different Topologies Following are the graphs for reference based on different topologies with the same load RL=4.7KΩ to measure rise time (tr), fall time (tf ), and RL= 100 to measure CTR, Vcc = 5V, Rb = 1KΩ for cascode topology and the measurement was made at Ta = 25C: 1. Active low using common emitter and cascode: Performance comparisons for Common Collector, Common Emitter and our Cascode circuits at various base resistor values are shown in data tables in the Appendix. As well, we have included data for the traditional Cascode circuit for comparison. In some cases, it may serve better, depending on circuit topology. The alternating behavior of the Common Collector and Common Emitter circuit with regard to rise and fall times is clearly seen in the data. The modified Cascode at Vb=0V has the best performance, though with the lowest output signal. The rise time of the modified Cascode at Vb=1 kΩ is similar to the Common Collector circuit, and significantly faster than the Common Emitter. Performance is adjusted at the bias voltage, with a tradeoff in collector and base currents through the transistors. The fall time of the modified Cascode is faster than the standard Common Collector stage, though not as fast as the Common Emitter on its own. Pick the active high or active low requirement to fit your application. The traditional Cascode topology has corollary performance for rise and fall times, as seen in the data in the Appendix. 2. Active high using common collector and cascode: Note that all of the above is dependent on the optocoupler, the transistor chosen and the operating voltage of the circuit. This topology offers some improvements over a single Common Collector or Common Emitter stage, with the addition of two inexpensive components. Our intent is to show different configurations for a standard optocoupler to provide circuit improvements without adding significant cost. Conclusion: Besides the general circuit configurations, such as Common Emitter or Common Collector, the Cascode configuration can improve the switching time and behavior of the circuit by adding either a NPN or PNP transistor as in the examples shown. In short, remember that the optocoupler has a transistor output that may be leveraged similar to any other transistor to overcome inherent device behavior. This paper provides a general design idea that can be used as a reference to meet design needs. Page 5 AN3009 Appendix These tables show data collected from the Cascode with PNP transistor (2N4402) circuit at: Load resistor is 4.7 kΩ, pulsed at 1.0 kHz with 50% duty cycle at room temperature (TA=25 degrees) and Vcc = +5V. CTR measurements were taken with RL = 110 Ω, to create a similar comparison environment. Rise and fall time measurements were with the RL = 4.7 kΩ. CTR Rb Rb Rb Rb If (mA) 100 'W 470 ‘W 1000 ‘W 10,000 ‘W 1 2 3 4 5 6 7 8 9 10 215 280 255 241 225 215 205 189 174 160 211 284 291 295 294 285 270 245 223 207 222 287 303 309 309 303 283 257 236 222 222 284 310 327 327 318 294 268 246 225 Ic (mA) Rb Rb Rb Rb If (mA) 100 ‘W 470 ‘W 1000 ‘W 10,000 ‘W 1 2 3 4 5 6 7 8 9 10 2.15 5.60 7.64 9.64 11.27 12.91 14.36 15.09 15.64 16.00 2.11 5.67 8.73 11.82 14.68 17.09 18.91 19.64 20.09 20.73 2.22 5.75 9.09 12.36 15.45 18.18 19.80 20.55 21.27 22.18 2.218 5.673 9.309 13.091 16.364 19.091 20.545 21.455 22.182 22.545 Trise (us) Rb Rb Rb Rb If (mA) 100 ‘W 470 ‘W 1000 ‘W 10,000 ‘W 1 2 3 4 5 6 7 8 9 10 6.1 5.6 5.6 5.6 5.4 5.4 5.0 5.1 4.6 4.5 10.5 10.3 8.8 6.7 6.1 5.6 5.1 5.3 5.5 6.1 16.0 13.7 7.9 6.2 5.4 5.2 4.6 4.6 4.3 4.3 28.3 8.8 6.1 5.3 4.7 4.4 4.4 4.1 4.1 4.1 Page 6 AN3009 Appendix (Continued) Tfall (us) Rb Rb Rb Rb If (mA) 100 ‘W 470 ‘W 1000 ‘W 10,000 ‘W 1 2 3 4 5 6 7 8 9 10 50.3 43.6 38.5 34.5 33.0 32.5 32.0 31.4 31.1 31.1 42.0 34.6 32.3 31.5 30.1 31.0 31.0 31.5 33.9 35.2 41.0 36.0 36.0 36.0 37.7 36.7 36.8 36.0 36.0 36.2 70.0 69.0 69.5 68.0 69.5 69.4 69.2 69.1 69.1 69.1 These tables show data collected from a standard Cascode circuit using an NPN transistor 2N4400 at: Load resistor is 4.7 kΩ, pulsed at 1.0 kHz with 50% duty cycle at room temperature (TA=25 degrees) and Vcc = +5V. CTR measurements were taken with RL = 110 Ω, to create a similar comparison environment. Rise and fall time measurements were with the RL = 4.7 kΩ. CTR Rb Rb Rb Rb If (mA) 100 ‘W 470 ‘W 1000 ‘W 10,000 ‘W 1 2 3 4 5 6 7 8 9 10 227 255 242 237 219 213 197 191 170 160 227 255 269 291 291 279 260 240 219 204 218 255 291 309 305 303 281 255 234 218 227 292 314 327 320 314 281 260 242 218 Ic (mA) Rb Rb Rb Rb If (mA) 100 ‘W 470 ‘W 1000 ‘W 10,000 ‘W 1 2 3 4 5 6 7 8 9 10 2.273 5.091 7.273 9.473 10.927 12.773 13.818 15.273 15.273 16.000 2.273 5.091 8.073 11.636 14.545 16.727 18.182 19.164 19.709 20.364 2.182 5.091 8.727 12.364 15.273 18.182 19.636 20.364 21.091 21.773 2.273 5.845 9.427 13.091 16.000 18.864 19.655 20.782 21.782 21.818 Page 7 AN3009 Appendix (Continued) Trise (us) If (mA) Rb 100 ‘W Rb 470 ‘W Rb 1000 ‘W Rb 10,000 ‘W 1 2 3 4 5 6 7 8 9 10 42.0 42.0 34.6 34.4 32.7 27.0 26.6 27.6 26.6 27.5 45.6 32.0 24.0 24.0 24.1 25.1 25.3 26.7 29.8 28.2 43.0 31.7 32.1 32.4 30.7 31.1 30.9 30.6 31.6 31.6 71.2 71.6 71.4 71.7 71.5 71.7 71.8 71.6 71.5 71.4 Tfall (us) If (mA) Rb 100 ‘W Rb 470 ‘W Rb 1000 ‘W Rb 10,000 ‘W 1 2 3 4 5 6 7 8 9 10 6.5 6.0 6.0 6.1 5.9 5.3 5.1 5.1 4.8 4.9 11.5 10.3 9.1 6.7 5.7 6.1 5.7 6.2 6.3 6.2 16.0 13.7 7.9 6.5 5.8 5.2 4.6 4.3 4.6 4.4 31.2 8.9 6.2 5.2 4.7 4.5 4.2 4.3 3.8 3.9 Information and data presented here is subject to change without notice. California Eastern Laboratories assumes no responsibility for the use of any circuits described herein and makes no representations or warranties, expressed or implied, that such circuits are free from patent infringement. © California Eastern Laboratories 04/09 4590 Patrick Henry Drive, Santa Clara, CA 95054-1817 Tel. 408-919-2500 FAX 408-988-0279 www.cel.com Page 8