A 5GHz/1.8V CMOS Active Balun Integrated with LNA

advertisement

Ibersensor 2010, 9-11 November 2010, Lisbon, Portugal

IB-138

Low Power CMOS RFIC Receiver for Wireless Sensor Applications

Fernando Azevedo1, Vitor Fialho2, Fernando Fortes3 and Maria J. Rosário4

Instituto Superior de Engenharia de Lisboa, Lisboa, Portugal

4

Instituto Superior Técnico, Lisboa, Portugal

1,3,4

Instituto de Telecomunicações, Lisboa, Portugal

1

fazevedo@deetc.isel.ipl.pt, 3ffortes@deetc.isel.ipl.pt and 4mrosario@alfa.ist.utl.pt

1,2,3

Abstract

This paper presents the design and simulation of a 5GHz band monolithic low-power receiver

front-end. Intended to be integrated with sensor readout, data conversion and modulation circuitry for

wireless sensor network applications, the fully integrated circuit was implemented in a 0.18µm

CMOS technology. The simulations, optimized to noise performance, gain and minimum differential

phase and magnitude error, were performed with BSIM3 model. Circuit simulations present 29dB

differential power gain at 5.2GHz, a phase and a transducer gain magnitude errors less than 7º and

0.1dB, respectively, in a 100MHz span around 5.2GHz, NF =4dB, 1dBCP = -22dBm, IIP3 = -10dBm,

50Ω input and output match, while drawing 20mA from a 1.8V power supply.

Keywords: Receiver, front-end,

Communications, Wireless Sensor.

CMOS,

I-Introduction

Following the consumer market for cellular

phones, wireless communications evolution

have been carried over radio frequency

integrated circuits (RFICs) technology to areas

with enormous potential of interest, as is the

area of sensors in a variety of possible interface

uses on telemetry. As a matter of fact, the

telemetry needs point to the same goals of

general data transmission for the consumer

market: reduced-costs, reduced-size, better

power management to low consumption, robust

and easy in maintenance solutions emphasizing

higher integration and less weight. The

applications of wireless sensors are growing in a

wide variety and distinct areas like medical

implants, embedded sensors in building, traffic

control and military applications.

Being one of the fastest growing

technologies, CMOS has been elected as one of

the technologies of excellence to develop the

circuitry. To maintain competitive hardware

costs, it has been used since it is the best

solution for low cost and high integration level.

Allowing analog circuits to be mixed with digital

ones, is also the best solution to design the

sensor, the RF transceiver and all the digital

processing needs, all over the same die. Once

at the same die, the various blocks must be

physically separated to maintain blocs protected

Radio

Frequency

Integrated

Circuit,

Wireless

against intra-interferences between each other,

being the attention focused mainly at digital to

protect analogue circuitry. To achieve a high

performance monolithic RF receiver, innovative

RF circuit design is required, to make the best of

a good technology. The front-end chain is one of

the most critical blocks of the receiver, where

the sensitivity is mainly determined by the LNA

noise figure (NF) and gain. Since the LNA is the

first front-end gain stage, special care must be

taken to provide accurate input match, low NF,

good linearity and a sufficient gain over a wide

band of operation.

A fully differential approach is usually

preferred, due to its well-known properties.

Although the differential approach must be

preserved inside the chip, there are cases where

the input signal is single-ended such as RF

image filters and IF filters in a RF receiver. In

these situations, a stage able to convert

single-ended into differential signals, known as

Balun11 is needed.

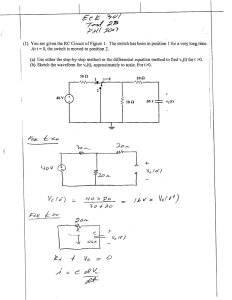

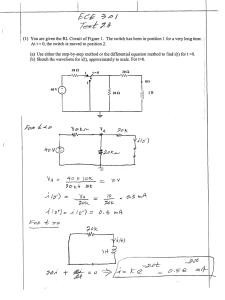

This work reports the design and

implementation of a low-power low-size

monolithic direct-conversion receiver integrated

on a 0.18µm CMOS process, which synoptic

scheme is shown at fig.1. The receiver is

intended to be integrated with sensor readout,

data conversion and modulation circuitry for

1

BALUN - BALanced from UNbalanced signal converter.

Ibersensor 2010, 9-11 November 2010, Lisbon, Portugal

VDD_LNA

VDD_VGA

VDD_BAL

VDD_MIX

RX Front-End

RFIN

DC

LNA

VGA

BALUN

RXOUT+

RXOUT-

Mixer

VCTL

Digital Circuit

VD OUT

6 Bit

DAC

Logic

4

6

VREF

B 3 B2 B 1B 0

4 to 6

bit

IREF

Dig. Ctl

DVDD

DVDD

VCTL_EXT

DGND

DCLK

DGND

LOIN AGND

Fig. 1. Receiver synoptic scheme.

wireless sensor network applications. Is aimed

at IEEE 802.11a standards for WLAN operating

at 5.2GHz band. All the required circuits are

integrated on the same die and are powered by

1.8V supply. The simulated results are shown,

promising excellent experimental performance.

Section II describes the LNA, Balun, VGA,

DAC

and

Mixer

topologies

and

the

interconnected building blocks circuit design.

Section III shows the simulated performance

results focused at gain, phase/amplitude

balance and noise figure. Finally, the last section

draws conclusions and future work.

II-Description of the Circuit Design

The design of the building blocks in CMOS

technology is the subject of next sub-sections.

The all integrated circuitry schematic is not show

for simplicity. The receiver has a RF and LO

input 50Ω single-ended and a differential-ended

50Ω output. Due to the additional noise of the

LNA/Balun following stages, it is necessary to

mitigate the noise effects of these two circuits.

IB-138

To allow a good compromise between high

gain and low noise, a common source topology

is preferable. A schematic of the proposed LNA

is shown in fig. 2. It is a cascode common

source topology, with a simple input and output

matching network to enable wide band. Both

input and output ports are matched to 50Ω The

predominant capacitive matching networks

makes use of all parasitic elements to optimize

input/output matching.

Sizes of ML1 and ML2 devices are

W/L=100/0.18µm with twenty fingers and the

inductors has both 2.89nH at 5.2GHz. The stage

consumption is 7.9mA.

B. Active Balun topology

Several active Balun topologies have been

proposed in the literature. The most cited and a

strong candidate for use as active Balun is the

differential topology shown in fig. 3. Consisting

on a differential pair stage with one of the two

inputs grounded, is capable of providing high

gain and ideally split equally between the output

pair, the RF signal applied to the other input. In

ideal conditions, it provides 180º phase shift

between the two output signals. However, this

solution

has

same

drawbacks

when

implemented monolithically. The differential

architecture shown uses double common

sources to obtain differential output. If

implemented in a monolithic technology, it is

impossible to obtain a perfect ground at the gate

of M2 due to the bond-wire used for grounding

and bond pad parasitic capacitance. Also, as

reported in [5], the impedance of the non-ideal

current source is not as high as required to

equal signal distribution. The two drawbacks

point to an unbalance between the two output

signals, meaning that a correct differential phase

and equal magnitudes are unobtainable.

A. Low Noise Amplifier topology

The LNA is the first active stage and is

responsible for amplifying the weak RF signal

with minimum noise and linear distortion. It must

provide enough gain to reduce the impact of the

following stages in the overall NF. As a first

stage of receiver architecture, considerations

like low NF and high gain must be taken into

account during the LNA design. Besides that,

linearity, input and output impedance match and

stability (Kf) must also be considered. A classical

noise matching technique was used. This

technique, firstly reported in 1960 [2], was

recently re-studied and reported in [3][4].

VD D LN A

LD

C RFOUT

RFO U T

M L2

C RFIN

RFIN

M L1

C VDD

LG

VRE FLN A

CG

GND

Fig. 2. Cascode common source LNA topology.

Ibersensor 2010, 9-11 November 2010, Lisbon, Portugal

VDD

OutM

In

R bias

amplifier topology, as shown at fig. 5. Regulated

by VCTL applied to MV3P and MV3M gate

devices, the gain can be dynamically updated.

This dynamic update mechanism has, as main

advantage, the feature of a lower noise figure

when the gain increases. Realizing all the gain

control after LNA output, in a differential

scheme, has same other advantages related

with noise, common mode appearance and

mismatch. In addition, the devices MV3P and

OutP

180º

M1

M2

C

Ibias

IB-138

V bias

Fig. 3. Differential topology for active Balun.

In contrast with the above referred, the

single-to-differential conversion using the new

balun presented in fig. 4, takes place in two

distinct modes to obtain differential output, one

using a common source and other a common

gate. This provides two main advantages: no

dependency of series gate impedance and no

special care on parasitic bond-wire connection

to ground. Dedicated simulations have

confirmed this behavior.

Even using different source and gate

common modes in each input branch, both

output loads see similar impedance’s. With a

proper layout design the circuit achieves good

phase/gain balance. This solution overcomes

the limitations of the circuit of fig. 3 and has

several advantages when compared with other

reported monolithic active Baluns [5][6].

Sizes of MB1 and MB2 devices are

W/L=100/0.18µm with twenty fingers and the

inductors has both 3.9nH at 5.2GHz. The stage

consumption is 5.5mA.

C. VGA topology and Gain Control Mechanism

MV3M (W/L=15/0.18µm) needs no extra DC

current to control the variable gain.

Due to the down scale rule of CMOS, the

devices size allow to operate at high frequency

band, while preserving minimum noise figure,

during all the dynamic degeneration change.

Sizes of set {MV1P, MV1M, MV2P, MV2M} devices

are W/L=10/0.18µm with two fingers and

W/L=40/0.18µm for {MV4P, MV4M} eight finger

devices. The stage consumption is 7.5mA.

The VGA voltage control must be applied to

VCTL input. As shown in fig. 1 this voltage can be

provided directly in a analogue way or digitally

using internal digital circuitry. The digital

circuitry comprises a 6-bit DAC and a four bit

input logic control plus clock, as shown in fig. 6.

The function of the logic is to choose the best

16 (4-bits) of the 64 samples of the digital to

analogical converter (DAC), allowing the gain

response to have a linear approximation with 16

dynamic levels. The gain level change is

approximately 1dB per step.

The consumption of the all digital circuit is

less then 230uA. The function of the Logic circuit

can be replaced with a microcontroller, when in

a complete integrated transceiver system.

The gain control mechanism takes place

using a differential variable gain common source

V DDVGA

R PMM

VD D B A L

RPMM

R PMM

R PMM

CMOP RFOU T

P

C BP

C BM

LBP

LBM

C BOP

C BOM

RFOU T

M V4P

RFIN +

M B2

RFIN

s

M V4M

M V3P

M V2P

MV3M

MV2M

RFIN -

CBB

IBia

C MOM

RFOU TM

C Bph

M B1

GND

M

RFOU TP

M V1P

MV1P

VR E FLN A

VC TL

VR E F

GND

Fig. 4. Balun topology used in this work.

Fig. 5. VGA topology

Ibersensor 2010, 9-11 November 2010, Lisbon, Portugal

DVD D

VR EF

IB-138

VDDMIX

Digital Circuit

R LMP

Logic

DCLK

Dig. Ctl

R PMM

R LMM

BBP

VOU T

DAC

4 to 6

bit

4

B 3B 2 B 1B 0

RPMP

6 Bit

6

C MBBP

LOP

M M2P M M2M

M M3P M M3M

C MBBM

BBM

LOM

DGND

RFP

IR EF

M M1P

M M1M

RFM

a). Digital synoptic scheme.

ISRC

V DDDAC RLDAC

OUTDAC

M B0.1

M B1.1

M B0.2

M B1.2

M B2.1

M B2.2

MB3.1

M B3.2

MB4.1

MB4.2

M B5.1

M B5.2

V REFDAC

M B0.3

M B1.3

M B2.3

M B3.3

B0

B1

B2

B3

M B4.3

B4

M B5.3

B5

GND

b). Six bit input DAC topology.

Fig. 6. Digital circuit stage.

D. Mixer topology

The mixer is a very important stage in

transceiver design that allows to eliminate the

off-chip discrete components to fully integration.

This stage converts all of the RF spectrum

passing through the RF filter directly to

baseband. Attending the receiver goals the

design consider the compromises between

conversion gain, port-to-port isolation, linearity,

local oscillator power, noise figure, dynamic

range, voltage supply and current consumption.

The direct conversion mixer presented in

fig. 7 is a variation of the doubly balanced

Gilbert cell topology. Doubly balanced mixers

have excellent port-to-port isolation, conversion

gain, broad bandwidth, and spurious-signal

rejection.

The mixer employs an all n-channel devices

and resistive loads for high frequency operation

and requires no inductors on or off-chip. It

requires a reduced LO power and presents

conversion gain. The signal path has both

differential input and output. The differential

output current is converted to voltage by the

differential RLM loads. As all the devices are

fabricated on a single chip, the balance is very

good and high spurious rejection is obtained.

The parasitic capacity is used as Low-pass filter.

All the remaining filtering is performed digitally

by the DSP at baseband.

GND

Fig. 7. Mixer topology.

The differential pair constituted by

MM1P-MM1M impose the input transconductance

and single balanced pairs devices M M2P-MM2M

and MM3P-MM3M act like current-steering

switches of the cell.

A compromise was attended in respect to

the width of the active devices. The path signal

devices are designed with a minimal width to

obtain the highest possible fT. However, in order

to obtain a reasonable gain, a generous g m was

granted. Sizes of MM1P and MM1M devices are

W/L=20/0.18µm with four fingers and the set

{MM2P, MM2M, MM3P, MM3M} devices are

W/L=10/0.18µm with two fingers.

The LO and RF ports were biased from

external voltage sources through resistors, not

shown for simplicity. The current source, that is

a classic current mirror, controls the

consumption of the mixer and regulates the

current for the cell. The stage consumption is

1mA.

E. Passive and active

Inter-stage matching

input/output

and

To achieve input and output match to 50Ω,

the size of the input and output devices are

designed in accordance with the bondwire set,

respectively at input and output, keeping the

matching networks simple.

The criteria of simple matching networks

were applied also to inter-stage matching,

controlling the devices geometries as well as

matching parasitic elements and appropriately

biasing active devices. The match between

balun and the gain controlled circuit, using a

single passive element per branch (capacitor

CBOP and CBOM) was possible by using an active

Ibersensor 2010, 9-11 November 2010, Lisbon, Portugal

match (MV2P and MV2M) avoiding a more complex

and sized passive nets including inductors.

The single-input and the differential outputs

are all matched to 50Ω. The 50Ω output loads

were used just for testing purpose.

Inter-stage matching networks makes use of

the parasitic elements of the active devices, the

bias sources and the coupling capacitors, to

optimize matching. Coupling capacitors are used

to achieve DC isolation between the active

devices of the stages.

Since external source currents are

preferable, the bias voltages and currents are

created using extra voltage/current sources to

internal voltage/current reference bias, not

shown for simplicity. Some external bias are offchip controllable for testing purpose only.

All the active devices used are in stack and

have a fixed width of 5µm with variable number

of fingers. The input common-source device ML1,

with size of W/L=100µm/0.18µm, is optimized for

noise and input match. The device ML2, which

has the same size of ML1, is optimized for noise

and inter-stage match with Balun input. The

output stage is AC coupled to differential outputs

loads with CMOP and CMOM capacitors. Inductors

LBP and LBM, which are DC coupled to the

common-source

and

common-gate,

respectively, are essential elements to achieve

the 50Ω impedance match in both differential

outputs. On-chip spiral inductors play a

significant role in realizing fully integrated RF

circuits. Due to the substrate losses, they exhibit

poor performance in terms of their quality factor,

strongly limiting circuit results. However, even

with low Q, it is possible to obtain good results

with the topologies presented, as shown in the

following section.

IB-138

Fig. 8 presents the simulations of phase

and magnitude mismatch. Unbalance between

the two branches is expressed from their gain

magnitude and phase differences extracted from

forward

transmission. A

broadband

well

balanced behavior was achieved, since the

circuit exhibits phase and amplitude errors

between the two output ports lower than 8º and

0.1dB, respectively, from 4.7GHz to 5.7GHz RF

input frequency. These errors are better than 7º

and 0.01dB in a 100MHz span centered at

5.2GHz.

In fig. 9, input/output match and gain

magnitude are expressed in terms of

S-parameters obtained between RF input and

VGA ouput and all the bits at high state. The

circuit has a good input match (S11 = -12dB) and

reasonable output mach at both output branches

(S22 = S33 = -9dB). The

gain, S31 and S21,

presents a maximum value of 24dB at 5.2GHz,

leading to 27dB single-ended input to differential

output gain. In a 1GHz span centered at

5.2GHz, the gain is higher then 16dB

(19dB differential). The noise performance is

shown at the same graph. At 5.2GHz the noise

Fig. 8. Phase and Magnitude Mismatch.

III-Circuit Simulation Results

The proposed circuit was simulated using

Spectre

from

Cadence [7]

with

the

0.18µm/1.8V-RFCMOS process from UMC [8].

The circuit was simulated over a large variety of

conditions. In the 4.5GHz to 5.5GHz frequency

band, the results were taken with a 1.8V supply

voltage and using 50Ω single-ended input and

output ports. Noise figure, transducer gain,

return loss and linearity were optimized by

adjusting current and voltage bias. The

simulation results are illustrated in figures 8 to

11. Results are promising for gain, noise figure

and phase and magnitude mismatch. Stability is

also insured (Kf > 2.5).

Fig. 9. S-Parameters, NF and Phase.

Ibersensor 2010, 9-11 November 2010, Lisbon, Portugal

IB-138

figure (NF) is 3.5dB and the phase and

magnitude errors are 7º and 0.01dB,

respectively. In the 4.5GHz to 5.5GHz band, the

circuit presents a NF lower then 4dB. Figures 11

and 12 demonstrate that the overall circuit is

highly linear, since the input-referred 1dB

compression

point

is

-22dBm and

the

input-referred third-order intercept point is

-10dBm.

Fig. 12 presents non-differential gain and

noise figure versus digital words measured at

VGA output. A non-linear sixty four and a linear

sixteen gain levels are shown on the same

graphic in different axis. As can be observed the

curve has a good linear approximation,

presenting a sixteen 1dB step dynamic levels.

The noise figure decreases when gain increase.

IV-Conclusions

A direct conversion front-end receiver

comprising an LNA, active Balun, VGA, Mixer

and digital control circuitry at the same die was

presented. Intended to be used in a wireless

sensor network, the total circuit is fully integrated

in a low cost CMOS process with total area of

1.84mm2. Simulations show that under a 1.8V

power supply the circuit has a 29dB maximum

Fig. 10. 1dB compression point.

0

10

20

W_6Bit [Dec]

30

40

50

60

20

20

noDifGain4bit [dB]

NF [dB]

16

noDifGain6bit [dB]

12

12

Linearized Gain Curve

8

8

4

NF [dB]

Gain [dB]

16

4

0

0

0

5

W_4Bit [Dec]

10

15

Fig. 12. Gain and Noise Figure versus Digital words

differential power gain at 5.2GHz, with 21mA

current consumption. The LNA has 16dB, the

Balun 3dB, the VGA [-5, 5] dB and Mixer 2dB,

meaning a non-differential power gain within

interval [16, 26] dB depending of the VGA V CTL.

The contribution of the overall circuit presents a

well balanced broadband behavior, since the

Balun and following stages exhibits low

differential phase and magnitude errors.

Table .I summarize the circuit performances.

Summary Circuit Performances

Technology:

CMOS 180nm UMC

Active Area:

0.8mm2

Total Area (includ. pad´s):

1.84mm2

Power Supply:

1.8V

Total Current:

< 20.9mA

Power Consumption:

37.6mW

RF Frequency:

5.2GHz

Wideband:

>1GHz

{S11}, {S22, S33} @ 5.2GHz:

< -12dB, -3dB

S21, S31 @ 5.2GHz:

> 26dB

Maximum Differential Gain : > 29dB

Noise Figure (*):

< 4dB

LNA Gain @5.2GHz

16dB

Balun Gain @5.2GHz

3dB

VGA variation Gain@5.2GHz [-5, +5]dB

Mixer Gain @5.2GHz

2dB

Input 1dB comp. point:

-22 dBm

IIP3

-10 dBm

Phase Mismatch (*):

< 8º (7º @ 5.2GHz)

Gain Mag. Mismatch (*):

< 0.1 dB (0.01 dB @5.2GHz)

(*) in Referred Band

Fig. 11. Two-tone test IP3.

Table.I. Overall circuit performances.

Ibersensor 2010, 9-11 November 2010, Lisbon, Portugal

An experimental prototype of the receiver

has been fabricated in a UMC 0.18µm CMOS

technology. Fig. 13 shows a photograph of the

die, which active occupied area are 0.8mm 2

(1.84mm2 including pads). This prototype is

currently under experimental tests. The chip has

been directly mounted on a printed-circuit board

such that a ground plane lies under the die,

providing a low-impedance connection to the

backside and all of the ground pads (fig. 14).

Various supply and bias decoupling techniques

reduce the effect of both trace inductance’s and

external sources of noise. The differential LO

signals are generated by means of a balun (only

used for experimental tests) similar to that

shown in fig. 4. A number of precautions have

been taken in the layout of the circuit. First,

various pads are dedicated to the ground

Fig. 13. Receiver die photograph.

Fig. 14. Chip-on-board prototype.

IB-138

connection so as to minimize the effect of

bondwire inductance. Second, the RF input pad

capacity and respective wirebond´s of the LNA

and LO where taken in account during

simulations. Third, the gate resistance of the

LNA and mixer transistors is reduced to

acceptably low levels by proper layout.

The performance measurements are in

progress and should be soon available. To

conclude, one must notice that the proposed

circuit has been designed to match, in a near

future work, the inputs of a differential

integrated oscillator and a smart sensor (to be

reported soon).

References

[1] Wendong Liu et all, BSIM3v3.2.2 MOSFET

Model Users Manual, University of California,

Berkeley, 1999.

[2] H. A. Haus et all, "Representation of noise in

linear two ports", Proceeding of IRE, vol. 48,

pp. 69-74, January 1960.

[3] T. Nguyen, C. Kim, G. Ihm, M. Yang and S. Lee,

"CMOS Low Noise Amplifier Design Optimization

Techniques", IEEE Transactions on Microwave

Theory and Techniques, vol. 52, May 2004.

[4] R. Elkinm Roa et all, "A Methodology for

CMOS Low Noise Amplifier Design" IEEE

Proceedings of Integrated Circuits and Systems

Design, vol. 150, nº 3, March 2003.

[5] M. Rajashekharaiah et all, "A New Gain

Controllable On-Chip Active Balun for 5GHz Direct

Conversion Receiver", IEEE Transactions on

Microwave Theory and Techniques, vol. 50, nº 1,

pp. 377-383, January 2002.

[6] Ta-Tao Hsu and Chien-Nan Kuo, "Low Power

8GHz Ultra-Wideband Active Balun", IEEE Silicon

Monolithic Integrated Circuits in RF Systems

Conference, January 2006.

[7] Cadence, version 5.1, San Jose, CA, 2005.

[8] United Microelectronics Corporation, “UMC

0.18um Cadence-based Mixed Mode/RF CMOS

Foundry Design Kit User’s Manual”, UMC, 2006.