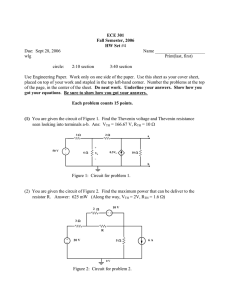

Part 1

advertisement

Kuwait University College of Engineering & Petroleum Electrical Engineering Department Designed & Edited By Eng. Ahmed Shafik Eng. Mohamed Tawfik Supervised By Dr. Meshaal Al-Shaher Dr. Sadek Al-Nasser Lab Schedule Date Week Experiment Title Quiz From To 1 3-Feb 7-Feb Introduction and DC SPICE training 2 10-Feb 14-Feb Ex1. Ohm's Law 3 17-Feb 21-Feb Ex2. KVL and KCL 4 24-Feb 28-Frb عطلة العيد الوطني Ex3. Node, Mesh and Superposition Pre-Lab Report Quiz 2 Ex4. Thevenin Equivalent Theorem Quiz 3 Quiz 1 5 3-Mar 7-Mar 6 10-Mar 14-Mar 7 17-Mar 21-Mar First Exam 8 24-Apr 28- Mar Ex5. AC Measurements Training Quiz 4 9 31-Mar 4-Apr Ex6. Transient and Pulse Responses 10 7-Apr 11-Apr Ex7. Phase shift Measurements Quiz 5 11 14-Apr 18-Apr Exp 8 : Sinusoidal Steady-state power calculation Quiz 6 12 21-Apr 25-Apr Exp 9 : Power Consumption Quiz 7 13 28-Apr 2-May Second Exam Grading Policy Performance Pre-Lab Reports 7 Quizzes Exams Total 5% 10% 15% 20% 50% 100% Data Sheet should be signed by the lab engineer at the end of the lab Absence of 3 out of 10 lab sessions = FA. All reports and data sheets should be done by computer; no hand writing will be accepted. Pre-Lab = Data Sheet + Spice Simulation Report Grading Policy Cover Table of Contents Objective Equipment Theory Procedure + Circuit Data Sheet Exercise Conclusion References Report Format Total 1 1 2 1 5 3 2 15 Lab Regulations 1) Pre Lab Note: (10 points) PSpice simulation report (student name and ID must be typed, otherwise will be discarded) (7 points) Find Data Sheet at the end of each experiment. Theoretical part should be filled in and printed by computer before the lab. (3 points) Note: Lab engineer has to sign the pre lab note before students leave the lab. 2) Performance: (5 points) Students should attend the lab with the following items: o Lab note o Calculator o Stationery No side talks will be allowed during the lab session. Students have to leave the bench clean and switch all the equipments off before leaving the lab. Food and drink is not allowed in the labs. Cell phone use in the labs is prohibited. 3) Attendance Students should attend the lab in time. Late students will not be allowed to attend the lab and will get zero mark for (Pre Lab Note, Performance, Quiz and Report). Students can attend in their section only, no switching between labs will be allowed for any reason. Absent students for 3 out of 10 labs or more will get FA. Students have to attend the two practical tests, otherwise, will be graded FA. 4) Report Layout: A typical lab report should contain the following sections (in order), you can download the report sample from the site: Cover Page Table of Contents Objective Theory Experimental Procedure + Exercise PSpice Simulation Data Sheet Conclusion References . Writing techniques: Report and Pre Lab note should be written by computer. The font and size of the normal text is TimesNewRoman 12. The font and size of the heading and subheading is TimesNewRoman 16/14. The report should contain page numbers. All figures and tables should have a title caption. The theory part should contain (figures, equations, description) for each part of the objective. 1 Familiarization, and Ohm's Law Objectives To be familiar with the laboratory equipment and components. Verification of Ohm’s law. Series and parallel circuits. Theory Part I : Lab equipment and components: DC Power Supply: It is a multi-channels power source device to generate a variable DC voltage, Figure 1-1: DC power supply sample Function Generator (FG): It is a device to generate a variable AC signals with different wave forms (sine, square and triangle). Figure 1-2: Function Generator 1 Resistor: There are two types of resistors in the lab, resistor substitution box (from 0 to 9.999 M) and discrete resistors. See Figure 1-5 for the discrete resistor values reading table. Resistor Substitution Box Discrete Resistors Figure 1-3: Resistors 4-band Color Code Figure 1-4: 4-band color code table 2 5-band Color Code Figure 1-5: 5-band color code table 3 Example: (a) (b) Figure 1-6: Color code example a) For the resistor of figure 1-6-a, the value can be calculated as follows: R N 1N 2 N 3 N 4 Where: Ni = band value. R = 02 x 105 + 10% = 200 K + 10% b) For the resistor of figure 1-6-b, the value can be calculated as follows: R N1 N2 N3 N4 N5 Where: Ni = band value. R = 330 x 101 + 0.1% = 3.3 K + 0.1% 4 Inductor: There is inductance substitution box in the lab (from 0 to 9.999 H). Figure 1-7: Inductance substitution box Capacitor: There is capacitance substitution box in the lab (from 0 to 99.999 uF). Figure 1-8: Capacitance substitution box Digital Multi-Meter (DMM): DMM is a measuring instrument to measure voltage, current, ohm, frequency. Figure 1-9: DMM sample 5 Digital Oscilloscope (CRO): CRO is a multi-channels measuring instrument to measure and display voltage wave forms with different measurements readings. Figure 1-10: CRO Sample Bread Board: It is a board to connect the circuits. Figure 1-11: Bread Board Sample 6 Part II : Ohms's Law: Ohm's Law says: The current in a circuit is directly proportional to the applied voltage. V I R (1) I I 1/R V Circuit Diagram Relationship Between V & I (slope=1/R) Figure 1-12: Ohm’s Law Part III : Series & Parallel Circuits: Figure 1-13: Series and Parallel Connections 7 Connect the circuit as shown in Figure 1-14 by the following steps: PSpice Simulation Part I: Figure 1-14: Circuit Diagram 1) Start PSpice [Appendix A-1] 2) Add a Resistor [Appendix A-2] (R1=2 KΩ) 3) Add DC Voltage Source (Vs) [Appendix A-5] 4) Add Ground [Appendix A-11] 5) Connect the circuit by adding wires [Appendix A-10] 6) Add CRO current probe to measure I [Appendix A-12] 7) Select DC sweep analysis wit the following parameters [Appendix A-14] Name = VS Start Value = 0 End Value = 10 Increment = 1 8) Simulate the circuit [Appendix A-13] 9) The following wave form will be displayed in a new window. 2.8mA 2.4mA 2.0mA 1.6mA 1.2mA 0.8mA 0.4mA 0A 0V 0.5V 1.0V 1.5V 2.0V 2.5V 3.0V 3.5V 4.0V 4.5V 5.0V 5.5V 6.0V 6.5V 7.0V 7.5V 8.0V 8.5V 9.0V 9.5V 10.0V I(R1) V_Vs 10) Calculate the line slope = and compare it with the theoretical value. 8 Part II: I (a) I (b) Figure 1-15: Circuit Diagram 1) Start PSpice [Appendix A-1] 2) Add Resistors [Appendix A-2] R1= R2=2KΩ, R3=5.1KΩ, R4= R5=2KΩ 3) Add DC Voltage Source (Vs) [Appendix A-5] Vs = 10 V 4) Add Ground [Appendix A-11] 5) Connect the circuit by adding wires [Appendix A-10] 6) Simulate the circuit [Appendix A-13] 7) Calculate the equivalent resistor. R AB1 = = 1) Start PSpice [Appendix A-1] 2) Add Resistors [Appendix A-2] R1= 1KΩ, R3=5.1KΩ, R2=1KΩ 3) Add DC Voltage Source (Vs) [Appendix A-5] Vs = 10 V 4) Add Ground [Appendix A-11] 5) Connect the circuit by adding wires [Appendix A-10] 6) Simulate the circuit [Appendix A-13] 7) Calculate the equivalent resistor. R AB2 = 9 = Experimental Work Equipments: 1) DC Voltage Source 2) Bread Board. 3) DMM 4) Discrete resistors. I Figure 1-16: Circuit Diagram Procedure: Part I : Ohm’s Law: 1) Select the resistor R = 2 KΩ using color table in Figure (1-4), measure the resistor value R= 2) Connect the circuit as shown in Figure 1-16 with the shown values. 3) Vary the DC voltage source and measure I. Fill table 1-1. Table 1-1 VS I (mA) 2 4 6 8 10 Q1: Draw V versus I, find the slope of the curve and what does the slope represent?. Theoritical Measured 100 Q2: Compare the slope of Q1 with the theoretical value. %error Q3: What are the error sources in Q2? 10 Theoritical Part II: Parallel and Series Circuits: (a) B2 A (b) Figure 1-17: Circuit Diagram 1) Connect the circuit as shown in Figure 1-17-a, R1= R2=2KΩ, R3=5.1KΩ, R4= R5=2KΩ, Measure RAB1. RAB1= 2) Connect the circuit as shown in Figure 1-17-b, R1=1KΩ, R3=5.1KΩ, R2=1KΩ. Measure RAB2. RAB2= Q4: Calculate RAB1 and RAB2 theoretically. Q5: What is the relation between the circuit of Figure 1-17a and Figure 1-17b 11 Pre-Lab Report 1) PSpice Simulation: Part 1: Simulation for Circuit 1-14: PSpice DC Sweep Analysis Curve: Slope of the curve = 12 Part II: Simulation for circuit of Figure 1-15-a = R AB1 = Simulation for circuit of Figure 1-15-b R AB2 = = 13 2) Data Sheet: Part I: R Measured = Table 1-1 I (mA) VS Theoretical (PSpice) Practical (Measured) 2 4 6 8 10 Part II: RAB1 RAB2 Theoretical Practical Theoretical Practical (PSpice) (Measured) (PSpice) (Measured) 14 2 KVL, KCL, and equivalent circuit resistance Objectives Verification of KVL and KCL. Simulating the DC circuits using PSpice. Measuring and calculating the equivalent resistance of different circuits. Theory Kirchhoff’s Voltage Law (KVL) KVL states that the algebraic sum of all voltages around a closed path (or loop) is zero. Figure 2-1 shows an example for closed loop circuit. For the circuit shown in Figure 2-1, applying KVL: Figure 2-1: KVL example Kirchhoff’s Current Law (KCL) Kirchhoff’s current law (KCL) states that the sum of the currents entering a node is equal to the sum of the currents leaving the node. For the circuit shown in Figure 2-2, applying KCL: Figure 2-2: KCL example 15 Parallel and Series Circuit Connections n n R ab R1 R 2 ... R N R n N 1 1 1 1 1 ... R ab R1 R 2 R N n 1 R n Series Connection Parallel Connection N n 1 Figure 2-3: Series-Parallel Connections Delta to Wye Conversion Delta to Why conversion (given Ra, Rb, Rc) Why to Delta conversion (given R1, R2, R3) Figure 2-4: Delta Why conversions 16 Connect the circuit as shown in Figure 2-5 by the following steps: PSpice Simulation + - - + L2 L1 I3 I2 A + + - - I1 + - - L3 L4 - Figure 2-5: Circuit Diagram 1) Start PSpice [Appendix A-1] 2) Add a Resistor [Appendix A-2] (R1= R2=1KΩ, R3=2KΩ, R4=3.9KΩ, R5=5.1 KΩ) 3) Add DC Voltage Source (Vdc) [Appendix A-5] (V1=10 Volt, V2=15 Volt) 4) Add Ground [Appendix A-11] 5) Connect the circuit by adding wires [Appendix A-10] 6) Select the bias point simulation analysis [Appendix A-15] 7) Simulate the circuit [Appendix A-13] 8) Activate the voltage and current icons in the tool bar. 9) Fill Table 2-1. Table 2-1 I1 I2 Q1: Verify KCL at point A. Delta to Wye Conversion 17 I3 3.9 3.9 1 5.1 10 2 2 10 10 Figure 2-6: Circuit Diagram 1) Start PSpice [Appendix A-1] 2) Add a Resistor [Appendix A-2] 3) Add DC Voltage Source (Vdc) between the two nodes A and B = 10 Volt[Appendix A-5] 4) Add Ground [Appendix A-11] 5) Connect the circuit by adding wires [Appendix A-10] 6) Select the bias point simulation analysis [Appendix A-15] 7) Simulate the circuit [Appendix A-13] 8) Activate the voltage and current icons in the tool bar. 9) Calculate the value of RAB Rab == = 18 Experimental Work Equipment: 1) DC Voltage Source 2) Bread Board. 3) DMM 4) Discrete resistors. Part A – KVL & KCL: 1) Select (using color table in Appendix B-1) and measure (using DMM) the resistors values. Fill the measured values of the resistors in Table 2-2. Table 2-2 R1 R2 R3 R4 R5 2) Connect the circuit shown in Figure 2-5, adjust V1 = 10 V and V2 = 15 V using DMM. 3) Fill table 2-3. Table 2-3 VR1 VR2 VR3 VR4 VR5 I1 I2 I3 Q1: Using the measured values of table 2-2 and 2-3, verify KVL for closed loops L1, L2, L3 and L4. Loop L1: Loop L2: Loop L3: Loop L4: 19 Q2: Using the measured values of tables 2-2 and 2-3, verify KCL at node A. Q3: Repeat Q1 using results of PSpice. Part B - Delta to Wye Conversion and equivalent resistance of different circuits: 3.9 3.9 1 5.1 10 2 2 10 10 Figure 2-7: Circuit Diagram 1) Connect the circuit as shown in Figure 2-7. 2) Using DMM measure Rab. Rab = Q4: Find Rab theoretically in details (step by step with figures) and compare it with measured value in step 2 and the simulated value by PSpice. 20 Pre-Lab Report 1) PSpice simulation of KCL circuit Table 2-1 I1 I2 Delta to Wye simulation circuit Rab == = 21 I3 2) Data Sheet: Part A Table 2-2 R1 R2 R3 R4 R5 Theoretical Measured Table 2-3 VR1 VR2 VR3 VR4 VR5 I1 PSpice Measured Part B Rab Theoretical (PSpice) Practical (Measured) 22 I2 I3 3 Nodal, Mesh and Superposition Analysis Objectives Verification of Nodal analysis method. Verification of Mesh analysis method. Verification of Superposition technique. DC circuits analysis using PSpice. Theory Nodal Analysis Analysis Steps: 1. Select a node as the reference node. Assign voltages v1, v2,…, vn-1 to the remaining n−1 nodes. The voltages are referenced with respect to the reference node. 2. Apply KCL to each of the n−1 non reference nodes. Use Ohm’s law to express the branch currents in terms of node voltages. 3. Solve the resulting simultaneous equations to obtain the unknown node voltages. Example: Figure 3-1: Nodal Example Applying nodal equation for the circuit of Figure 3-1: V N 1 V 1 V N 1 V N 1 V N 2 0 R1 R3 R2 V N 2 V 2 V N 2 V N 2 V N 1 0 R5 R4 R2 23 Mesh Analysis A mesh is a loop which does not contain any other loops within it. Analysis steps: 1. Assign mesh currents i1, i2, . . . , in to the n meshes. 2. Apply KVL to each of the n meshes. Use Ohm’s law to express the voltages in terms of the mesh currents. 3. Solve the resulting n simultaneous equations to get the mesh currents. Example: Figure 3-2: Mesh Loop Example Applying mesh loop equation for the circuit of Figure 3-2: Superposition technique: The superposition principle states that the voltage across (or current through) an element in a linear circuit is the algebraic sum of the voltages across (or currents through) that element due to each independent source acting alone. Superposition steps: 1. Turn off all independent sources except one source. Find the output (voltage or current) due to that active source using nodal or mesh analysis. 2. Repeat step 1 for each of the other independent sources. 3. Find the total contribution by adding algebraically all the contributions due to the independent sources. Example: For the circuit shown in Figure 3-1, to find IR1 using super position: 24 Disconnect the voltage source V2 and replace it with a wire (short circuit it) as shown in Figure 3-3-a. Solve for IR1’. Disconnect the voltage source V1 and replace it with a wire (short circuit it) as shown in Figure 3-3-b. Solve for IR1”. IR1 = IR1’ + IR1” IR1” IR1’ (a) (b) Figure 3-3: Superposition Technique Example PSpice Simulation Connect the circuit as shown in Figure 3-4 by the following steps: L4 L1 L3 L2 Figure 3-4: Circuit Diagram 1) Start PSpice [Appendix A-1] 2) Add a Resistor [Appendix A-2], R1=1K, R2=2K, R3= R4= 3.9K, R5=2K, R6=R7=10K 3) Add DC Voltage Source (Vdc) [Appendix A-5], V1 = 15 V and V2 = 10 V. 4) Add Ground [Appendix A-11] 25 5) Connect the circuit by adding wires [Appendix A-10] 6) Select the bias point simulation analysis [Appendix A-15] 7) Simulate the circuit [Appendix A-13] 8) Activate the voltage and current icons in the tool bar. 9) Fill Table 3-1. Table 3-1 IR5 IR3 IR7 IR4 VA VB 10) Deactivate V2 and simulate the circuit’ [Appendix A-13] 11) Fill table 3-2 Table 3-2 12) Deactivate V1 and simulate the circuit” [Appendix A-13] 13) Fill table 3-3. Table 3-3 Q1: Verify superposition technique for VA and IR3. Experimental Work Equipments: 5) DC Voltage Source 6) Bread Board. 7) DMM 8) Discrete resistors. Part A – Nodal and Mesh Analysis a. For the circuit shown in Figure 3.4, select (using color table in appendix B-1) and measure (using DMM) the resistors. Fill the measured values of the resistors in table 3-4. 26 Table 3-4 R1 R2 R3 R4 R5 R6 R7 b. Connect the circuit shown in Figure 3-4, adjust V1 = 15 V and V2 = 10 V using DMM. c. Fill table 3-5. Table 3-5 IR5 IR3 IR7 IR4 VA Q1: Using the measured values of table 3-4 and 3-5, verify Nodal equations for A and B. Node A: Node B: Q2: Using the measured values of table 3-4 and 3-5, verify Mesh equations. Mesh L1: Mesh L2: Mesh L3: Mesh L4: Part B – Superposition technique: 1) Deactivate the voltage source V2, measure and fill table 3-6 for and 2) Deactivate the voltage source V1, measure and fill table 3-6 for and 3) Verify superposition technique and fill table 3-6 for Table 3-6 27 and VB Pre-Lab Report 1) PSpice Simulation for circuit of Figure 3-4 Table 3-1 IR5 IR3 IR7 IR4 Simulation for circuit with V1 only Table 3-2 28 VA VB Simulation for circuit with V2 only. Table 3-3 1) Data Sheet Table 3-4 R1 R2 R3 R4 R5 R6 R7 Theoretical Measured Table 3-5 IR5 IR3 IR7 PSpice Measured Table 3-6 PSpice Measured 29 IR4 VA VB 4 Thevenin’s Equivalent Circuit & Max. Power Transfer Objectives Verification of Thevenin’s Theory. Verification of maximum power condition. Determination of Thevenin’s Eq. Circuit using PSpice. Theory Thevenin’s Theory Thevenin’s theorem states that a linear two-terminal circuit can be replaced by an equivalent circuit consisting of a voltage source VTh in series with a resistor RTh, where VTh is the open-circuit voltage at the terminals and RTh is the input or equivalent resistance at the terminals when the independent sources are turned off. (a) Original Circuit (b) Thevenin Equivalent Circuit Figure 4-1: Thevenin Theory Maximum Power Transfer Maximum power is transferred to the load when the load resistance equals the Thevenin resistance as seen from the load (RL = RTh). For Figure 4-2, maximum power equation is as follows: (1) 30 (a) The circuit used for maximum power (b) Power delivered to the load as a function transfer of RL Figure 4-2: Maximum Power Circuit PSpice Simulation Connect the circuit as shown in Figure 4-3 by the following steps: I x y Figure 4-3: Circuit Diagram 1) Start PSpice [Appendix A-1] 2) Add a Resistor [Appendix A-2] R1=2KΩ, R2=2KΩ, R3=3.9KΩ, RL=5.1KΩ 3) Add two DC Voltage Source (Vdc) [Appendix A-5] V1=10Volt, V2=12Volt 4) Add Ground [Appendix A-11] 5) Connect the circuit by adding wires [Appendix A-10] 31 Part 1- Finding I through RL: 1) Select the bias point simulation analysis [Appendix A-15] 2) Simulate the circuit [Appendix A-13] 3) Activate the voltage and current icons in the tool bar. IRL = mA Part 2: Calculating I using Thevenin’s Circuit A) Finding VTH 1) Change the value of RL to be 1T (high value equivalent to open circuit). 2) Simulate the circuit [Appendix A-13] 3) Activate the voltage and current icons in the tool bar. Calculate VTH = Vxy VTH = V B) Finding RTH 1) Change the value of RL to be 1f (very small value equivalent to short circuit). 2) The circuit will be as shown in Figure 4-4. 3) Simulate the circuit [Appendix A-13] 4) Activate the voltage and current icons in the tool bar. Calculate RTH Isc Figure 4-4: Circuit Diagram 32 RTH VTH I SC Q1: Using Thevenin Equivalent Circuit, calculate IRL and compare it with the value in part 1. Experimental Work Equipments: 9) DC Voltage Source 10) Bread Board. 11) DMM 12) Discrete resistors and resistor box Part 1 – Finding IRL 1) Connect the circuit as shown in Figure 4-3 with the same values of resistors (using color resistor table in Appendix B-1). Fill the measured values of the resistors in table 4-1. Table 4-1 R1 R2 R3 R4 2) Connect the circuit shown in Figure 4-3, adjust V1 = 10 V and V2 = 12 V using DMM. 3) Measure I. I= mA Part 2: Calculating I using Thevenin’s Circuit A) Finding VTH Remove RL from the circuit and measure VTH = Vxy VTH = V B) Finding RTH Remove RL and replace it with a short circuit wire. Measure ISC. ISC = mA 33 Calculate RTH RTH = KΩ Q2: Using Thevenin Equivalent Circuit, calculate IRL and compare it with the value in part 1. IRL = mA Part 3: Maximum Power Transfer RTH I + RL VTH - Figure 4-5: Circuit Diagram Let VTH = 12 V and RTH = 1.5 K. Connect the circuit as shown in Figure 4-5, where RL is a resistor box. Vary RL with the values of table 4-2. Fill table 4-2. Table 4-2 RL () PRL = I2*RL I 200 1000 1500 2500 4000 Q3: From table 4-2, plot PRL versus RL. What is the value of RL for maximum power. Comment? RL = KΩ PRL MAX = 34 W Pre-Lab Report 1) PSpice Simulation of Part 1 I= mA VTH = V Simulation of Part 2 35 Simulation of Finding RTH ISC = mA KΩ RTH = I= mA Data Sheet: Part 1 R1 R2 R3 Theoretical Measured I Theoretical (PSpice) Measured Part 2 Vth Theoretical (PSpice) Measured ISC Theoretical (PSpice) Measured 36 R4 Part 3 Table 4-2 PRL = I2*RL I RL () Theoretical Practical 200 500 1000 1500 2500 PRL MAX = W RL for maximum power= KΩ 37 Theoretical Practical