Evaluation Board Manual

advertisement

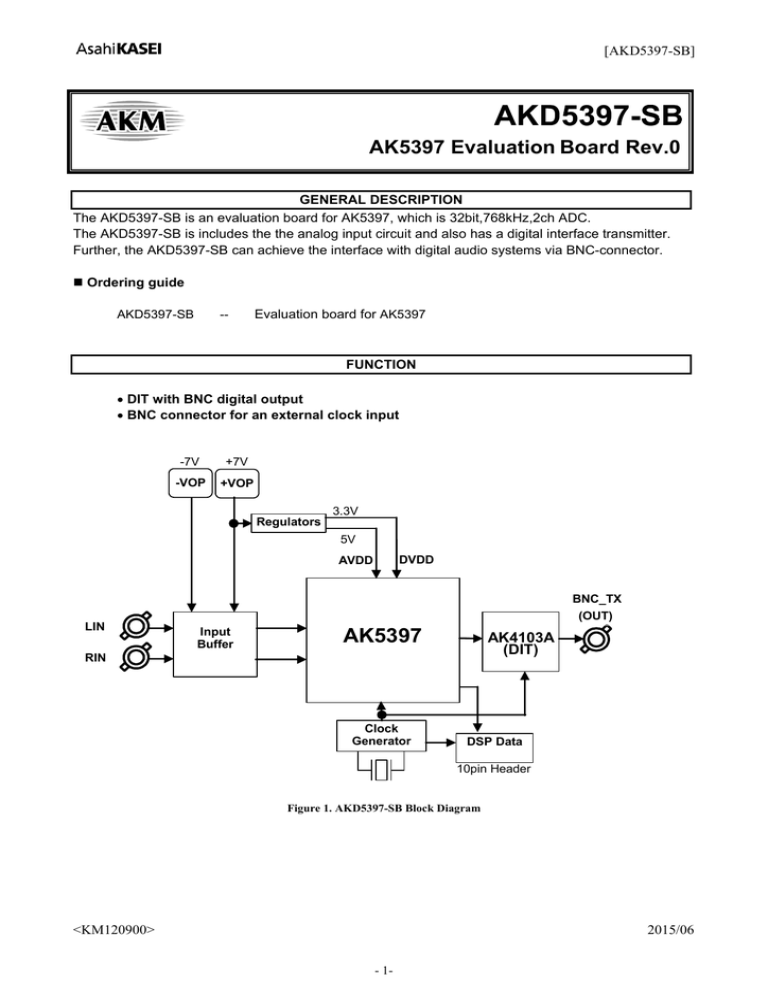

[AKD5397-SB] AK5397 Evaluation Board Rev.0 GENERAL DESCRIPTION The AKD5397-SB is an evaluation board for AK5397, which is 32bit,768kHz,2ch ADC. The AKD5397-SB is includes the the analog input circuit and also has a digital interface transmitter. Further, the AKD5397-SB can achieve the interface with digital audio systems via BNC-connector. Ordering guide AKD5397-SB -- Evaluation board for AK5397 FUNCTION DIT with BNC digital output BNC connector for an external clock input -7V +7V -VOP +VOP Regulators 3.3V 5V DVDD AVDD LIN BNC_TX (OUT) Input Buffer AK5397 AK4103A (DIT) RIN Clock Generator DSP Data 10pin Header Figure 1. AKD5397-SB Block Diagram <KM120900> 2015/06 - 1- [AKD5397-SB] Evaluation Board Diagram Board Diagram T2 T3 J203 J300 J501 J502 J400 J500 T1 SW301 J201 U2 U1 J200 SW300 SW400 PORT2 SW401 PORT1 J202 Figure 2. AKD5397-SA Board Diagram Description (1) U1 ( AK5397 ) 32bit,768kHz,2ch A/D Converter. (2) J200,J201 ( Analog data ) Cannon connector : Differential Analog Input (3) J300 ( Digital data ) BNC Connector : Digital Output. (4) J500, J501, J502 ( Power supply ) Power Supply Connector. (5) PORT1 ( pin header ) Pin header for evaluation (MCLK, BICK, LRCK). (6) PORT2 ( Digital Data ) Pin header for evaluation (SDTO1,SDTO2,TDMIN1,TDMIN2). (7) U2 ( AK4103A ) AK4103A has DIT. Transports output data from AK5397. (8) SW400 ( Toggle switch ) Toggle type-switch PDN for AK5397. “H” : PDN = High “L” : PDN = Low (9) SW401 ( Toggle switch ) Toggle type-switch PDN for AK4103A. “H” : PDN = High “L” : PDN = Low <KM120900> 2015/06 - 2- [AKD5397-SB] (10) SW300,SW301 ( Dip switch ) DIP type-switch for AK5397, AK4103A. ( Table2.-Table6. ) (11) J203,J202 ( Analog data ) BNC Connector : Single-ended Analog Input. (12) J400 ( MCLK external input ) BNC Connector : External Clock Input (MCLK). (13) T1, T2, T3 Regulator for AK5397, AK4103A, Logic Circuit. <KM120900> 2015/06 - 3- [AKD5397-SB] Evaluation Board Manual Operation sequence [1] Power supply line settings [2] Evaluation modes [2-1] Slave Mode (2-1-1) A/D evaluation using DIT function of AK4103A (2-1-2) Feeding all clocks from PORT1 (CLOCK) (2-1-3) Input/Output digital data from PORT2 (DATA) [2-2] Master Mode (2-2-1) A/D evaluation using DIT function of AK4103A (2-2-2) Feeding all clocks from PORT1 (CLOCK) (2-2-3) Input/Output digital data from PORT2 (DATA) [3] DIP switches settings [4] Clock / Data format settings [5] Toggle switches settings [6] Analog input Circuit <KM120900> 2015/06 - 4- [AKD5397-SB] [1] Power supply line settings (1) Power supply settings : Used the regulator (T1,T2,T3) <Default> Set up the power supplied lines : * Each supply line should be distributed from the power supply unit. Name Color Setting (Typ) J500(+7V) Green +7V For Op-amp and Regulator J501(-7V) Blue -7V For Op-amp and Regulator J502(VSS) Black 0V Ground Table 1-1. Comments Power supply line setting ( default : used the regulator ) (2) About short resistance for power supply : The roles of the short resistance for each power supply supplied from the regulator are as follows. Connection of the short resistance for power supply : Name Processing (Resistance) Name Comments (power supply) R510 Short AVDD1 AVDD for AK5397 R500 Short VBIAS Bias for Op-amp R511 Short VCC1 VCC for AK4103A and Logic IC R501 Short VCC2 Spare terminal VCC R512 Short DVDD1 VDD for AK5397 and Logic IC R502 Short DVDD2 VDD for DIP SW Table 1-2. Short resistance for power supply (Default : Short) <KM120900> 2015/06 - 5- [AKD5397-SB] [2] Evaluation modes [2-1] Slave Mode (2-1-1) A/D evaluation using DIT function of AK4103A *J300 (BNC_TX) used. DIT generates audio bi-phase signal from received data and which is output throurh BNC connector (BNC_TX). It is possible to connect AKM’s D/A converter evaluation boards and the digital-amplifier through the BNC connector. *Nothing should be connected to PORT1 (CLOCK), PORT2 (DATA). *In case of using external clock (MCLK) through a BNC connector (J400), short R423(EXT) and R422 by 0ohm resistance, and open R421 (XTL). *In case of default setting, SDTO1 of AK5397 output data is output through J300 (BNC_TX). In case of short R442(SDTO) by 0ohm resistance and open R441(SDTO), SDTO2 of AK5397 output data is output through J300 (BNC_TX). (2-1-2) Feeding all clocks from PORT1 (CLOCK) *Under the following set-up, all external clocks (MCLK, BICK, LRCK) can be fed through PORT1 (CLOCK). Short R440(MCLK), R438(BICK), R436(LRCK) by 0ohm resistance. Open R439(MCLK), R437(BICK), R435(LRCK). (2-1-3) Input/Output digital data from PORT2 (DATA) *The A/D converted data is output from SDTO1, SDTO2 of PORT2 (DATA). *IN case of using digital data through TDMIN1 pin, TDMIN2 pin of AK5397, digital data is input through TDMIN1 or TDMIN2 of PORT2 (DATA). [2-2] Master Mode (2-2-1) A/D evaluation using DIT function of AK4103A *Signals (BICK, LRCK) output from AK5397 used. Open R437 and R438 (BICK), R435 and R436 (LRCK). *J300 (BNC_TX) used. DIT generates audio bi-phase signal from received data and which is output throurh BNC connector (BNC_TX). It is possible to connect AKM’s D/A converter evaluation boards and the digital-amplifier through the BNC connector. *Nothing should be connected to PORT1 (CLOCK), PORT2 (DATA). *In case of using external clock (MCLK) through a BNC connector (J400), short R423(EXT) and R422 by 0ohm resistance, and open R421 (XTL). *In case of default setting, SDTO1 of AK5397 output data is output through J300 (BNC_TX). In case of short R442(SDTO) by 0ohm resistance and open R441(SDTO), SDTO2 of AK5397 output data is output through J300 (BNC_TX). (2-2-2) Feeding all clocks from PORT1 (CLOCK) *Under the following set-up, the external clock (MCLK) can be fed through PORT1 (CLOCK). Short R440(MCLK) by 0ohm resistance. Open R439(MCLK). (2-2-3) Input/Output digital data from PORT2 (DATA) *The A/D converted data is output from SDTO1, SDTO2 of PORT2 (DATA). *IN case of using digital data through TDMIN1 pin, TDMIN2 pin of AK5397, digital data is input through TDMIN1 or TDMIN2 of PORT2 (DATA). <KM120900> 2015/06 - 6- [AKD5397-SB] [3] DIP switches settings [SW300] (MODE): Evaluation Mode setting for AK5397 and AK4103A *ON=”H”, OFF=“L” No. Name OFF (“L”) ON (“H”) Default 1 HPFE HPF OFF HPF ON ON (“H”) 2 CKS0 ON (“H”) Table 3-1 3 CKS1 OFF (“L”) 4 CKS2 OFF (“L”) 5 DIT0 ON (“H”) Table 4 6 DIT1 ON (“H”) 7 ― N/A N/A OFF (“L”) 8 ― N/A N/A OFF (“L”) Table 2. Mode setting M_SN CKS2 CKS1 CKS0 L L L L L H L H L L H H H L L H L H H H L L H H L L L H L H L H L L H H H L L L H H L H H H H H L H MCLK BICK Sampling 256fs 64fs≦BICK≦128fs Normal Speed Mode (8kHz≦fs≦48kHz) 256fs Table3-2 64fs Auto Setting Mode Double Speed Mode Default (48kHz≦fs≦96kHz) 128fs 64fs Quad Speed Mode (96kHz≦fs≦192kHz) 64fs 64fs Octal Speed Mode (fs=384kHz) 32fs 32fs N/A N/A 256fs 512fs 256fs N/A N/A 64fs 64fs 64fs Hex Speed Mode (fs=768kHz) N/A N/A Normal Speed Mode (8kHz≦fs≦48kHz) Double Speed Mode (48kHz≦fs≦96kHz) 128fs 64fs Quad Speed Mode (96kHz≦fs≦192kHz) 64fs 64fs Octal Speed Mode 32fs 32fs Hex Speed Mode N/A N/A N/A N/A (fs=384kHz) (fs=768kHz) N/A N/A Table 3-1. MCLK frequency setting for AK5397 <KM120900> 2015/06 - 7- [AKD5397-SB] MCLK BICK fs 512fs 256fs 128fs 64fs 32fs 64fs≦BICK≦128fs 64fs 64fs 64fs 32fs Normal Speed Mode (8kHz≦fs≦48kHz) Double Speed Mode (48kHz≦fs≦96kHz) Quad Speed Mode (96kHz≦fs≦192kHz) Octal Speed Mode (fs = 384kHz) Hex Speed Mode (fs = 768kHz) Table 3-2. MCLK / BICK frequency setting for AK5397 (Auto Setting Mode: Slave Mode) Mode DIT1 DIT0 MCLK fs 28k 216kHz 28k 108kHz 28k 54kHz 28k 54kHz Table 4. MCLK frequency setting for AK4103A 0 1 2 3 L L H H L H L H 128fs 256fs 384fs 512fs Default [SW301] (MODE): Evaluation Mode setting for AK5397 and AK4103A *ON=“H”, OFF=“L” No. Name OFF (“L”) ON (“H”) Default 1 2 3 4 5 6 7 8 MONO TDM0 TDM1 M_SN DIF SDFIL SDM1 SDM2 Stereo Mode Mono Mode OFF (“L”) OFF (“L”) OFF (“L”) OFF (“L”) OFF (“L”) OFF (“L”) OFF (“L”) OFF (“L”) Table 6 Slave Mode MSB justified Short Delay Normal Output Normal Output Master Mode I S Compatible Minimum Phase “L” output “L” output 2 Table 5. Mode setting TDM1 TDM0 Mode L L H H L H L H Normal TDM256 N/A TDM128 Default Table 6. TDM Mode setting for AK5397 <KM120900> 2015/06 - 8- [AKD5397-SB] [4] Clock / Data format settings (1) Settings of Clocks (BICK, LRCK) Clock speed settings of BICK, LRCK can be set change by switching CLK1, CLK2. BICK fs MCLK R431 R432 R433 R434 (MCLK/8) (MCLK/4) (MCLK/2) (MCLK/1) 32fs 64fs 64fs 128fs 128fs 256fs 256fs 512fs 32fs 64fs 64fs 128fs 128fs 256fs 256fs 512fs 512fs = 24.576MHz 32fs 64fs 64fs 128fs 128fs 256fs 256fs 512fs 96kHz 256fs = 24.576MHz 32fs 64fs 128fs 256fs 192kHz 128fs = 24.576MHz - 32fs 64fs 128fs 384kHz 64fs = 24.576MHz - - 32fs 64fs 768kHz 32fs = 24.576MHz - - - 32fs 256fs = 8.192MHz 32kHz 512fs = 16.384MHz 44.1kHz 48kHz 256fs = 11.2896MHz 512fs = 22.5792MHz 256fs = 12.288MHz Default (R431=Short) Table 7. BICK Clock setting LRCK fs MCLK R426 R427 R428 R429 R430 (MCLK/512) (MCLK/256) (MCLK/128) (MCLK/64) (MCLK/32) 1fs 1fs - - - - 1fs 1fs - - - - 512fs = 24.576MHz 1fs 1fs - - - - 96kHz 256fs = 24.576MHz - 1fs - - - 192kHz 128fs = 24.576MHz - - 1fs - - 384kHz 64fs = 24.576MHz - - - 1fs - 768kHz 32fs = 24.576MHz - - - - 1fs 32kHz 44.1kHz 48kHz 256fs = 8.192MHz 512fs = 16.384MHz 256fs = 11.2896MHz 512fs = 22.5792MHz 256fs = 12.288MHz Default (R426=Short) Table 8. LRCK Clock setting <KM120900> 2015/06 - 9- [AKD5397-SB] (2) Settings of Data Format (SDTO) Audio Interface Format settings of SDTO can be set change by switching TDM1, TDM0, M/SN, DIF. Mode 0 1 2 3 4 5 6 7 8 9 10 11 12 Normal TDM1 L TDM0 L M/SN DIF L L H L H L H L H L H L H N/A (Slave) H (Master) L TDM256 L H (Slave) H (Master) L TDM128 H H (Slave) H (Master) N/A H L N/A SDTO 32bit, MSB justified 32bit, I2S Compatible 32bit, MSB justified 32bit, I2S Compatible 32bit, MSB justified 32bit, I2S Compatible 32bit, MSB justified 32bit, I2S Compatible 32bit, MSB justified 32bit, I2S Compatible 32bit, MSB justified 32bit, I2S Compatible N/A LRCK I/O H/L L/H H/L L/H ↑ ↓ ↑ ↓ ↑ ↓ ↑ ↓ N/A I I O O I I O O I I O O N/A BICK I/O Default I Table 3-1 I O O 256fs I 256fs I 256fs 256fs 128fs 128fs 128fs 128fs N/A O O I I O O N/A Table 9. Audio Interface Format setting for AK5397 <KM120900> 2015/06 - 10- [AKD5397-SB] [5] Toggle switches settings Up=”H”, Down=”L” [SW400] ( Power Down (PDN) for AK5397): Power Down (PDN) Switch for AK5397 Reset AK5397 (U1) once by brining SW400 to “L” once upon power-up. Keep “H” when AK5397 is in use; keep “L” when AK5397 is not in use. [SW401] ( Power Down (PDN) for AK4103A): Power Down (PDN) Switch for AK4103A Reset AK4103A (U2) once by brining SW401 to “L” once upon power-up. Keep “H” when AK4103A is in use; keep “L” when AK4103A is not in use. <KM120900> 2015/06 - 11- [AKD5397-SB] [6] Analog input Circuit Cannon Connectors (J200,J201) : Differential analog input signals for AK5397 1) Analog input Circuit 1 : Op-amp = LME49990 1.0k 1.0k Analog In (Single) 300 VP+ open + 8.5Vpp Vin+ 220µ + 910 Bias VPLME49990 Analog In Vin+/(Differential) VA+ Bias 10µ VA=+5V 2.80Vpp AK5397 AIN+ 33n 5 33n 300 220µ + 910 Vin0.01µ 5 XLR open + 100 VPLME49990 +/-17.11Vpp 1.1k 680 VP+ + VP+ - 100 5 + Bias VP=15V VPLME49990 5 2.80Vpp AK5397 AIN33n Figure 3. Analog Input Circuit 1 (Op-amp : LME49990) <KM120900> 2015/06 - 12- [AKD5397-SB] Measurement Results [Measurement condition] ・Measurement unit : Audio Precision, SYS-2722 ・MCKI : 512fs/256fs/128fs (24.576MHz ) ・BICK : 64fs ・fs : 48kHz / 96kHz / 192kHz ・Bit : 24bit ・Measurement Mode : ADC @ Slave Mode ・Power Supply : VOP+(15V)=7V, GND AVDD=5.0V (Regulator), DVDD=3.3V (Regulator) ・Input Frequency ・Measurement Frequency : 1kHz : 20 ~ 20kHz @48kHz / 20~40kHz @96kHz / 20~80kHz @192kHz ・Temperature : Room [Measurement Results] 1. Stereo ADC (Differential Inputs) Result Unit Lch Rch fs = 48kHz (-1dBFS) 104.2 104.0 dB fs = 96kHz (-1dBFS) 103.8 103.7 dB fs = 192kHz (-1dBFS) 103.6 103.6 dB DR fs = 48kHz (-60dBFS, A-Weighted) 126.0 125.6 dB S/N fs = 48kHz (A-weighted) 126.1 126.8 dB Stereo ADC : AINL/R => ADC => SDTO1 S/(N+D) 2. Mono ADC (Differential Inputs) Result Unit Lch Rch fs = 48kHz (-1dBFS) 103.7 103.6 dB fs = 96kHz (-1dBFS) 103.5 103.5 dB fs = 192kHz (-1dBFS) 103.4 103.4 dB DR fs = 48kHz (-60dBFS, A-Weighted) 128.9 128.8 dB S/N fs = 48kHz (A-weighted) 129.4 129.6 dB Mono ADC : AINL/R => ADC => SDTO1 S/(N+D) <KM120900> 2015/06 - 13- [AKD5397-SB] [Plots] fs = 48 kHz AK5397 FFT (-1dBFS Input) AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=512fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 -70 d B F S -80 -90 -100 -110 -120 -130 -140 -150 -160 -170 -180 20 50 100 200 500 1k 2k 5k 10k 20k Hz Figure 4. FFT (-1dBFS Input) AK5397 FFT ( -60dBFS Input) AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=512fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 -70 d B F S -80 -90 -100 -110 -120 -130 -140 -150 -160 -170 -180 20 50 100 200 500 1k 2k 5k 10k 20k Hz Figure 5. FFT (-60dBFS Input) <KM120900> 2015/06 - 14- [AKD5397-SB] fs = 48 kHz AK5397 FFT ( No Signal Input) AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=512fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 -70 d B F S -80 -90 -100 -110 -120 -130 -140 -150 -160 -170 -180 20 50 100 200 500 1k 2k 5k 10k 20k Hz Figure 6. FFT (No Signal Input) AK5397 THD+N vs. Input Level AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=512fs, fin=1kHz -70 -75 -80 -85 -90 -95 -100 d B F S -105 -110 -115 -120 -125 -130 -135 -140 -145 -150 -140 -130 -120 -110 -100 -90 -80 -70 -60 -50 -40 -30 -20 -10 +0 dBr Figure 7. THD+N vs. Input Level <KM120900> 2015/06 - 15- [AKD5397-SB] fs = 48 kHz AK5397 THD+N vs. Input Frequency AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=512fs, -1dBFS Input -70 -75 -80 -85 -90 -95 -100 d B F S -105 -110 -115 -120 -125 -130 -135 -140 -145 -150 20 50 100 200 500 1k 2k 5k 10k 20k Hz Figure 8. THD+N vs. Input Frequency AK5397 Linearity AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=512fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 d B F S -70 -80 -90 -100 -110 -120 -130 -140 -150 -160 -160 -140 -120 -100 -80 -60 -40 -20 +0 dBr Figure 9. Linearity <KM120900> 2015/06 - 16- [AKD5397-SB] fs = 48 kHz AK5397 Frequency Response AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=512fs, -1dBFS input +0 -0.1 -0.2 -0.3 -0.4 -0.5 -0.6 -0.7 -0.8 d B F S -0.9 -1 -1.1 -1.2 -1.3 -1.4 -1.5 -1.6 -1.7 -1.8 -1.9 -2 20 50 100 200 500 1k 2k 5k 10k 20k Hz Figure 10. Frequency Response AK5397 Crosstalk AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=512fs, -1dBFS Input -80 -85 -90 -95 -100 -105 -110 -115 -120 -125 d B -130 -135 -140 -145 -150 -155 -160 -165 -170 -175 -180 20 50 100 200 500 1k 2k 5k 10k 20k Hz Figure 11. Crosstalk <KM120900> 2015/06 - 17- [AKD5397-SB] fs = 96 kHz AK5397 FFT (-1dBFS Input) AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=256fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 -70 d B F S -80 -90 -100 -110 -120 -130 -140 -150 -160 -170 -180 20 50 100 200 500 1k 2k 5k 10k 20k 40k Hz Figure 12. FFT (-1dBFS Input) AK5397 FFT ( -60dBFS Input) AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=256fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 -70 d B F S -80 -90 -100 -110 -120 -130 -140 -150 -160 -170 -180 20 50 100 200 500 1k 2k 5k 10k 20k 40k Hz Figure 13. FFT (-60dBFS Input) <KM120900> 2015/06 - 18- [AKD5397-SB] fs =96 kHz AK5397 FFT ( No Signal Input) AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=256fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 -70 d B F S -80 -90 -100 -110 -120 -130 -140 -150 -160 -170 -180 20 50 100 200 500 1k 2k 5k 10k 20k 40k Hz Figure 14. FFT (No Signal Input) AK5397 THD+N vs. Input Level AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=256fs, fin=1kHz -70 -75 -80 -85 -90 -95 -100 d B F S -105 -110 -115 -120 -125 -130 -135 -140 -145 -150 -140 -130 -120 -110 -100 -90 -80 -70 -60 -50 -40 -30 -20 -10 +0 dBr Figure 15. THD+N vs. Input Level <KM120900> 2015/06 - 19- [AKD5397-SB] fs = 96 kHz AK5397 THD+N vs. Input Frequency AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=256fs, -1dBFS Input -70 -75 -80 -85 -90 -95 -100 d B F S -105 -110 -115 -120 -125 -130 -135 -140 -145 -150 20 50 100 200 500 1k 2k 5k 10k 20k 40k Hz Figure 16. THD+N vs. Input Frequency AK5397 Linearity AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=256fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 d B F S -70 -80 -90 -100 -110 -120 -130 -140 -150 -160 -160 -140 -120 -100 -80 -60 -40 -20 +0 dBr Figure 17. Linearity <KM120900> 2015/06 - 20- [AKD5397-SB] fs = 96 kHz AK5397 Frequency Response AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=256fs, -1dBFS Input +0 -0.1 -0.2 -0.3 -0.4 -0.5 -0.6 -0.7 -0.8 d B F S -0.9 -1 -1.1 -1.2 -1.3 -1.4 -1.5 -1.6 -1.7 -1.8 -1.9 -2 20 50 100 200 500 1k 2k 5k 10k 20k 40k Hz Figure 18. Frequency Response AK5397 Crosstalk AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=256fs, -1dBFS Input -80 -85 -90 -95 -100 -105 -110 -115 -120 -125 d B -130 -135 -140 -145 -150 -155 -160 -165 -170 -175 -180 20 50 100 200 500 1k 2k 5k 10k 20k 40k Hz Figure 19. Crosstalk <KM120900> 2015/06 - 21- [AKD5397-SB] fs = 192 kHz AK5397 FFT (-1dBFS Input) AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=128fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 -70 d B F S -80 -90 -100 -110 -120 -130 -140 -150 -160 -170 -180 20 50 100 200 500 1k 2k 5k 10k 20k 50k 80k Hz Figure 20. FFT (-1dBFS Input) AK5397 FFT ( -60dBFS Input) AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=128fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 -70 d B F S -80 -90 -100 -110 -120 -130 -140 -150 -160 -170 -180 20 50 100 200 500 1k 2k 5k 10k 20k 50k 80k Hz Figure 21. FFT (-60dBFS Input) <KM120900> 2015/06 - 22- [AKD5397-SB] fs =192 kHz AK5397 FFT ( No Signal Input) AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=128fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 -70 d B F S -80 -90 -100 -110 -120 -130 -140 -150 -160 -170 -180 20 50 100 200 500 1k 2k 5k 10k 20k 50k 80k Hz Figure 22. FFT (No Signal Input) AK5397 THD+N vs. Input Level AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=128fs, fin=1kHz -70 -75 -80 -85 -90 -95 -100 d B F S -105 -110 -115 -120 -125 -130 -135 -140 -145 -150 -140 -130 -120 -110 -100 -90 -80 -70 -60 -50 -40 -30 -20 -10 +0 dBr Figure 23. THD+N vs. Input Level <KM120900> 2015/06 - 23- [AKD5397-SB] fs = 192 kHz AK5397 THD+N vs. Input Frequency AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=128fs, -1dBFS Input -70 -75 -80 -85 -90 -95 -100 d B F S -105 -110 -115 -120 -125 -130 -135 -140 -145 -150 20 50 100 200 500 1k 2k 5k 10k 20k 50k 80k Hz Figure 24. THD+N vs. Input Frequency AK5397 Linearity AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=128fs, fin=1kHz +0 -10 -20 -30 -40 -50 -60 d B F S -70 -80 -90 -100 -110 -120 -130 -140 -150 -160 -160 -140 -120 -100 -80 -60 -40 -20 +0 dBr Figure 25. Linearity <KM120900> 2015/06 - 24- [AKD5397-SB] fs = 192 kHz AK5397 Frequency Response AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=128fs, -1dBFS Input +0 -0.1 -0.2 -0.3 -0.4 -0.5 -0.6 -0.7 -0.8 d B F S -0.9 -1 -1.1 -1.2 -1.3 -1.4 -1.5 -1.6 -1.7 -1.8 -1.9 -2 20 50 100 200 500 1k 2k 5k 10k 20k 50k 80k Hz Figure 26. Frequency Response AK5397 Crosstalk AVDD=5.0V, DVDD=3.3V, VREFL+/-=VREFR+/-=5.0V/VSS, MCLK=128fs, -1dBFS Input -80 -85 -90 -95 -100 -105 -110 -115 -120 -125 d B -130 -135 -140 -145 -150 -155 -160 -165 -170 -175 -180 20 50 100 200 500 1k 2k 5k 10k 20k 50k 80k Hz Figure 27. Crosstalk <KM120900> 2015/06 - 25- [AKD5397-SB] REVISION HISTORY Date (YY/MM/DD) 15/06/01 Manual Revision KM120900 Board Revision 0 Reason Page First edition - <KM120900> Contents 2015/06 - 26- [AKD5397-SB] IMPORTANT NOTICE 0. Asahi Kasei Microdevices Corporation (“AKM”) reserves the right to make changes to the information contained in this document without notice. When you consider any use or application of AKM product stipulated in this document (“Product”), please make inquiries the sales office of AKM or authorized distributors as to current status of the Products. 1. All information included in this document are provided only to illustrate the operation and application examples of AKM Products. AKM neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of AKM or any third party with respect to the information in this document. You are fully responsible for use of such information contained in this document in your product design or applications. AKM ASSUMES NO LIABILITY FOR ANY LOSSES INCURRED BY YOU OR THIRD PARTIES ARISING FROM THE USE OF SUCH INFORMATION IN YOUR PRODUCT DESIGN OR APPLICATIONS. 2. The Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact, including but not limited to, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for the above use unless specifically agreed by AKM in writing. 3. Though AKM works continually to improve the Product’s quality and reliability, you are responsible for complying with safety standards and for providing adequate designs and safeguards for your hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of the Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. 4. Do not use or otherwise make available the Product or related technology or any information contained in this document for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). When exporting the Products or related technology or any information contained in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. The Products and related technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. 5. Please contact AKM sales representative for details as to environmental matters such as the RoHS compatibility of the Product. Please use the Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. AKM assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations. 6. Resale of the Product with provisions different from the statement and/or technical features set forth in this document shall immediately void any warranty granted by AKM for the Product and shall not create or extend in any manner whatsoever, any liability of AKM. 7. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of AKM. <KM120900> 2015/06 - 27- 5 4 3 2 1 AVDD1 R120 3 0 4 VSS 5 HPFE 6 CKS0 7 CKS1 8 CKS2 R100 PDN1 VREFR- + C106 10u C107 0.1u 34 35 VREFR+ 36 + 0 C108 10u C110 0.1u AVSS 37 AVDD 39 VCOM 40 41 AVDD 42 AVSS 43 TOUT R108 0 RIN+ 9 PDN LIN- RIN- TEST1 TEST2 BVSS BVSS HPFE MONO CKS0 TDM1 CKS1 TDM0 CKS2 TDMIN2 33 RIN_P0 PDN TDMIN1 0.033u 32 31 RIN_N0 R121 0 C VSS 30 VSS 29 MONO 28 TDM1 27 TDM0 26 TDMIN2 R107 51 TDMIN2_VD 25 TDMIN1 R106 51 TDMIN1_VD 100p R101 R102 R103 R104 R105 330 220 51 51 51 MCLK_VD BICK_VD LRCK_VD 24 C103 0.1u C104 + 10u 23 DVDD1 B M/SN VSS 22 DIF 21 SDFIL 20 SDM2 19 SDM1 18 17 13 BICK MCLK 12 OVF DVSS MCLK DVSS SDTO2 11 VSS SDTO2 16 0.1u DVDD SDTO1 10u DVDD SDTO1 15 C102 LRCK 10 C101 + LRCK 14 DVDD1 B 51 R122 open R123 0 R109 LIN+ BICK C130 VSS C105 2 VSS C111 10u C112 0.1u 0.033u LIN_N0 C VREFL+ 44 VREFL- C100 C113 10u C114 0.1u + 1 LIN_P0 VSS + C115 10u C116 0.1u U1 R110 0 D VSS 38 R111 0 VSS + VSS TOUT VSS TEST3 D M_SN DIF SDFIL SDM2 SDM1 SDTO1_VD SDTO2_VD OVF A A Title Size A3 - 285 4 3 Date: 2 AKD5397-SB Document Number Rev 0 AKD5397 Thursday, March 12, 2015 Sheet 1 1 of 5 5 4 3 2 1 VOP+ R230 1k U200 R200 2 1k 3 D 4 NC -IN V+ +IN OUT V- NC R205 300 C211 open 8 7 U201 6 R240 open 1 C205 220u 5 910 R203 AINLP 2 NC NC -IN V+ +IN OUT 8 D 7 + VOP- NC 2 1 J202 AIN_L LME49990 C202 0.1u C203 47u + 2 C201 0.1u 1 J200 AINL + R241 C250 100p 3 4 VOP- V- NC 6 R207 5.6 R210 5.6 100 LIN_P0 5 LME49990 AINLN C207 + VSS 3 VSS VSS BIASL1 C206 220u 3 1 + C200 47u R209 open 10u C208 0.1u C213 0.1u C214 + C217 0.033u 10u VSS VBIAS R206 300 C212 open R201 U202 1 1.1k BIASL1 R202 680 + 2 C251 100p BIASL1 C240 0.1u C204 10u 910 R204 3 4 VOP- NC NC -IN V+ +IN OUT V- NC 8 7 6 R208 R211 5.6 R212 5.6 100 LIN_N0 5 LME49990 C209 C VSS + 10u C210 0.1u C215 0.1u C216 + C C218 0.033u 10u VSS VOP+ R231 1k U203 R213 2 1k 3 4 NC -IN V+ +IN OUT V- NC open U204 6 R242 open 1 C224 220u 5 LME49990 C221 0.1u C222 47u + 2 C220 0.1u 1 + 910 R216 AINRP 2 R243 C252 100p BIASR1 C225 220u 3 4 VOP- NC NC -IN V+ +IN OUT 8 7 V- NC 6 R220 R222 5.6 R223 5.6 100 RIN_P0 5 B LME49990 AINRN C226 + VSS J201 AINR 3 3 1 VSS VSS 300 C230 7 + C219 47u B R218 8 + VOP- NC 2 1 J203 AIN_R open 10u C227 0.1u C232 0.1u C233 + C236 0.033u 10u VSS VBIAS R219 300 C231 open R214 U205 1 1.1k BIASR1 R215 680 + C223 10u 910 R217 BIASR1 C241 0.1u 2 C253 100p 3 4 VOP- NC NC -IN V+ +IN OUT V- NC 8 7 6 R221 R224 5.6 R225 5.6 100 RIN_N0 5 LME49990 C228 VSS + 10u C229 0.1u C234 0.1u C235 + 10u C237 0.033u VSS A A Title Size A3 - 295 4 3 Date: 2 AKD5397-SB Document Number Rev 0 Analog Input Thursday, March 12, 2015 Sheet 1 2 of 5 5 4 DVDD1 3 2 1 VCC1 U2 U300A 3 DIF D OVF 4 SDTO2_VD 5 6 7 SDTO1_VD DIT1 8 DIT0 9 10 1 2 11 12 -> B 1 A1 B1 A2 B2 A3 B3 A4 B4 A5 B5 A6 B6 A7 B7 A8 B8 VCCA VCCB DIR VCCB GND GND OE GND C300 DIF_VC 21 LED300 1 2 R300 20 19 1k VSS 2 SDTO2_VCPR4353K V1 U1 TRANS DIF2 24 23 17 PDN_VCB 3 MCLK_VC 4 SDTI_4103 5 BICK_4103 6 LRCK_4103 7 SDTO1_VC 16 DIT1_VC 15 DIT0_VC PDN DIF1 MCLK DIF0 SDTI TXP BICK TXN 22 J300 BNC_TX 14 20 R301 240 24 19 150 22 13 LRCK VSS 18 C306 C307 4 5 BICK_VD 6 7 8 9 10 1 M_SN 8 2 11 12 <-> B A1 B1 A2 B2 A3 B3 A4 B4 A5 B5 A6 B6 A7 B7 A8 B8 VCCA VCCB DIR VCCB GND OE GND GND C302 9 21 LRCK_VC FS0/CSN VDD FS1/CDTI CKS1 FS2/CCLK CKS0 FS3/CDTO BLS C1 ANS 19 BICK_VC 11 17 4 TDMIN2_VD 5 6 TDMIN1_VD 7 8 MCLK_VD 9 10 PDN1 1 2 11 12 12 15 VSS DIT0_VC 14 13 14 24 AK4103A VSS 23 22 13 HPFE CKS0 CKS1 CKS2 B DVDD2 A1 B1 A2 B2 A3 B3 A4 B4 A5 B5 A6 B6 A7 B7 A8 B8 VCCA VCCB DIR VCCB GND OE GND GND 21 SW300 20 TDMIN2_VC RP300 19 18 TDMIN1_VC 17 16 HPFE CKS0 CKS1 CKS2 DIT0 DIT1 1 2 3 4 5 6 7 8 9 MCLK_VC HPFE 1 CKS0 2 CKS1 3 CKS2 4 DIT0 5 DIT1 6 7 8 16 15 14 13 12 11 10 9 SW DIP-8 15 10k 14 PDN_VCA MONO TDM0 TDM1 M_SN DIF SDFIL SDM1 SDM2 VSS 24 23 22 DVDD2 13 RP301 SW301 1 2 3 4 5 6 7 8 9 C305 74LVC8T245 0.1u 15 <- B C304 A DIT1_VC 16 DIT0 DIT1 3 16 18 0.1u U302A VCC1 C 10 C303 0.1u 17 20 74LVC8T245 B VSS 0.1u 47u 0.1u 3 LRCK_VD VSS VSS + C C308 0.1u R302 23 74LVC8T245 U301A T300 DA-02F DIF_VC 21 C301 0.1u D VSS 18 0.1u VSS MONO TDM0 TDM1 M_SN DIF SDFIL SDM1 SDM2 MONO1 TDM0 2 TDM1 3 M_SN 4 DIF 5 SDFIL 6 SDM1 7 SDM2 8 16 15 14 13 12 11 10 9 A Title SW DIP-8 10k VSS 5 4 Size A3 - 303 Date: 2 Document Number AKD5397-SB Rev 0 DIT Thursday, March 12, 2015 Sheet 1 3 of 5 5 4 3 2 1 X1 24.576MHz D R402 D 1M U400 1 3 5 9 11 13 14 7 open C402 10p C403 10p C404 0.1u VSS 1A 2A 3A 4A 5A 6A VCC GND 1Y 2Y 3Y 4Y 5Y 6Y 2 4 6 8 10 12 XTL R421 0 MCLK_SOURCE 74HCU04 R422 open VSS VCC1 14 7 C405 J400 EXT C CLK/1 U401 4 3 2 1 10 11 12 13 0.1u 1PR 1CK 1D 1CLR 2PR 2CK 2D 2CLR 1Q 1Q 2Q 2Q 5 6 9 8 MCLK_2 XTE R420 MCLK_SOURCE MCLK_SOURCE CLK/2 VCC1 R424 0 U403 MCLK 10 11 open R425 16 C407 0.1u 8 VCC GND 74VHC74F CLK RST VDD VSS Q1 Q2 Q3 Q4 Q5 Q6 Q7 Q8 Q9 Q10 Q11 Q12 9 7 6 5 3 2 4 13 12 14 15 1 BICK1 BICK2 BICK3 LRTD1 LRTD2 LRCK1 LRCK2 LRCK3 CLK1 MCLK/512 MCLK/256 MCLK/128 MCLK/64 MCLK/32 R426 R427 R428 R429 R430 MCLK/8 MCLK/4 MCLK/2 CLK/1 R431 R432 R433 R434 0 LRCK_DIV open LRCK_P open open open CLK2 0 BICK_DIV open open open LRCK R435 R436 LRCK_4103 0 open BICK R437 R438 BICK_4103 0 open R407 51 BICK_VC BICK_P BICK_4103 C MCLK MCLK_SEL 0 open R408 51 R409 51 R410 51 SDTO1_P R411 51 SDTO1_VC SDTO2_P R412 51 SDTO2_VC MCLK_VC MCLK_P VSS R403 51 PORT1 MCLK BICK LRCK U402 PDN_VC1 R423 open LRCK_VC MCLK_SOURCE 74LV4040AD VSS 51 LRCK_4103 R439 R440 EXT R406 EXT 1 3 5 9 11 13 14 7 PDN_VC2 VSS C406 1A 2A 3A 4A 5A 6A VCC GND 0.1u 1Y 2Y 3Y 4Y 5Y 6Y 2 4 6 8 10 12 PDN_VCA PDN_VCA PDN_VCB PDN_VCB CLOCK VSS PORT2 TDMIN1_P TDMIN2_P TDMIN1 TDMIN2 SDTO1 SDTO2 74VHC14F TDMIN1_VC TDMIN2_VC DATA VSS R404 R405 VSS 100k VCC1 100k SDTO SDTO1_P R441 SDTO2_P R442 VCC1 0 open SDTI_4103 VSS B SW400 PDN 3 L 1 H 2 D400 HSU119 1 2 SW401 PDN 3 L 1 H 2 C400 0.1u R400 10k C401 0.1u R401 10k PDN_VC1 VSS B D401 HSU119 1 2 PDN_VC2 VSS A A Title Size A3 - 315 4 3 Date: 2 AKD5397-SB Document Number Rev 0 LOGIC Thursday, March 12, 2015 Sheet 1 4 of 5 5 4 3 +15V L500 1 2 1 0 2 VOP+ T1 ADM7150-50 D R520 C500 47u + C528 10u + C520 10u C521 1u C501 0.1u D VIN VREG EN VOUT REF BYP REF-SENSE GND 0 + C522 1u C523 1u C524 1u + C532 33u + C531 0.1u C525 10u C526 10u + C530 47u + C502 0.1u C527 10u C529 10u + C503 47u + R510 0 R500 0 AVDD1 VBIAS VSS -15V L501 1 0 J500 2 +15V VOP+15V C505 47u + C J501 VSS -15V C -15V J502 VSS VSS VOP+ IN C506 47u + GND T2 NJM78M05FA OUT C507 0.1u C508 0.1u C509 47u R511 0 R501 0 VCC1 + VCC2 VSS B B VCC2 IN C510 47u + GND T3 uPC29M33HF OUT C511 0.1u C512 0.1u C513 47u + R512 0 R502 0 DVDD1 DVDD2 VSS A A Title Size A3 - 325 4 3 Date: 2 AKD5397-SB Document Number Rev Power Supply Thursday, March 12, 2015 Sheet 1 5 0 of 5