Digital Integrated Circuits – A Design Perspective 2/e

advertisement

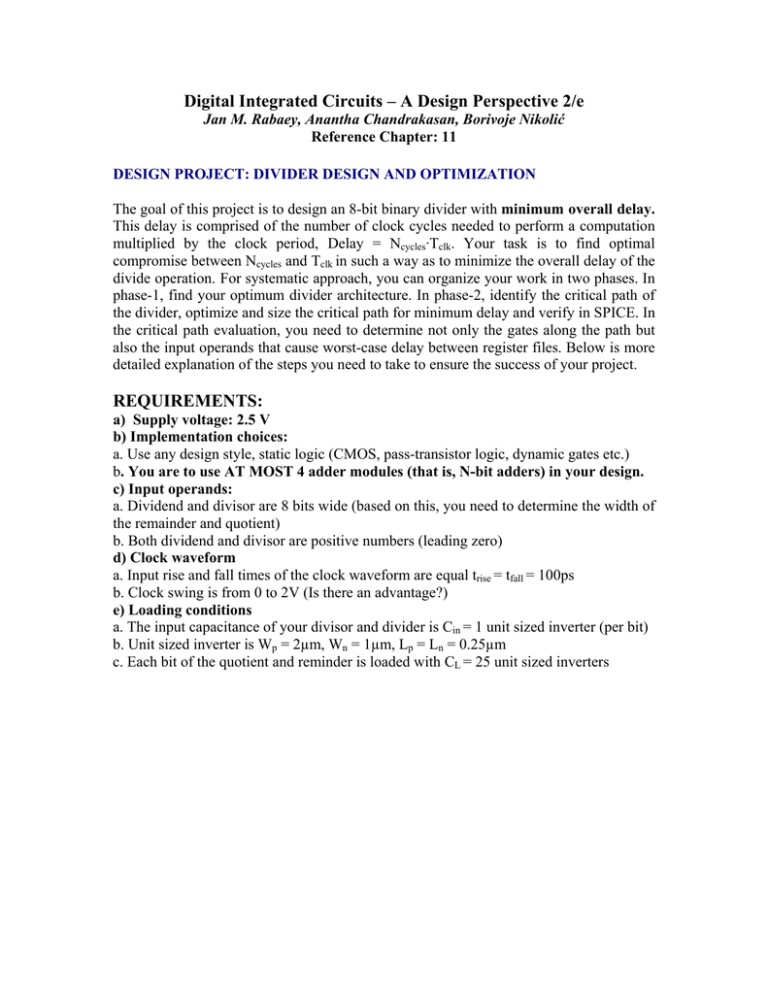

Digital Integrated Circuits – A Design Perspective 2/e Jan M. Rabaey, Anantha Chandrakasan, Borivoje Nikolić Reference Chapter: 11 DESIGN PROJECT: DIVIDER DESIGN AND OPTIMIZATION The goal of this project is to design an 8-bit binary divider with minimum overall delay. This delay is comprised of the number of clock cycles needed to perform a computation multiplied by the clock period, Delay = Ncycles·Tclk. Your task is to find optimal compromise between Ncycles and Tclk in such a way as to minimize the overall delay of the divide operation. For systematic approach, you can organize your work in two phases. In phase-1, find your optimum divider architecture. In phase-2, identify the critical path of the divider, optimize and size the critical path for minimum delay and verify in SPICE. In the critical path evaluation, you need to determine not only the gates along the path but also the input operands that cause worst-case delay between register files. Below is more detailed explanation of the steps you need to take to ensure the success of your project. REQUIREMENTS: a) Supply voltage: 2.5 V b) Implementation choices: a. Use any design style, static logic (CMOS, pass-transistor logic, dynamic gates etc.) b. You are to use AT MOST 4 adder modules (that is, N-bit adders) in your design. c) Input operands: a. Dividend and divisor are 8 bits wide (based on this, you need to determine the width of the remainder and quotient) b. Both dividend and divisor are positive numbers (leading zero) d) Clock waveform a. Input rise and fall times of the clock waveform are equal trise = tfall = 100ps b. Clock swing is from 0 to 2V (Is there an advantage?) e) Loading conditions a. The input capacitance of your divisor and divider is Cin = 1 unit sized inverter (per bit) b. Unit sized inverter is Wp = 2µm, Wn = 1µm, Lp = Ln = 0.25µm c. Each bit of the quotient and reminder is loaded with CL = 25 unit sized inverters Digital Integrated Circuits – A Design Perspective 2/e Jan M. Rabaey, Anantha Chandrakasan, Borivoje Nikolić References Chapters: 11 and 6 DESIGN PROJECT: 16-BIT ARITHMETIC LOGIC UNIT 1. IMPLEMENTATION AND CONSTRAINTS The goal of this project is to design the carry look-ahead adder for an ALU to be used in a high-performance or mobile microprocessor with a particular set of optimization criteria. Physical and electrical specifications and constraints: You are free to choose any supply voltage and logic swing up to 2.5 V. Make sure that you use the appropriate model when you perform any hand analysis. The propagation delay for static CMOS design is defined as the time interval between the 50% transition point of the inputs and the 50% point of the worst case output signal. Make sure you pick the worst-case condition and state EXPLICITLY in your report what that condition is. Each bit slice in the adder should accommodate 9 metal-5 busses and is 144λ (36 metal pitch) wide. Other circuits in the data path set this constraint. The goal is to minimize the delay, power and area of the design. Your delay should not exceed 12 fanout-of-4 (FO4) inverter delays. 2. SIMULATION Analyze the circuit by using SPICE to simulate the design and prove that it functions correctly. You will need to determine the input pattern that causes the worst-case propagation delay or energy consumption by analyzing your circuit schematic. 3. REPORT The quality of your report is as important as the quality of your design. One must sell the design by justifying all design decisions. Be sure to provide all relevant information. Digital Integrated Circuits – A Design Perspective 2/e Jan M. Rabaey, Anantha Chandrakasan, Borivoje Nikolić Reference Chapter: 12 DESIGN PROJECT: 32-bit 512-WORD RANDOM ACCESS MEMORY (RAM) The objective of this project is to design a multiple port (3 port at a minimum) RAM. Stored data access should be very flexible, allowing single-bit, nibble, byte, word and long-word accesses. a) Access time – Details of the RAM’s access time must be provided i.e. how access time is determined or measured, factors that could affect the this time etc. b) Power aware - memory accesses – must determine a method that would minimize power dissipation. c) How your design approach address the memory-microprocessor performance gap