A Low-Power Blocking-Capacitor-Free Charge

advertisement

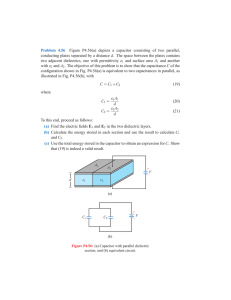

172 IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS, VOL. 1, NO. 3, SEPTEMBER 2007 A Low-Power Blocking-Capacitor-Free Charge-Balanced Electrode-Stimulator Chip With Less Than 6 nA DC Error for 1-mA Full-Scale Stimulation Ji-Jon Sit, Member, IEEE, and Rahul Sarpeshkar, Senior Member, IEEE Abstract—Large dc blocking capacitors are a bottleneck in reducing the size and cost of neural implants. We describe an electrode-stimulator chip that removes the need for large dc blocking capacitors in neural implants by achieving precise charge-balanced stimulation with 6 nA of dc error. For cochlear implant patients, this is well below the industry’s safety limit of 25 nA. Charge balance is achieved by dynamic current balancing to reduce the mismatch between the positive and negative phases of current to 0.4%, followed by a shorting phase of at least 1ms between current pulses to further reduce the charge error. On 6 and 9 V rails in a 0.7- m AMI high voltage process, the power consumption of a single channel of this chip is 47 W when biasing power is shared by 16 channels. + Index Terms—Biphasic current pulse, charge balancing, cochlear implants, electrode stimulation, neural implants. I. INTRODUCTION ANY biomedical implants currently convey information to nervous tissue by pulsatile current stimulation via an implanted microelectrode array. Examples of such implants include cochlear implants for the deaf, deep brain stimulators for Parkinson’s disease and retinal implants for the blind. In order to avoid irreversible electrochemical reactions leading to toxic by-product generation and eventual rejection of the implant, the pulse of current is typically made up of equal-sized negative and positive phases, with the goal of delivering no net charge through the electrode at the end of the pulse [1]. A perfect balance of zero net charge is difficult to achieve because current source and sink drivers will typically be mismatched by 1%–2% in the fabrication process even when great care is taken to ensure good matching in the layout and design. Studies have shown that a residual dc current of more than 100 nA is M Manuscript received June 29, 2007; revised October 23, 2007. This work was supported in part by the Packard Foundation and in part by the McGovern Institute for Neuro Technology (MINT) Program at the Massachusetts Institute of Technology, Cambridge. This paper was recommended by Associate Editor B.-D. Liu. J.-J. Sit was with the Analog VLSI and Biological Systems group at the Massachusetts Institute of Technology, Cambridge MA 02139 USA. He is now with Advanced Bionics Corporation, Sylmar, CA 91342 USA. R. Sarpeshkar is with the Analog VLSI and Biological Systems Group, Massachusetts Institute of Technology, Cambridge MA 02139 USA (e-mail: rahuls@mit.edu). Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/TBCAS.2007.911631 highly correlated with neural tissue damage [2], and since stimulation currents may need to be as high as 1 mA, a dc error of 0.01% is required. Some means of correcting any charge imbalance such that it presents 100 nA of dc error must therefore be implemented. One of the simplest solutions is to insert a large dc blocking capacitor with a typical shunt impedance of 5G in series with each electrode, to guarantee that negligible ( 1 nA) dc current will be able to flow across the electrode. However, to handle the clinical levels of charge that are required for stimulation, which in cochlear implant users has a median maximum comfortable level around 15 nC/phase [3], the size of a typical blocking capacitor must be 100 nF or larger so that the voltage drop across the capacitor does not add appreciably to the voltage compliance required for driving the electrode impedance. The size of a large (100 nF) blocking capacitor is hugely detrimental for implantable electronics, which is required to be small. Hence, safe levels of charge-balance that can be achieved by capacitor-free precision electronics is attractive. Since the cost of packaging is often a highly nonlinear function of the size of the implant, capacitor-free stimulation reduces cost as well. Several methods to achieve safely charge-balanced stimulation without using large dc blocking capacitors have been proposed. The first and perhaps simplest solution is to short out the electrode between current pulses [4]. The degree to which shorting is effective will depend on the initial charge imbalance, the electrode time constant of discharge, and the time available for discharge, set by the minimum inter-pulse interval. At stimulation rates as high as 2000 pulses-per-second (pps)/channel, shorting has been shown in clinical trials to achieve 100 nA dc error and safe long-term electrical stimulation [5], [6]. However, for reasons of patient safety, it is desirable to achieve charge balance which is significantly lower than 100 nA, and more precise than that achieved by shorting alone. We propose to do this by reducing the initial charge imbalance below the usual 1%–2% mismatch error, and getting closer to the level produced by dc blocking capacitors (on the order of 1 nA dc error). Besides shorting, the use of many tiny charge dumps from filling and emptying four small-sized (25 pF) blocking capacitors at 10 MHz has been proposed to reduce but not eliminate the blocking capacitors [7]. The technique was verified in a discrete implementation and simulated in CADENCE. Experimental evaluation of such ultrahigh-frequency stimulation in actual nerve environments that exhibit refractoriness and lowpass 1932-4545/$25.00 © 2007 IEEE SIT AND SARPESHKAR: LOW-POWER BLOCKING-CAPACITOR-FREE CHARGE-BALANCED ELECTRODE-STIMULATOR CHIP filtering is needed, especially to ensure that stimulation thresholds are not adversely affected. Noting that a large dc blocking capacitor functions as a charge integrator in feedback, an alternative method of charge balancing by charge-metering was proposed in [8], using a switched-capacitor integrator to integrate the current transacted across a small series resistor, and feeding back finely discretized charge packets to equilibrate the charge. As mentioned, the success of this technique then depends on the ability to minimize the charge-injection, noise, mismatch, leakage and other sampling errors to achieve highly precise and stable feedback, which can make for a power-hungry solution in practice. Another approach is to perform feedback current DAC calibration by sampling and holding a correction current to improve the matching of the current drivers [9]. This technique is similar to the dynamic current matching that we will employ, and achieves 90 nA of dc error, although in this work only current and not charge was matched. Finally, a feedback strategy to monitor any residual voltage on the electrode capacitance after each biphasic pulse and then apply stimulation currents until the residual voltage falls within a safe window ( 100 mV) was proposed in [10]. The precision of charge balance in this case is then a function of the electrode capacitance. In cochlear implants, a typical RC series impedance presented by an electrode can be as high as 10 k and 10 nF, which when driven with a 1mA pulse for 30 s/phase, requires at least V of output compliance on a single rail alone. Thus, it is crucial for any practical stimulator design to have sufficient voltage compliance to accommodate both the variability in electrode impedances and the variability in patient thresholds for comfortable stimulation levels [11]. The particular values used in our paper are of primary relevance to cochlear implants, but our technique is widely applicable to all biomedical implants that employ electrode stimulation. In this paper, we present a stimulator chip that employs dynamic current matching to reduce the typical 1–2% mismatch error because the same pMOS device which dynamically stores an nMOS current magnitude is later used to output the positive current pulse. As the dynamic current matching employed only provides 0.4% mismatch on its own, we follow the biphasic pulse with a shorting phase to achieve 6 nA of dc error. Finally, as in all implanted electronics, fail-safes have to be designed to protect the user from device failure. These are not considered in this paper but similar ideas from [7] and [12] in providing multiple redundant devices and voltage window checking can and should be implemented. This paper is organized as follows. Section II provides an introduction to the electrode model that we use in this paper. Section III presents our strategy for achieving precise charge balance. Section IV provides a feedback stability and noise analysis of the dynamic current-balance loop employed in the first phase of charge balancing. Measurements from our fabricated stimulator chip are presented in Section V. Section VI concludes the paper by summarizing our contributions. II. BACKGROUND ON ELECTRODE STIMULATION A. Electrode Modeling When addressing the problem of delivering balanced charge to an electrode, it is helpful to consider a basic circuit model that 173 Fig. 1. Simple circuit model for a typical electrode in a neural implant. will govern the electrical response of an electrode to biphasic current stimulation, shown in Fig. 1. In this simple model, is the solution spreading resistance, which is well determined by the resistivity of the fluid (set by ionic species in solution). is the double-layer capacitance, created by the accumulation of tightly adsorbed ions at the electrode surface and more loosely attracted ions in a diffuse layer behind it. Finally, is the Faradaic resistance, which is governed by diffusion of reactive species to the electrode for is indicated as a charge-transfer reactions. The resistance time-varying variable resistor because its value varies based on the dynamics of redox charge-transfer reactions occurring at the electrode. For the purposes of our analysis, we shall remains large M over the time scale of assume that a stimulation pulse s , and can therefore be neglected. is, however, the Current through the Faradaic resistance source of toxicity when there is no long-term charge balance. It is important to note that the values of and will vary depending on the material and geometry of the electrodes used. In the cochlear-implant devices that we chose as a reference for our design, the values of and have an upper bound of 20 k and 15 nF, respectively. B. Biphasic Pulse Generation In this work, we have chosen to implement only cathodic (negative) stimulation followed by anodic (positive) stimulation, in accordance with the conventional understanding that the negative pulse serves to depolarize the nerve and evoke action potentials by lowering the local extracellular potential relative to the membrane potential [13]. In contrast, the positive pulse tends to hyperpolarize the nerve and elevate sensory thresholds, but is required for charge balance. Most stimulation schemes therefore default to negative-first stimulation, which we also adopt here. In practice, many implants will also include a short interphase interval, i.e., a no-stimulus section between the negative and positive pulses, which can mitigate the hyperpolarizing effect from the trailing positive pulse. The interphase interval is also helpful in lowering crossbar conduction that wastes implant power. However, as simulations indicated that charge balance and power consumption were not significantly affected by the interphase interval in our design, it was omitted for simplification. 174 IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS, VOL. 1, NO. 3, SEPTEMBER 2007 Fig. 2. Timing diagram showing the order of operations. Gray blocks indicate a short delay. Fig. 3. (a) Sample phase in dynamic current balancing: SAMP1 and SAMP switches are closed. (b) Hold phase in dynamic current balancing: SAMP1 opens first, followed by SAMP, after which HOLD is closed. III. STRATEGY TO ACHIEVE PRECISE CHARGE BALANCE A. Overview Fig. 2 shows that the strategy we employ to achieve charge balance is two-fold: First, a dynamic current-balancing phase is performed to match a pMOS current source with an nMOS current sink. Second, after the biphasic pulse is generated, any residual charge error left on the electrode is shorted to ground. A biphasic current pulse is initiated by the falling edge of , shown in Fig. 2. The use an asynchronous trigger signal of Vox enables an asynchronous stimulation strategy, which encodes phase information for conveying better music and speech perception in cochlear implants [14]. Immediately after Vox arrives, a sample-and-hold (S&H) phase begins, shown as in Fig. 2. In this phase, the pMOS gate voltage required to support an nMOS current is sampled on a hold capacitor as shown in Fig. 3(a), and exploits the same basic idea as a dynamic current mirror [15]. and form a source-follower that diode-connects transistor M1, and is biased with enough current to drive at a to reasonable speed. The source-follower also level-shifts , which keeps the active-cascode formed a diode drop below and in saturation. After the circuit has settled, by is opened first. is then opened followed by the switch as shown in Fig. 3(b). This circuit closing of the of Fig. 3(b) incorporates a closed-loop switched-capacitor sample-and-hold [16] which attenuates noise and other disturby the gain of the loop around transconductor bances to . Errors due to the charge injection of the switch switch limit the precision of the sample and but not the hold [16]. The sampling phase preceding the hold phase is 4 clock cycles in duration, counting from the first rising clock edge . Then, a negative pulse is generated by closing the after OUTPUT NEG PULSE switch for 8 clock cycles. A positive pulse immediately follows the negative pulse via the closing of the OUTPUT POS PULSE switch for the next 8 clock cycles. Finally, after a small delay, the SHORT switch is closed to discharge any residual charge on the electrode. This scheme was chosen such that an asynchronous stimulation pulse would have a fixed latency of 4 clock cycles, and an additive variable . Since latency between 0–1 clock cycles after the arrival of 1 clock cycle is 4 s, the variable latency is a small fraction of the output pulsewidth. B. Low-Leakage Sample and Hold A conventional differential-mode closed-loop sample-andhold is shown in Fig. 4(a). Differential sampling allows for partial cancellation of charge injection errors of the SAMP1 switches in a closed-loop sample-and-hold. An additional improvement, shown in Fig. 4(b), includes the addition of a low-leakage sampling SIT AND SARPESHKAR: LOW-POWER BLOCKING-CAPACITOR-FREE CHARGE-BALANCED ELECTRODE-STIMULATOR CHIP 175 Fig. 4. (a) Conventional differential-mode closed-loop sample-and-hold: Vref is also sampled onto a capacitor. (b) Improved with a low-leakage switch. Fig. 5. Full circuit of differential, low-leakage analog storage within the dynamic current mirror, showing the use of diffusion-MOS (DMOS) devices with lightly doped drains (with up to 35 V of breakdown voltage, indicated by a thick drain terminal) to withstand large voltage drops where needed. The reference voltage Vref is buffered from Vref in by an identical Gmh transconductor and bypassed by a capacitor Cref , shown in gray. 0 switch adapted from the ultralow power analog storage cell of [17] and [18]. It works to minimize the switch leakage onto node by matching source and drain voltages (at ), thus nullifying leakage diffusion currents between source and drain [17], [18]. Note that this equality occurs automatically for the switch, but must be enforced explicitly for the switch, by switching its rightmost terminal to during the phase. The SPDT switch labeled enforces the equality. The “d” suffix indicates that its switching time is slightly delayed from the onset of sampling and holding, the reason for which is explained in the next section. C. Full Circuit Implementation The full circuit which implements the differential low-leakage analog storage within the dynamic current mirror is shown in Fig. 5. In order to achieve the high-voltage compliance necessary for electrode stimulation, DMOS devices available in the Europractice AMI 0.7- m 30 V (I2T30E) process were used to protect junctions that were exposed to large voltage drops. Additional circuit details that are required to improve the circuit’s settling time during its sampling phase are as follows. 176 IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS, VOL. 1, NO. 3, SEPTEMBER 2007 Fig. 6. Timing diagram showing the switching signals required for the various operations in dynamic current balancing. is low when the circuit is waiting for the input signal, and prebiases to start out near the positive rail. This initial condition improves the settling time, because at the onset of sampling, it is faster for the pMOS source-follower to pull rather than pull up on it. For the same reason, down on switch is closed for to pull up to the the rail when waiting for the trigger, as it is faster for to pull down on than to rely on a gradually stabilizing current sourced from to pull up on . The switch is closed to supply current to the active-cascode, whenever needs to source current. This saves power in the active-cascode by turning it off when it is not needed. is simply , just as . A third technique used to shorten the settling time during the sample phase was to delay the closure of all the feedback loops in Fig. 5 until turn-on transients had died out. Note that when the switch is closed, shoots upwards from the negative rail to equalize with near the positive rail, and thereby creates a large spike on the value of Iin. This spike, while short-lived, can cause all the feedback loops to take much longer to settle. Hence, and also are both delayed from switching until slightly after the onset of and , in order for the initial turn-on spike to die out before the feedback loops are closed. A timing diagram which summarizes these timing relationships is shown in Fig. 6. Select capacitor placement was found to be necessary for robust operation. A capacitor pF was added to bypass noise on . The capacitors and were both 1 pF and helped to stabilize the settling behavior of the active cascode. The capacitor pF was added to dampen a voltage spike on when switching from to mode. The capacitor pF was necessary to compensate the dynamic mirror feedback loop and improve its phase margin. The stability of this circuit is further described in the next section. The schematic of the transconductor is shown in Fig. 7. D. Shorting The shorting phase is implemented by a simple nMOS switch to ground that is sized to have a small on-resistance 2k , which is small in comparison with the electrode resistance. IV. FEEDBACK STABILITY AND NOISE ANALYSIS A simplified schematic of the dynamic mirror in closed-loop sampling is shown in Fig. 8. was not shown in earlier schematics because it is a parasitic capacitance, but is important for this analysis. We will make the simplifying assumption that the active cascode is fast and does not contribute to the loop dynamics, and only increases transistor by a factor of to the output resistance of the . The block diagram for this loop can then be written out in Fig. 9(a) and simplified to that of Fig. 9(b). A. Loop Bandwidth From Fig. 9(b), the transfer function can be treated as unity since the source-follower dynamics are comparatively fast. We can read off the loop bandwidth of to be , as the feedback term is only significant above crossover. A Bode plot of the forward transmission together with the inverse of the feedback transmission, is shown in Fig. 10. Since the minimum input current is set by our application at 1 A, we can expect an upper bound for one time constant to mV A ns. There may be some be at most 1 pF degradation in this value due to a lag effect (reduction in loop gain) from falling below unity, but the loop should still be fast enough to achieve full settling within the 4 clock cycles allotted, which is 16 s in our application. In general, since the settling is governed solely by , we can expect fast first-order settling. B. Loop Stability Since , it is indicated in Fig. 10 by the continuation of as a dotted line, having a right-half-plane (RHP) zero at . Since the RHP zero occurs after crossover by a factor of , it does not adversely affect loop stability as long as is not too small compared with . Thus, we can see that the loop should be stable with nearly 90 of phase margin. In addition to the usual pole-splitting compensation provided by , we can identify two additional sources of improvement SIT AND SARPESHKAR: LOW-POWER BLOCKING-CAPACITOR-FREE CHARGE-BALANCED ELECTRODE-STIMULATOR CHIP Fig. 7. Topology of the high-output impedance transconductor swing from to . Vref Vin 177 Gmh. The output is cascoded and protected with DMOS output devices to allow a wide voltage , which can be quite slow. added by the source follower at The capacitor helps by inserting a zero at to partially cancel this nondominant pole. Secondly, the large sampling capacitor , which is sized at 2 pF, would degrade phase margin if resistor in series with not for the zero introduced by the it. At high frequencies, rather than seeing the capacitive roll-off due to continue forever, the impedance of and flattens out at and hence inserts another zero at . The closed-loop sample-and-hold topology of Fig. 4 is therefore well suited to allow stable closed-loop sampling within the dynamic mirror. The use of pole-splitting compensation and the combination of zeroes at and allow the loop to be stable over a large range of input currents, down to the minimum value of A. C. Noise Performance Fig. 8. Simplified schematic of our dynamic mirror circuit in the sample phase. in the phase margin: Firstly, without , a nondominant pole is From the block diagram in Fig. 9(b), we see that noise sources and Iin experiences the full bandwidth of the loop from and have a frequency dependence just like Iin. However, noise sources from , and will be strongly attenuated at 178 IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS, VOL. 1, NO. 3, SEPTEMBER 2007 Fig. 9. (a) Block diagram of the dynamic mirror feedback loop. (b) Simplified block diagram containing unitless transfer functions within the loop. is defined as C=Gmh. Fig. 10. Bode plot of the closed loop transfer function G(s) // (1/H(s)) shaded in gray and the loop transmission L(s), which continues after G(s) as a dashed line. because of the large gain of at dc in their feedback path to . To understand this attenuation more clearly and over all frequencies, we can again draw the forward transmission together with the inverse of the feedback transmission , as shown in Fig. 11. The transmission can be observed to be the same as except without the zero at , and reveals the strong attenuation of at low frequencies. At higher frequencies, intersects with the rolloff from , hence is attenuated by the loop over all frethe noise appearing at quencies. Although current noise from does not inject directly into , it is capacitively coupled through , and has a highpass nature which further attenuates low frequency components. Hence, we can expect the noise contribution from the , , and sources to to be negligible compared to and injections into , reducing the effective number of noise sources in this circuit to only . SIT AND SARPESHKAR: LOW-POWER BLOCKING-CAPACITOR-FREE CHARGE-BALANCED ELECTRODE-STIMULATOR CHIP Fig. 11. Bode plot of G(s)==(1=H(s)) shaded in gray, showing the transfer function from Ibs and similar noise sources to Vp. The gain of g as A and the dominant time constant of (Cc + Cpo)A r is defined as . 179 1 A r is defined Estimating the noise from only two effective noise sources and referring it back to , we get where Fig. 12. Die photo of stimulator chip. pF mV pF At the highest current level, using a maximum of 1 mA/V, this sampled noise is converted to 75 nA in current noise. With a pulsewidth of 32 , the standard deviation in charge is then 2.4 pC, which is very small compared to the full-scale charge of 30 nC. This circuit is, therefore, a very low noise circuit, which is borne out by measurements presented in the next section. V. MEASUREMENTS A 2.3 mm 2.3 mm stimulator chip was fabricated by the Europractice IC fabrication service in an AMI 0.7- m 30 V (I2T30E) process. The die photo is shown in Fig. 12. A. Sample Output Waveforms The output Vo was loaded with a discrete resistor and a low-leakage 10 nF Teflon capacitor in series, to simulate a typ) were used to ical electrode impedance. Seven digital bits ( set the value of via a 7-bit DAC on chip, and the value of 180 IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS, VOL. 1, NO. 3, SEPTEMBER 2007 Fig. 14. Residual charge error over the range of DAC currents. Note that the residual charge error captures the net effect of any inaccuracies in the positive current pulse causing a mismatch with the negative current pulse in magnitude, duration or shape. Ultimately, charge balance rather than current balance determines the safety of current drivers in an implant. Fig. 13. Output voltage Vo measured with various resistive loads R. was latched on the falling edge of . The size of the LSB could be varied with an external pin control and was nomcorresponds to a 1 mA inally set to 8 A such that output. Sample output voltage waveforms from the biphasic current pulse are shown in Fig. 13. The output voltage compliance exceeds 11 V, but is no greater than 13 V on 6 and 9 V rails, due to 1 V of headroom being sacrificed in active cascodes on both the pMOS and nMOS current drivers. This headroom reduction could be alleviated by using a differential amplifier to drive the active cascode, rather than a common-source amplifier, but at the cost of additional power. Note that the asymmetry of the output waveforms in Fig. 13 allows us to save power by also making the voltage rails asymmetric. The larger negative-going pulse may result in greater charge leakage (through ) during the negative phase, and may also reduce the negative current output by channel-length modulation more than the positive-going pulse reduces the positive current output. A result of this asymmetry is that the final charge error then tends to be positive. C. Verification of Shorting From Capacitor Voltage Measurements To verify that the shorting phase was working as designed, the exponential time constant of discharge during shorting was measured from scope captures of the capacitor voltage waveform, shown in Fig. 15. The best-fit time constant of discharge was measured to be around 40 s. The resistance was 2.2 k for these measurements, confirming that the on-resistance of the shorting tran2 k . If shorting was not performed, the charge sistor was error was observed to accumulate over many cycles and raised the average voltage on the capacitor above ground. Shorting was thus confirmed to be essential in maintaining precise charge balance. D. Settling Time Measurements were made Measurements of the settling behavior of to confirm the loop bandwidth and stability predictions of Section IV-A and B, respectively, and shown in Fig. 16. Settling was well-behaved over all input levels, showing a first-order response and reaching final value well within the allotted time of 16 s. A slight bumpiness in the waveforms is caused by clock switching injection, which is likely the major cause of the final imbalance in current. B. Residual Charge Error E. Noise Measurements The precision of the dynamic current balance was obtained by measuring the residual voltage integrated on the 10 nF Teflon capacitor at the end of the biphasic pulse. A plot of this error over the range of DAC currents is shown in Fig. 14. The decrease in error at high currents may be caused by velocity saturation effects in device , as suggested by simulation, which reduces the transconductance and hence the conversion gain of voltage error on into output-current error. The worst-case charge error of 0.12 nC out of a full scale charge of 30 nC thus accounts for a mismatch of 0.4% in our scheme. To verify the level of circuit noise, multiple readings of the final capacitor voltage were taken, to compute the variance in the residual voltage, shown in Fig. 17. The standard deviation of 0.8 mV translates to 8 pC of charge on the 10 nF capacitor. The measured noise is slightly higher than the calculated 2.4 pC in Section IV-C, but is still very small, on the order of 0.025% of the full scale of 30 nC. The additional noise likely arises from sources like timing jitter in the pulsewidth which we have neglected in our calculations. Fortunately, it is small enough to not be of concern. SIT AND SARPESHKAR: LOW-POWER BLOCKING-CAPACITOR-FREE CHARGE-BALANCED ELECTRODE-STIMULATOR CHIP 181 Fig. 15. Capacitor voltage scope captures at the end of a biphasic pulse, which allow measurements of residual voltage and to be made. The power consumption in this work has not been optimized because we have exceeded the settling time specification of 16 s by a significant margin. We could therefore reduce the ) and source-follower ( ) power in the analog storage ( to achieve perhaps as much as a 50% reduction in the 40 W of unshared power. G. Average DC Current Error Fig. 16. Settling time measurements for Vp over various input levels. F. Power Consumption Most of the biasing power (e.g., in the voltage reference and active cascodes) can be shared between multiple channels in a multichannel implant. If we amortize this biasing power by 16 channels in a 16-channel implant, the dominant source of power consumption then lies in Ibs and the analog storage transconductor, , which cannot be shared. The current and each leg of the transconductor was biased with 1.2 A, which on 6 and 9 V rails works out to consume 40 W. An additional 7 W of shared biasing power then yields a total of 47 W per channel. Dynamic current balancing as we have implemented on its own achieves 0.4% mismatch by yielding 120 pC imbalance out of the 30 nC full scale charge. By following dynamic current balancing with shorting, an additional reduction in the charge error can be achieved as a function of the electrode impedance and minimum inter-pulse interval. Assuming a maximum eleck nF s (including trode time constant of 2 k of on-resistance in the shorting switch) and a minimum interval of 1 ms between pulses, the electrode can be discharged for at least three time constants or achieve a charge reduction of at least . The net dc current error is then the charge error divided by the inter-pulse interval of 1 ms, i.e., pC ms nA. This level of error puts us well below the safety limit in neural implants of 25 nA, and starts to approach the level of safety afforded by dc blocking capacitors. With further refinements in our dynamic current balancer, especially in the area of rejecting charge injection from the clock and other switching transients, 0.1% mismatch at the same full- 182 IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS, VOL. 1, NO. 3, SEPTEMBER 2007 Fig. 17. Multiple (N = 1600) scope acquisitions are used to compute the mean () and standard deviation ( ) of the residual error voltage, taken at 80.8 s. This measurement was taken with Din = 64, which exhibited the worst-case error of 12 mV. The end of the biphasic pulse occurs at 80.5 s, and shorting begins at 81 s. TABLE I PERFORMANCE COMPARISON OF BLOCKING-CAPACITOR-FREE ELECTRODE STIMULATOR DESIGNS scale current of 1 mA should be achievable, suggesting that future improvements may result in a 1.5 nA error. VI. CONCLUSION This paper shows that the two-step technique of cascading dynamic current balancing followed by shorting can achieve a level of dc current error of 6 nA and a residual voltage error of 12 mV, comparable to dc blocking capacitor performance. Table I summarizes our electrode-stimulator performance relative to other designs. Our results suggest that a future generation of neural implants can implement charge balancing in active electronics and remove the need for dc blocking capacitors, thus removing a big bottleneck in reducing their size. ACKNOWLEDGMENT The authors would like to thank M. O’Halloran for helpful discussions regarding the design and use of the low-leakage analog storage cell. SIT AND SARPESHKAR: LOW-POWER BLOCKING-CAPACITOR-FREE CHARGE-BALANCED ELECTRODE-STIMULATOR CHIP REFERENCES [1] J. C. Lilly, J. R. Hughes, E. C. Alvord, Jr., and T. W. Galkin, “Brief, noninjurious waveforms for stimulation of the brain,” Science, vol. 121, pp. 468–469, 1955. [2] R. K. Shepherd, N. Linahan, J. Xu, G. M. Clark, and S. Araki, “Chronic electrical stimulation of the auditory nerve using noncharge-balanced stimuli,” Acta Otolaryngologica, vol. 119, pp. 674–684, 1999. [3] C. Q. Huang, R. K. Shepherd, P. M. Center, P. M. Seligman, and B. Tabor, “Electrical stimulation of the auditory nerve: Direct current measurement in vivo,” IEEE Trans. Biomed. Eng., vol. 46, no. 4, pp. 461–469, Apr. 1999. [4] J. F. Patrick, P. M. Seligman, D. K. Money, and J. A. Kuzma, “Engineering,” in Cochlear Prostheses. Edinburgh, U.K.: Churchill-Livingstone, 1990. [5] D. Ni, R. K. Shepherd, H. L. Seldon, S.-A. Xu, G. M. Clark, and R. E. Millard, “Cochlear pathology following chronic electrical stimulation of the auditory nerve. I: Normal hearing kittens,” Hearing Res., vol. 62, pp. 63–81, 1992. [6] J. Xu, R. K. Shepherd, R. E. Millard, and G. M. Clark, “Chronic electrical stimulation of the auditory nerve at high stimulus rates: A physiological and histopathological study,” Hearing Res., vol. 105, pp. 1–29, 1997. [7] X. Liu, A. Demosthenous, and N. Donaldson, “A stimulator output stage with capacitor reduction and failure-checking techniques,” in Proc. IEEE ISCAS, 2006, pp. 641–644. [8] X. Fang, J. Wills, J. Granacki, J. LaCoss, A. Arakeliana, and J. Weiland, “Novel charge-metering stimulus amplifier for biomimetic implantable prosthesis,” in Proc. IEEE ISCAS, 2007, pp. 569–572. [9] E. K. F. Lee and A. Lam, “A matching technique for biphasic stimulation pulse,” in Proc. IEEE ISCAS, 2007, pp. 817–820. [10] M. Ortmanns, N. Unger, A. Rocke, M. Gehrke, and H. J. Tietdke, “A 0.1 mm , digitally programmable nerve stimulation pad cell with highvoltage capability for a retinal implant,” in Proc. IEEE ISSCC, 2006, pp. 89–98. [11] P. T. Bhatti and K. D. Wise, “A 32-site 4-channel high-density electrode array for a cochlear prosthesis,” IEEE J. Solid-State Circuits, vol. 41, no. 12, pp. 2965–2973, Dec. 2006. [12] X. Liu, A. Demosthenous, and N. Donaldson, “A miniaturized, powerefficent stimulator output stage based on the bridge rectifier circuit,” in Proc. IEEE APCCAS , 2006, pp. 498–501. [13] E. C. Field-Fote, B. Anderson, V. J. Robertson, and N. I. Spielholz, “Monophasic and biphasic stimulation evoke different responses,” Muscle & Nerve, vol. 28, pp. 239–241, 2003. [14] J.-J. Sit, A. M. Simonson, A. J. Oxenham, M. A. Faltys, and R. Sarpeshkar, “A low-power asynchronous interleaved sampling algorithm for cochlear implants that encodes envelope and phase information,” IEEE Trans. Biomed. Eng., vol. 54, no. 1, pp. 138–149, Jan. 2007. 183 [15] G. Wegmann and E. A. Vittoz, “Very accurate dynamic current mirrors,” Electron. Lett., vol. 25, pp. 644–646, 1989. [16] K. Martin and D. A. Johns, Analog Integrated Circuit Design. Toronto, Canada: Wiley, 1997. [17] M. O’Halloran and R. Sarpeshkar, “A 10-nW 12-bit accurate analog storage cell with 10-aA leakage,” IEEE J. Solid-State Circuits, vol. 39, no. 11, pp. 1985–1996, Nov. 2004. [18] M. O’Halloran and R. Sarpeshkar, “An analog storage cell with 5 electron/sec leakage,” in Pro. IEEE ISCAS, 2006, pp. 557–560. Ji-Jon Sit received the B.S. degree in electrical engineering and computer science at Yale University, New Haven, CT, in 2000, and the M.S. degree in electrical engineering from the Massachussetts Institute of Technology, Cambridge, in 2002, where he received the Ph.D. degree in electrical engineering, in the Analog VLSI and Biological Systems Group in 2007. He is now with Advanced Bionics Corporation, Sylmar, CA, and works on emerging cochlear implant technology. Rahul Sarpeshkar received the B.S. degrees in electrical engineering and physics at the Massachussetts Institute of Technology (MIT), Cambridge, and the Ph.D. degree from California Institute of Technology, Pasadena. After completing the Ph.D., he joined Bell Labs as a member of technical staff in the Department of Biological Computation within its Physics division. Since 1999, he has been on the faculty of MIT’s Electrical Engineering and Computer Science Department where he heads a research group on Analog VLSI and Biological Systems. He holds over twenty patents and has authored more than 70 publications including one that was featured on the cover of Nature. He has given over 100 invited lectures. His research interests include analog and mixed-signal VLSI, biomedical systems, ultra low power circuits and systems, biologically inspired circuits and systems, molecular biology, neuroscience, and control theory. Prof. Sarpeshkar has received several awards including the Packard Fellow award given to outstanding young faculty, the ONR Young Investigator Award, the NSF Career Award, and the Indus Technovator Award. He is currently an Associate Editor of the IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS. He has received the Junior Bose award and the Ruth and Joel Spira award for excellence in teaching at MIT.