Frequency Domain Target Impedance Method for Bypass Capacitor

advertisement

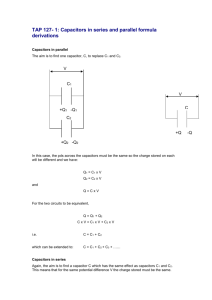

Frequency Domain Target Impedance Method for Bypass Capacitor Selection for Power Distribution Systems Larry D Smith, Altera Corporation lsmith@altera.com 408-544-7822 ©©2006 2005Altera AlteraCorporation Corporation Frequency Domain Target Impedance Method (FDTIM) Calculate target impedance Determine corner frequency Select Components − − − − VRM Bulk capacitors (matched with VRM) High frequency ceramic capacitors Power planes Works well with readily available capacitors Why is it a target? If your system impedance is: − Above it, you may have noise problems − Below it, you probably paid too much for it © 2006 Altera Corporation 2 of 9 2006 DesignCon Panel Discussion L.D.Smith Impedance (Ohms) Components for Power Distribution 1 0.1 0.01 0.001 0.0001 1.00E+00 1.00E+03 1.00E+06 1.00E+09 1.00E+12 Frequency (Hz) PCB Power Planes - LPF + + - Package Power Planes Load Ref VRM © 2006 Altera Corporation 3 of 9 Bulk Capacitors 2006 DesignCon Package Capacitor Ceramic Capacitors Panel Discussion L.D.Smith On-chip Capacitance Capacitor Characteristics 100m Volts Mag (log) 10nF 100nF 10m 1uF 10uF 100uF 1m 100k 1x 10x Frequency (log) (HERTZ) 100x 10x Frequency (log) (HERTZ) 100x 10m Volts Mag (log) SPICE Simulation Family of Ceramic capacitors X5R and X7R dielectric Several sizes Quantities in parallel to reach target impedance 1m 100k © 2006 Altera Corporation 4 of 9 2006 DesignCon Panel Discussion 1x L.D.Smith Simulation of Parallel Caps 10m − Capacitors chosen to meet 1 mOhm Volts Mag (log) Top Panel 1m Bottom Panel 50 MHz corner frequency © 2006 Altera Corporation 5 of 9 2006 DesignCon 1x 10x Frequency (log) (HERTZ) 100x 100k 1x 10x Frequency (log) (HERTZ) 100x 10m Volts Mag (log) − Modified matrix to stay below 1 mOhm 100k 1m Panel Discussion L.D.Smith Inductance is Important! Several values of Mounting inductance 10m L_mount=800pH L_mount=400pH Ability to meet corner frequency Q (dips and peaks) L_mount=200pH L_mount=001pH Volts Mag (log) − 1, 200, 400, 800, 1600 pH 1m Ztarget 100k © 2006 Altera Corporation 6 of 9 L_mount=1600pH 273 Capacitors 2006 DesignCon Panel Discussion 1x 10x Frequency (log) (HERTZ) L.D.Smith 100x Corner Frequency © 2006 Altera Corporation 7 of 9 10m 90 capacitors L_mount=600pH 120 capacitors 160 capacitors 213 capacitors 273 capacitors Volts Mag (log) Final ‘exit inductance’ is proportional to the number of capacitors Capacitor quantity can be reduced for lower corner frequency Determine corner frequency from properties of mounted package 1m 2006 DesignCon Ztarget 100k Panel Discussion 1x 10x Frequency (log) (HERTZ) L.D.Smith 100x Compare FDTIM to Other Methods 10m 120 capacitors optimized − FDTIM (blue) − Big V (light blue) − ‘1 per decade’ (brown) − Must deal with it at the package and die level 5 x 100uF 100u 65 x 1uF 50 x 10uF 120 x 4.7uF 2006 DesignCon 1x 10x Frequency (log) (HERTZ) 100x 100m chip/package resonance 10m Ztarget 1m 100u VRM inductance 10k © 2006 Altera Corporation 8 of 9 100k 10k Volts Mag (log) Capacitors alone meet target impedance for about the same frequency range Big V method has trouble at low frequency when combined with VRM ‘1 per decade’ method exceeds target impedance in a couple of spots None of the methods address the high frequency peak Volts Mag (log) 120 FDTIM caps Ztarget 1m Panel Discussion 100k L.D.Smith 1x 10x Frequency (log) (HERTZ) 100x FDTIM attributes Uses many different capacitor values − Perhaps a dozen − 3 values per decade (10, 22, 47) Usually the least expensive BOM − Standard capacitor geometry series 1210, 0805, 0603, 0402 sizes − Smaller capacitors cost less Usually the least board area − Only use large size capacitors where necessary Uses capacitors that are readily available © 2006 Altera Corporation 9 of 9 2006 DesignCon Panel Discussion L.D.Smith Bypass Capacitor Selection Dale Becker, Ph.D. IBM, Poughkeepsie, NY, USA wbecker@us.ibm.com DesignCon 2006 Feb. 6, 2006 Power Distribution Design Goals • • • • • • Minimize cost Minimize discontinuities Exceed Vmin to achieve frequency sort points Don’t exceed Vmax to meet power limits Limit ∆V/∆T to minimize jitter on interfaces Result: – Key metric is the concept of target impedance – Quantify SSN impact on signal performance February 6, 2005 Becker - Power Distribution Design 2 Processor Card February 6, 2005 Becker - Power Distribution Design 3 Decoupling Overview Voltage Level Bulk Decoupling Board Decoupling Package Decoupling On-Chip Decoupling 1999 Paper 400 Amps 12 Processors 200 – 560 µF 920 – 1 µF 250 – 10 µF 90 – 200nF [1 MCM] 50 nF 2005 System 1 1300 Amps 16 Processors 203 – 1500 µF 402 – 4.7 µF 1152 – 22 µF 232 -- 200nF [2 MCMs] 500 nF 2006 System 2 1000 Amps 16 Processors 180 – 1500 µF 1604 – 10 µF 217 -- 200nF [1 MCM] 500 nF February 6, 2005 Becker - Power Distribution Design 4 Mid-frequency current loops ι on-mcm decaps noise sources with on-chip decaps L L1_eff MCM vias voltage regulator L decaps L MCM MCM pins L L2_eff board L February 6, 2005 decaps on board backside Becker - Power Distribution Design 5 Board level time constants 800 600 (mA) i7, electrolytic decap i4, on-mcm decap i3, MCM via 165ns 400 i8, R-L at connector to voltage regulator Current 200 0 -200 i6, 10uF on-board decap -400 i5, 1uF on-board decap -600 0 200 400 Time February 6, 2005 600 800 1000 (ns) Becker - Power Distribution Design 6 Summary • Choosing bypass capacitors – Must reflect the system requirements under design – Must minimize effect of discontinuities – Cannot be done without considering the next levels of packaging – Must reflect realities of component availability February 6, 2005 Becker - Power Distribution Design 7 System Considerations for Bypass Filter Designs Steve Weir steve@teraspeed.com Teraspeed Consulting Group LLC (775) 762 9031 CA, (401) 284 1827 RI Page 1 ©Teraspeed Consulting Group LLC, 2006 Reproduction or Distribution Prohibited TERASPEED CONSULTING GROUP How Many Poles Should We Have? • “One” pole pair, big “V” • A few, capacitors by the decade • Many, E3 series across bandwidth Page 2 ©Teraspeed Consulting Group LLC, 2006 Reproduction or Distribution Prohibited TERASPEED CONSULTING GROUP Perfect 1.47N vs Real 1.47N • Perfect, very flat magnitude, linear phase • Real, same capacitor count, more variation – Quantization at low freq, drops ESR Page 3 ©Teraspeed Consulting Group LLC, 2006 Reproduction or Distribution Prohibited TERASPEED CONSULTING GROUP Real 1.47N vs Big “V” • Near cut-off: – 1.47N Same capacitor count better response OR – 1.47N Lower capacitor count for similar response • Phase is resistive to a much higher frequency than Big “V” Page 4 ©Teraspeed Consulting Group LLC, 2006 Reproduction or Distribution Prohibited TERASPEED CONSULTING GROUP Slow Edge Peaking w/o Damping • At slow edge rates, FRES is well above signal B/W – Ringing is limited and does not build Page 5 ©Teraspeed Consulting Group LLC, 2006 Reproduction or Distribution Prohibited TERASPEED CONSULTING GROUP Fast Edge Peaking w/o Damping • Big “V” & MP both ring badly. Big “V” worse. Page 6 ©Teraspeed Consulting Group LLC, 2006 Reproduction or Distribution Prohibited TERASPEED CONSULTING GROUP Fast Edge Peaking w/ Damping • Distributed damping great noise amplitude equalizer Page 7 ©Teraspeed Consulting Group LLC, 2006 Reproduction or Distribution Prohibited TERASPEED CONSULTING GROUP Example PDN Effects, IC Die Capacitance Page 8 ©Teraspeed Consulting Group LLC, 2006 Reproduction or Distribution Prohibited TERASPEED CONSULTING GROUP Damp on the PCB • FRES located within B/W of high ESR or MP damps near ZTARGET Page 9 ©Teraspeed Consulting Group LLC, 2006 Reproduction or Distribution Prohibited TERASPEED CONSULTING GROUP Conclusions • High ESR and many pole networks can provide benefits in specific situations • High edge rates demand one form or another of distributed damping • Distributed damping almost completely eradicates HF noise performance between big “V”, high ESR and many pole methods • Distributed damping is the subject of multiple patents Page 10 ©Teraspeed Consulting Group LLC, 2006 Reproduction or Distribution Prohibited TERASPEED CONSULTING GROUP How to Choose Bypass Capacitors Bypass Capacitor Selection Based on Time Domain and Frequency Domain Performances Istvan Novak DesignCon 2006, TecForum THA2, February 2006 DesignCon 2006 panel February 2006 Defining the metric Requirements towards PDNs ● Worst-case peak-to-peak transient noise ● Resonance-free construction ● Low sensitivity ● Uniform stress distribution ● Portability ● Cost ● Size (area, component height) DesignCon 2006, 11-TA4, February 2006 2 So what is the METRIC? ● ● ● PDN design is usually done in the frequency domain Target impedance is specified PDN is better if Z is lower Impedance magnitude [ohm] 1.E-01 PDN1 1.E-02 Or is it??? PDN2 1.E-03 1.E+3 Frequency [Hz] 1.E+4 1.E+5 DesignCon 2006, 11-TA4, February 2006 1.E+6 1.E+7 1.E+8 3 Comparison of popular methods ● ● ● ● “Multi-pole” (MP) “Capacitors-by-the-decade” (CBD) “Big-V” “Distributed Matched Bypassing” (DMB) DesignCon 2006, 11-TA4, February 2006 4 Comparison with AVP Solution with the lowest impedance has the highest transient noise! Step response [V] Impedance magnitude [ohm] 1.E-01 1.2E-02 Distributed Matched Bypassing: 10 mVpp/A 1.0E-02 Distributed Matched Bypassing 8.0E-03 1.E-02 Multi-pole: 15.7 mVpp/A 6.0E-03 Multi-pole Big-V: 21.4v mVpp/A 4.0E-03 Big-V 2.0E-03 Frequency [Hz] 1.E-03 1.E+4 1.E+5 1.E+6 Time [sec] 1.E+7 1.E+8 0.0E+00 1.E-9 1.E-8 1.E-7 1.E-6 1.E-5 DMB: Big-V: Multi-pole: • best transient noise, good EMI • simple BOM • workload/dissipation is shared • zero sensitivity to C and L • best portability • medium transient, bad EMI • simplest BOM • workload/dissipation is shared • low sensitivity to C and L • medium portability • medium transient, medium EMI • complex BOM • workload/dissipation not shared • high sensitivity to C and L • worst portability 5 DesignCon 2006, 11-TA4, February 2006 1.E- Pulse response [V] 1.E-2 DMB with gradual AVP 8.E-3 6.E-3 4.E-3 ` 2.E-3 0.E+0 Impedance magnitude [ohm] 1.E-1 -2.E-3 1.E-9 10E-3 8E-3 5E-3 1.E-2 2E-3 1E-3 5E-4 2E-4 1E-4 1.E-3 Frequency [Hz] 1.E-4 1.E+2 1.E+3 1.E+4 1.E+5 1.E+6 DesignCon 2006, 11-TA4, February 2006 1.E+7 1.E+8 Time [sec] 1.E-8 1.E-7 1.E-6 1.E-5 1.E-4 Worst-case transient noise gradually increases as ZDC goes down. The multiplier: Z DC 2− Z nom 6 Step response [V] 1.2E-2 Big-V with varying dip 1.0E-2 11E-3 10E-3 8E-3 5E-3 2E-3 1E-3 5E-4 2E-4 1E-4 8.0E-3 6.0E-3 4.0E-3 Impedance magnitude [ohm] 1.E-1 2.0E-3 0.0E+0 1.E-9 Time [sec] 1.E-8 1.E-7 1.E-6 1.E-5 11E-3 10E-3 8E-3 5E-3 1.E-2 2E-3 1E-3 1.E-3 Frequency [Hz] 1.E-4 1.E+5 1.E+6 5E-4 2E-4 1E-4 1.E+7 DesignCon 2006, 11-TA4, February 2006 Worst-case transient noise gradually increases as dip goes deeper. 1.E+8 7 Multi-pole Z vs. N and Q Zmax/Zmin in Muti-pole solution depends on both N and Q. Zmax/ESR [-] 100 N=1 N=2 N=3 N=4 N=5 10 1 0.1 0 1 2 Q [-] 3 4 5 Zmin/ESR [-] 1 Zmax N=1 N=2 N=3 N=4 N=5 ESR Zmin N=3, Q=3 0.1 0 1 2 Q [-] 3 DesignCon 2006, 11-TA4, February 2006 4 5 8 Self-impedance magnitude [ohm] Placement 2”x2” plane at 0.5MHz One capacitor in the middle 1.E-02 Self-impedance magnitude [ohm] 1.E-02 1.E-03 1.E-03 2-mil dielectric C: 100uF, 7mohm, 1nH 50-mil dielectric C: 100uF, 1mohm, 1nH DesignCon 2006, 11-TA4, February 2006 9 Implementation example Impedance with and without DET [ohm] 1.4E-01 1.2E-01 1.9x 1.0E-01 8.0E-02 2.2x 6.0E-02 4.0E-02 2.0E-02 Impedance magnitude [ohm] 1.E+00 0.0E+00 1.E+08 Frequency [Hz] 1.E+09 1.E-01 1.E-02 Frequency [Hz] 1.E-03 1.E+02 1.E+04 1.E+06 1.E+08 DesignCon 2006, 11-TA4, February 2006 T2000 CPU module High-current rail DMB 10