2.3.5 Correct Algorithm to Find Critical Path 343 Complete Example

advertisement

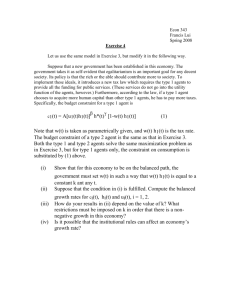

2.3.5 Correct Algorithm to Find Critical Path Complete Example 2a REVISION1 Question: 343 ................................................................ . Find the critical path in the circuit below. CHAPTER 2. TIMING ANALYSIS 344 Signal / path old g on hb, d, e, gi 12 hb, d, e, gi 18 g[e] on hb, d, ei 14 e on hb, d, ei 14 hb, d, ei 18 new 8 14 10 10 14 f a d e g potential delay false 8 12 14 14 j i j h i b c Answer: a unused fanout f h f, g 8 8 8 Find longest path: a 8 8 8 14 f4 8 8 18 b 12 c d 16 e 14 14 g 12 12 12 8 i 4 4 4 j 0 unused fanout f h f, g h, i path a c b,d,e b,d,e,g b,d,e,g,h,i,j side input non-controlling value h[c] 0 i[g] 0 j[f] 0 Contradiction. First false path, find next candidate. Changes in potential delays: 1 new circuit d 12 e 10 10 f4 8 8 g 8 12 8 12 i constraint c b ab 4 4 4 j 0 j h8 i j side input non-controlling value h[c] 0 i[h] 0 j[f] 0 h8 i Explore longest path: potential delay 8 12 18 18 false b 12 c path b,d,e,g,h,i,j a c b,d,e b,d,e,g,j constraint c cb ab Initially, found contradiction, but hb, d, e, g, hi is a prefix of a false path with the same input as the candidate path, and i[h] is a side input to the candidate path. We have a late side input. The viability constraint for this prefix is c. The constraint for the path input (i[g]) to have a controlling value of ’1’ is b. Combining the two constraints together gives us a constraint for the late side input of i[h] to be bc. Adding the constraint of the late side input to to the condition table gives us: side input non-controlling value h[c] 0 i[h] 0 j[f] 0 constraint c bc + bc = c ab The constraints reduce to abc. A falling edge will exercise the path. Critical path Delay Input vector hb, d, e, g, i, ji 14 a=0, b=falling edge, c=0 Illustration of falling edge exercising the critical path: 2.3.5 Correct Algorithm to Find Critical Path a 0 4 0 b c 4 e 4 f 8 8 6 10 6 g i potential delay 8 12 14 18 20 20 false 14 j 10 CHAPTER 2. TIMING ANALYSIS 346 j h 10 i 0 Complete Example 2b Question: 2 d 345 ................................................................ . k g f x c i m REVISION3 h j Changes in potential delays: e Signal / path old g on hc, x, f, gi 12 hc, x, f, gi 20 f[x] on hc, xi 18 x on hc, xi 18 hc, xi 20 REVISION2 Answer: Find longest path: 18 20 x 18 18 8 f 14 g 12 8 i 12 d 12 e 14 12 14 h 14 k 10 8 8 8 j l 4 4 4 4 m 0 m 8 unused fanout k i h f, h k f path c,x,f,g,i,l,m a d e c,x c,x,f,g b Pursue hb, fi. Explore longest path: delay through j, renamed inverter e to x new 8 16 14 14 16 potential delay false 8 12 14 16 16 18 8 a 18 b 2 corrected constraint b d ce a(b + c) Contradiction. First false path, find next candidate. m l d c path a d e b c,x c,x,f,g c,x,f,g,i,l,m side input non-controlling value f[b] 0 i[d] 1 l[j] 1 m[k] 0 Find the critical path in the circuit below. a b unused fanout k i h f f, h i, k 3 In original version, had incorrect delay through j, which caused next path to start at c. What follows until next correction note is based on the correct delay through j. This does not illustrate a late side input. To see a late side input, skip to the next correction note. 2.3.5 Correct Algorithm to Find Critical Path potential delay false 8 12 14 16 16 18 18 347 unused fanout potential delay false 8 12 14 18 19 path c,x,f,g,i,l,m a d e c,x c,x,f,g b,f,g b,f,g,i,l,m k i h f, h k i,k side input non-controlling value f[x] 0 i[d] 1 l[j] 1 m[k] 0 constraint c d ce a(b + c) Constraint simplifies to abcde. hb, f, g, i, l, mi 18 a=0, b=rising edge, c=1, d=1, e=0 Critical path Delay Input vector 0 c 1 d 1 0 f 4 k 6 k i h f side input non-controlling value h[e] 0 l[i] 1 m[k] 0 constraint e bcd a(b + c) Initially, found contradiction, but hc, x, f, g, ii is a prefix of a false path with the same primary input as the candidate path, and l[i] is a side input to the candidate path. We have a late side input. The viability constraint for this prefix is bd. The constraint for the path input (l[j]) to have a controlling value of ’0’ is c + e. Combining the two constraints together gives us a constraint for the late side input of l[i] to be bcd + bde. constraint e bcd + bcd + bde = bd a(b + c) 0 6 i 10 l m 14 18 m 1 0 e g path c,x,f,g,i,l,m a d e b c,x,h,j,l,m side input non-controlling value h[e] 0 l[i] 1 m[k] 0 0 x unused fanout Adding the constraint of the late side input to to the condition table gives us: Demonstrate excitation of path: a b CHAPTER 2. TIMING ANALYSIS 348 0 h j 0 The constraints reduce to abcde. hc, x, h, j, l, mi 19 a=0, b=0, c=falling edge, d=1, e=0 Critical path Delay Input vector 1 0 Illustration of falling edge exercising the critical path: REVISION4 0 8 a 18 b 18 c 19 d 12 x 17 18 8 f 14 g 12 8 i 12 12 17 e 17 17 k a b 0 4 0 c 8 8 8 l 4 4 4 m 0 m d x f 2 6 13 j 8 4 Modify circuit to illustrate late side input. Make j a very slow inverter with delay of 5. Pick up example after determining that hc, x, f, g, i, l, mi is false. e k 8 8 i 0 12 1 2 h g 0 h 6 j 8 l 12 m 16 m