Edge-triggered Flip-Flop, State Table, State Diagram

Edge-triggered Flip-Flop,

State Table, State Diagram

Edge-triggered Flip-Flop

• Contrast to Pulse-triggered SR Flip-Flop

• Pulse-triggered: Read input while clock is 1, change output when the clock goes to 0. What happens during the entire HIGH part of clock can affect eventual output.

• Edge-triggered: Read input only on edge of clock cycle (positive or negative)

• Example below: Positive Edge-Triggered D Flip-Flop

• On the positive edge (while the clock is going from 0 to 1), the input D is read, and almost immediately propagated to the output Q. Only the value of D at the positive edge matters.

D Q

Clock

D

C

S

C

R

Q

Symbol

• Symbol of edge-triggered D flip-flop

D

C

Positive-edge triggered

D

C

Negative-edge triggered

Flip-Flop Timing

• Set-up time: t s

• Input needs to be stable before trigger

• Hold time: t h

• Input needs to be stable after trigger

• Propagation delay: t p

• Some delay from trigger to output change

• Example: Negative edge triggered flip-flip

Clock t s t h t p

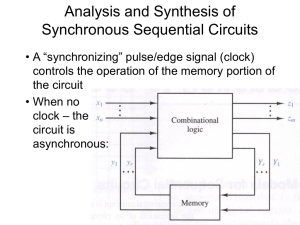

Sequential Circuit Description

• Input Equations

• State Table

• State Diagram

• We’ll use the following example

X

Sequential Circuit Description

D

C

A

A

Clock

D

C

B

B

Y

X

Sequential Circuit Description

Next state Present state input

D

C

A

A

D

C

Clock

At the clock trigger, the next state will be read and transferred to the present state

B

B

Y output

Input Equations

A next

= A present

X + B present

X

B next

= A’ present

X

Y = (A present

+ B present

)X’

Next state in terms of input and present state

Output in terms of input and present state

State Table

Present State Input Next State Output

A B X A B Y

0 0 0 0 0 0

0 0 1 0 1 0

0 1 0 0 0 1

0 1 1 1 1 0

1 0 0 0 0 1

1 0 1 1 0 0

1 1 0 0 0 1

1 1 1 1 0 0

State Diagram

0/0

1/0

0/1

00

10

01

0/1

0/1

1/0

1/0

11

1/0

Mealy and Moore Models

• Preceding Example: Output depends on present state and input.

This is called the Mealy Model

• Another kind of circuit: Output only depends on present state. This is called the Moore Model

Example of Moore Model

X

Y

A

D

C

Z

A next

= A present

+ XY

Z = A present

Clock

X Y A present

A next

0 0 0 0

0 0 1 1

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

00,01,10

0/0

11

1/1

00,01,10,11

Moore Model

Inputs Some

Combinational

Circuit

Flip-flops

Some

Combinational

Circuit

Outputs

Mealy Model

Inputs Some

Combinational

Circuit

Flip-flops

Some

Combinational

Circuit

Outputs

Mealy and Moore Model

State Diagrams

0/0

1/0

Moore input

00,01,10

0/0 state output

11

1/1 input output

0/1

00

10

1/0 state

0/1

0/1

1/0

00,01,10,11

01

1/0

11

How to Design a Sequential Circuit

• 1. Specification

• 2. Formulation: Draw a state diagram

• 3. Assign state number for each state

• 4. Draw state table

• 5. Derive input equations

• 5. One D flip-flop for each state bit

Example

• Design a sequential circuit to recognize the input sequence 1101.

• That is, output 1 if the sequence 1101 has been read, output 0 otherwise.

0/0

A

1/0

0/0

B

1/0

1/1

1/0

C

0/0

D

0/0

Assign States

• 4 states, so we need 2 bits

0/0

00

1/0

0/0

01

1/0

1/1

1/0

10

0/0

11

0/0

State Table

Present State Input Next State Output

A B X A B Y

0 0 0 0 0 0

0 0 1 0 1 0

0 1 0 0 0 0

0 1 1 1 0 0

1 0 0 1 1 0

1 0 1 1 0 0

1 1 0 0 0 0

1 1 1 0 1 1

Input Equations

A next

= A’BX + AB’

B next

= A’B’X + AB’X’ + ABX

Y = ABX

X

Circuit Diagram

Exercise:

Fill in the input to

Flip-Flop B

Clock

D

C

D

C

B

B

Y

A

A