sTGC Front end boards

L. Levinson

sTGC

Front end boards

NSW Electronics workshop

November 2013

L. Levinson

Weizmann Institute

NSW Electronics workshop, November 2013 1

sTGC Front end boards

L. Levinson NSW Electronics workshop, November 2013 2

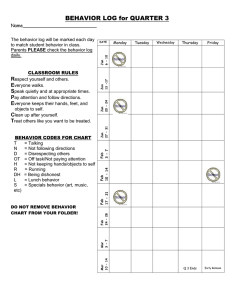

Issues

• FE boards on both edges of chamber to balance heat

to avoid cables from side-to-side, need GBT on each edge

• 2 GBTs per quadruplet instead of GBT per layer

cabling is self-contained in one quadruplet

loss of one GBT means quadruplet lost

MM does GBT per layer for 4 quadruplets

GBT pad strip pad strip

• Signal integrity

• Zebra connectors, same as for MM

• Slow Control Adapter, SCA, ASIC on every FEB for

– Configuration of VMM and TDS via I 2 C

– Temperature and voltage monitoring

– Calibration of VMM?

• E-link connectors from FEB to GBT board: candidate: twinax ribbon

• Component height restriction: 9mm DC-DC height?

• ?separate analog, digital gnds for VMM strip GBT pad strip pad

L. Levinson NSW Electronics workshop, November 2013 3

E-links

E-link to each Companion, 80Mb/s

6 or 7 per strip FEB, 2 per pad/wire FEB

clock

TTC

data (If FELIX streams are used, status/monitoring data can also be sent on this link.)

E-link to SCA, 80Mb/s, one per FEB

clock

configuration

configuration reply

Can there be single clock pair from GBT? bussed or find a rad tol SLVS fan-out chip

L. Levinson NSW Electronics workshop, November 2013 4

Wire group “FEB”

• Flex PCB to extract wire signals and bring them to FEB on edge

• Wires are read out by single VMM per layer on the Pad FEB

• Wire VMMs need extra protection: transient suppressor

• Max 64 wire groups per detector

L. Levinson NSW Electronics workshop, November 2013 5

VMM2 board for trigger demonstrator

• 128 channels

• Design in progress

L. Levinson NSW Electronics workshop, November 2013 6