Document

advertisement

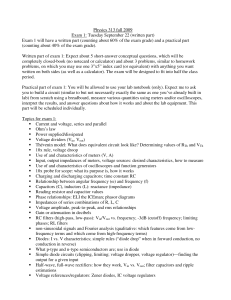

ECE-342 Test 1: Sep 28, 2010

6:00-8:00, Closed Book

Name : SOLUTION

All solutions must provide units as appropriate. Use the physical constants and data as provided on the formula sheet

(the last page of the exam). Use of rounded values will result in points deductions. Unless otherwise stated, assume

T = 300 K.

1. (15 pts) For each of the following circuits, use the 0.7 volt diode drop model to find and plot the output voltage

vout (t). Use the same axes as the provided plot of vin (t).

(a) (7 pts)

Solution:

This is a standard diode “clamp”, that prevents a voltage from exceeding 0.7 V above a power supply, or dropping

more than 0.7 V below ground.

(b) (8 pts)

Solution:

Here’s the standard “level shifter”. At first, vout tracks vin , since the diode is off, and no charge is stored on the

capacitor. Once vout reaches 0.7 V, the diode turns on, clamping the output voltage at 0.7 V. Current through the

diode charges the capacitor until vin reaches 5 V (resulting in 4.3V across the capacitor). The capacitor cannot

discharge through the diode, so this voltage never changes. The output voltage remains 4.3 volts below the input.

2. (20 pts) The circuit below shows an input stage for an instrumentation amplifier except for a component mismatch between the two feedback resistors. For the circuit shown, derive the differential gain Ad = vo /vid and

the common-mode gain Acm = vo /vicm , where vid and vicm are the differential and common-mode components of the input signal. Assume that the operational amplifiers are ideal.

Solution: To find the common mode gain, set vi1 = vi2 = vicm , giving v1− = v2− = vicm at the op-amp terminals.

Since there’s no voltage drop across the resistor, i = 0, giving

vo1 = v1− = vicm

vo2 = v2− = vicm

vo = vo1 − vo2 = 0.

So the common-mode gain is Acm = 0

To find the differential gain, set vi1 = +vd /2 and vi2 = −vd /2. In this case v1− = vd /2 and v2− = −vd /2

resulting in the current

v1− − v2−

vd

i=

=

1 kΩ

1 kΩ

This current, through the feedback resistors, gives the output voltages.

vd

(50 kΩ)vd

+

= 50.5vd

2

1 kΩ

(51 kΩ)vd

vd

= −51.5vd

vo2 = v2− − (51 kΩ)i = − −

2

1 kΩ

vo = vo1 − vo2 = 102vd

vo1 = v1− + (50 kΩ)i =

So the differential gain is Ad = 102

3. (24 pts) The diodes in the circuit below are known to have ideality coefficient n = 2, but the exact value of Is

is not known (and may change over time). You may assume that the forward voltage drop of one of the diodes

for a current of 5 mA is close to (but not exactly) 0.7 V. The circuit is designed to present a (nearly) constant

voltage level to the load.

(a) (4 pts) Assuming no external load (iout = 0), Select a value of R so that the

diode current is approximately 5 mA. For your solution, how much would the

diode current change if the actual diode drop was 0.6 V(instead of the 0.7 V

value given above)?

(b) (8 pts) Assuming the 0.7 Vdiode drop model, draw (and carefully label) a

sketch of the output voltage vout versus the load current iout for values in the

range −6 mA < iout < 6 mA.

(c) (8 pts) Now use the exponential diode model to predict the actual slope of the

vout versus iout characteristic near iout = 0. How much variation in vout is

expected for load currents in the range −1 mA ≤ iout ≤ +1 mA?

(d) (4 pts) As the temperature of the circuit increases, how would you expect the

output voltage vout to change? (Assume a fixed load current iout . Justify.)

Solution:

(a) Since vout ≈ 2.1 V, set R = (7.9 V)/(5 mA) = 1.58 kΩ If the diode drop happens to be 0.6 V (giving

vout = 1.8 V), the resulting current would be iD = (8.2 V)/(1.58 kΩ) = 5.19 mA (an increase of 190 µA).

(b) Using the .7 V drop diode model, vout should remain exactly at 2.1 V as long as the diodes are forward

biased. When iout reaches 5 mA, the diodes become reverse biased, and the output voltage is vout = (10 V)−

(1.58 kΩ)iout . The characteristic is plotted below.

(c) Essentially, this question deals with the small-signal resistance associated with the diode. It’s not hard to

derive the slope of the curve directly, starting from the diode exponential model:

iD

5 mA − iout

5 mA − iout

vD = nVT ln

= nVT ln

vout = 3vD = 3nVT ln

Is

Is

Is

dvout

Is

−1

= 3nVT

diout

5 mA − iout

Is

at iout = 0, the slope of the curve is

slope =

−3nVT

−3(2)(25.8 mV)

=

= −30.96 Ω

5 mA

5 mA

Changes in iout by ±1 mA should result in the output changing by ±30.96 mV.

(d) For a silicon diode at near room temperature, increasing the temperature will cause a drop in the diode voltage

(holding the current fixed). This is due to the exponential behavior of Is , which dominates the change due to

VT . The value of vout will drop.

4. (22 pts) Design a noninverting amplifier with a DC gain of 10. Formulate your design such that the output is

insensitive to the op-amp input bias current. DC errors at the op-amp output should be kept below 1 mV. When

a 100 mV voltage step is applied to the input, the output must be within 50 µV of its final output (near 1 V) in

at most 400 ns.

Assume that the op-amp has an input bias current of 0.5 µA, an input offset current of 100 nA, and an input

offset voltage of 50 µV.

(a) (12 pts) Draw a schematic of your design, showing all component values. Your schematic should show the

connection of the input source vin (t). Clearly show how the above specifications led to your selection of

component values.

Solution:

The schematic is shown, where the gain has been set to 10, and the input

bias current compensation resistor has been included. To ensure that DC

errors are kept below 1 mV,

Vos (10) + Ios (.9R)(10) ≤ 1 mV

500 µV + (100 nA)(9R) ≤ 1 mV

.5 mV

R≤

= 555.5 Ω.

9(100 nA)

So a valid selection would be R = 500 Ω, 9R = 4500 Ω, 0.9R = 450 Ω.

Using larger resistors will increase the effect of the input offset current,

and cause larger DC errors at the output.

(b) (10 pts) Determine the required unity-gain bandwidth of the op-amp.

Solution: For a single-time-constant system, the output waveform will have the form vo = 1 − e−t/τ , where τ is

the system time constant. To have an error of less than 50 µV when t = 400 ns requires

1 − e−(400 ns)/τ ≥ 1 − 50 µV

e−400/τ ≤ 50 µV

−400/τ ≤ −9.9

τ≤

400 ns

= 40.4 ns.

9.9

To get this time constant, set ω3dB = 1/τ = 24.75 Mrad/sec, or f3dB = 3.94 MHz. Since f3dB = fT /(1 +

R2 /R1 ) = fT /10 we get

fT ≥ (3.94 MHz)(10) = 39.4 MHz

5. (19 pts) The full wave rectifier shown below has an input signal whose frequency is 60 Hz. The rms value of vs

is 8.5 V. Use the 0.7 V diode drop model.

(a) (4 pts) What is the maximum value of vo ?

(b) (10 pts) If R = 10 Ω, determine the value of C so that the ripple voltage is no larger than 0.25 V.

(c) (5 pts) Determine the required “peak inverse voltage” rating for the diodes.

Solution:

√

(a) We know vs is a sinusoid with peak voltage 8.5 2 = 12 V. With a 0.7 V diode drop model, vo can never

exceed 11.3 V

(b) We require that the capacitor discharge over one-half of a cycle (1/120 seconds) is less than 0.25 V.

11.3e−t/τ ≥ 11.3 − 0.25 = 11.05

t=1/120

e−1/(120τ ) ≥ 0.978

τ ≥ 372 ms.

The time constant τ is the RC product:

(10 Ω)C = 0.372

−→

C = 0.037 F

(c) As vs reaches its peak, the reverse-biased diode has −vs = −12 V on the anode, and vout = +11.3 volts on

its cathode. The peak reverse voltage on the diode is 12 + 11.3 = 23.3 V .

The above solution is just a little conservative, since the capacitor is never allowed to discharge over the full

1/120 = 8.33 ms interval. The difference is not great... If you solve for the time at which vo reaches 11.05 V,

you’ll find that the discharge period is actually about 7.8 ms. Using this value gives τ = 349 ms, and C = .035 F.

ECE-342 Test 1, Fall 2010 (Last Page)

Exponential Model:

iD = Is evD /nVT − 1 ≈ Is evD /nVT

Open-Loop Op-Amp Characteristics

(first-order model)

Is : Reverse Saturation Current

VT : Thermal Voltage (≈ 25.8 mV at 300K)

n : Ideality Coefficient

Closed-Loop Op-Amp Amplifiers

(first-order op-amp model)

vD = nVT ln (iD /IS )

rD = nVT /ID

A0 large, low-frequencies:

R2

R2

v0 = 1 +

v1 −

v2

R1

R1

| {z }

| {z }

non-inverting gain

-3 dB bandwidth (either input): fBW =

Finite A0 −→ Gains reduced by

Diode Breakdown:

inverting gain

fT

2

1+ R

R1

1 + R2 /R1

1+

A0

Physical Constants

k = 8.62 × 10−5 eV/K

−23

= 1.38 × 10

J/K

Si Approximation:

ni2 doubles every 5 degrees

q = 1.60 × 10−19 coulomb

Periodic Table Segment

III

IV

V

B

Al

Ga

In

C

Si

Ge

Sn

N

P

As

Sb

0 = 8.854 × 10−14 F/cm

VT = kT /q = 25.8 mV at 300K

Silicon at 300K:

EG = 1.12 eV r = 11.7

ni = pi = 1.5 × 1010 cm−3

µn ≈ 1350 cm2 /V · s

Dn ≈ 34.8 cm2 /s

µp ≈ 480 cm2 /V · s

Dp ≈ 12.4 cm2 /s

ni =1.5 x 1010 at 300K

− EG /kT

n 2i ∝ T 3 e

EG =1.12 eV