C H A P T E R 02 Operational Amplifiers (Op-amp)

advertisement

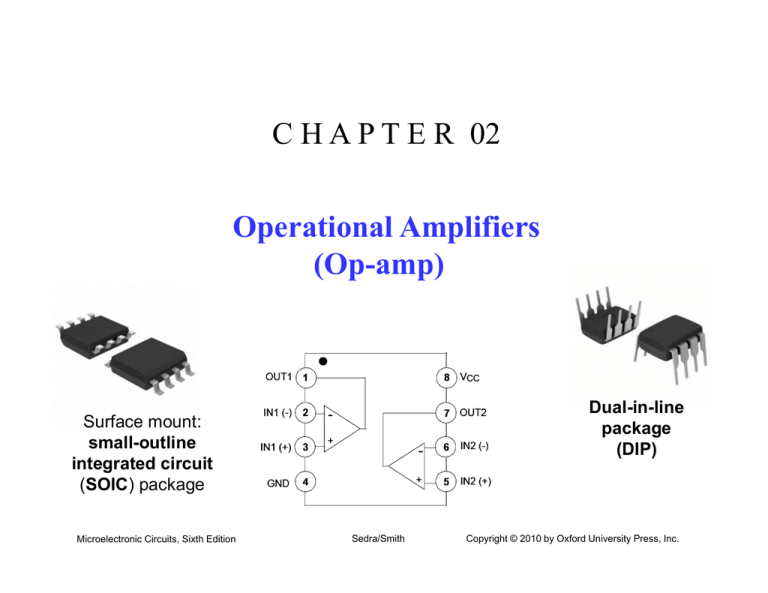

C H A P T E R 02 Operational Amplifiers (Op-amp) Dual-in-line package (DIP) Surface mount: small-outline integrated circuit (SOIC) package Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. The Op-amp Requires DC power to run, amplifies ac signal Figure 2.1 Circuit symbol for the op amp. Figure 2.2 The op amp shown connected to dc power supplies (dual or single supply). Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. The Ideal Op-amp 1. Infinite input impedance 2. Zero output impedance 3. Zero common-mode gain (i.e., infinite commonmode rejection) 4. Infinite loop-gain A (A=∞) 5. Infinite bandwidth Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Differential and Common-mode signals vId=v2-v1 vIcm=1/2(v1+v2) Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Model of internal of an op-amp by circuit Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. The inverting closed-loop configuration. Current at a node (Iin=Iout) Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Analyzing an inverting amplifier Rin=R1 Rout=0 Gain v0 R 2 vI R1 Figure 2.6 Analysis of the inverting configuration. The circled numbers indicate the order of the analysis steps. Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Inverting Configuration, taking gain A into account R2 v0 R1 G R vI 1 (1 2 ) / A R1 Figure 2.7 Analysis of the inverting configuration taking into account the finite open-loop gain of the op-amp. Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. vO R R R 2 (1 4 4 ) vI R1 R2 R3 Example 2.2. The circled numbers indicate the sequence of the steps in the analysis. Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Figure 2.9 A current amplifier based on the circuit of Fig. 2.8. The amplifier delivers its output current to R4. It has a current gain of (1 + R2 /R3), a zero input resistance, and an infinite output resistance. The load (R4), however, must be floating (i.e., neither of its two terminals can be connected to ground). Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. A weighted summer (using superposition technique). A weighted capable of implementing summing of both signs. Sedra/Smith Copyrightcoefficients © 2010 by Oxford University Press, Inc. Microelectronic summer Circuits, Sixth Edition Figure 2.13 Analysis of the non-inverting circuit. The sequence of the Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Microelectronic Circuits, Sixth steps inEdition the analysis is indicated by the circled numbers. Non-Inverting Configuration 1. Effect of finite loop gain R2 ) V0 R1 G R Vi 1 ( 2 ) R1 1 A 2. Input/output impedance - Infinite input - Zero output 1 ( R2 ) R1 % _ gain _ error x100 R2 A 1 ( ) R1 1 ( 3. Voltage follower Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Single Op-amp Difference Amplifiers vO 2 R4 R2 R2 vI 2 (1 ) vI 2 R3 R4 R1 R1 Given ( R 4 / R3) ( R 2 / R1) Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Instrumentation Amplifier Figure 2.20 A popular circuit for an instrumentation amplifier. (a) Initial approach to the circuit Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Instrumentation Amplifier (buy, don’t build) AD623ARZ Figure 2.20 (c) Analysis of the circuit assuming ideal op amps. Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Figure 2.22 The inverting configuration with general impedances in the feedback and the feed-in paths. Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Integrators vC (t ) VC Microelectronic Circuits, Sixth Edition Sedra/Smith 1 C 0 i1 (t ) dt Copyright © 2010 by Oxford University Press, Inc. Differentiator Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Figure 2.39 Open-loop gain of a typical general-purpose internally compensated op amp. Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Figure 2.40 Frequency response of a closed-loop amplifier with a nominal gain of +10 V/V. Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Output Voltage Saturation Figure 2.42 (a) A non-inverting amplifier with a nominal gain of 10 V/V designed using an op amp that saturates at ±13-V output voltage and has ±20mA output current limits. (b) When the input sine wave has a peak of 1.5 V, the output is clipped off at ±13 V. Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Slew Rate Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. Figure 2.44 Effect of slew-rate limiting on output sinusoidal waveforms. Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc. EE 221 Lab (Check EE 221 class website) Microelectronic Circuits, Sixth Edition Sedra/Smith Copyright © 2010 by Oxford University Press, Inc.