special edition of IEEE Solid-State Circuits Magazine

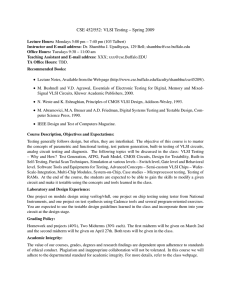

advertisement