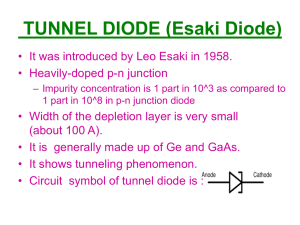

2 - The PN Junction Diode

advertisement