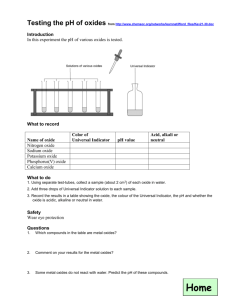

High dielectric constant oxides

advertisement