Lecture 4: Opamp Review Inverting Amplifier (Finite A )

advertisement

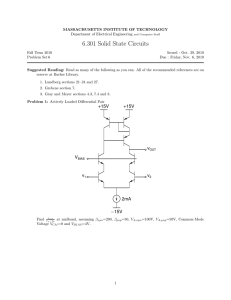

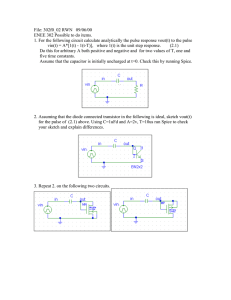

Lecture 4: Opamp Review • Effect of finite open-loop gain, A • Frequency dependence of open-loop gain • Frequency dependence of closed-loop gain • Output voltage and current saturation • Output slew rate • Offset voltage • Input bias and offset current • Non-zero output resistance Assume NON-ideal op amp. Inverting Amplifier (Finite A0) Vin1 Vin 2 A0 Vout A0VX Vin V X V X Vout R2 R1 Vout Vin R1 R2 1 R 1 1 1 A0 R2 For finite open loop gain A0, the error term indicates the larger the closed-loop gain, the less accurate the circuit becomes. 1 Noninverting Amplifier (Finite A0) Vin1 Vin 2 A0 Vout Vin 2 R2 Vout R1 R2 Vout Vin R 1 1 R2 1 R 1 1 1 A0 R2 Use the following approximation: (1 x ) 1 ~ (1 x ) when x>>1 To factor out the A0R2/(R1+R2) term in the denominator V out R R 1 1 1 1 1 1 V in R2 R 2 A 0 Larger ACL, larger the gain error Opamp speed limitation Due to internal capacitances, the gain of op amps begins to roll off. 2 Unity Gain Bandwidth ωb=internal pole of opamp Bandwidth and closed loop gain (Finite A0) ωt =A0ωb ω3db=closed loop opamp 3dB bandwidth Product of gain and bandwidth 3 Gain Bandwidth Product ~(1+R2/R1) Having a loop around the op amp (inverting, noninverting, etc) helps to increase its bandwidth. However, it also decreases the low frequency gain. Slew Rate of Op Amp • In the linear region, when the input doubles, the output and the output slope also double. However, when the input is large, the op amp slews so the output slope is fixed by a constant current source charging a capacitor. • This further limits the speed of the op amp. For large input, the internal circuitry of the op amp reduces to a constant current source charging a capacitor. The slope of the output ramp is called he “slew rate” As it can be seen, the settling speed is faster without slew rate (as determined by the closed-loop time constant). 4 Slew Rate Limit on Sinusoidal Signals • • As long as the output slope is less than the slew rate, the op amp can avoid slewing. However, as operating frequency and/or amplitude is increased, the slew rate becomes insufficient and the output becomes distorted. V in ( t ) V0 sin ωt R Vout ( t ) V0 1 1 ω cos ωt R 2 dVout R V0 1 1 cos t dt R2 Maximum Op Amp Swing • To determine the maximum frequency before op amp slews, first determine the maximum swing the op amp can have and divide the slew rate by it. V out V max V min V V min sin t max 2 2 Note that any output DC offsets will cause a reduction in the maximum voltage swing and SR before clipping If the opamp provides a slew rate of SR, then the maximum frequency of a sinusoid can be obtained by: SR Called the full-power bandwidth dVout FP SR Useful measure of large signal Vmax Vmin dt max speed of opamp 2 5 Input Offset Voltage, VOS • • Zero differential input Ideally zero output Define VOS as input needed to zero output – – Typical values: 1 mV to 5 mV VO caused by VOS depends on closed-loop circuit Ref. Sedra and Smith, Fig. 2.28 Effects of DC Offsets • Offsets in an op amp that arise from input stage mismatch cause the input-output characteristic to shift in either the positive or negative direction (the plot displays positive direction). As it can be seen, the op amp amplifies the input as well as the offset, thus creating errors. R Vout 1 1 Vin Vos R2 6 Saturation Due to DC Offsets • Since the offset will be amplified just like the input signal, output of the first stage may drive the second stage into saturation. Offset in Integrator • A resistor can be placed in parallel with the capacitor to “absorb” the offset. However, this means the closed-loop transfer function no longer has a pole at origin. 1 Vout Z 1 1 1 Vin Z2 sR1C1 Vout Vin Recall that the response to an “input” for the non-inverting “integrator” configuration is the input itself plus the integral of the input (i.e. the second term). Assuming the initial condition across C1 is zero, the circuit integrates the op-amp offset generating an output that tends to +inf or –inf, depending on the sign of Vos. Z1 1 Vin Vin Vin Z2 sR1C1 7 Offset in Integrator Placing R2 in parallel with C1 limits the output voltage by Since at low frequency C1 is effectively an Open. For instance, if Vos=2mV and R2/R1=100, then Vout contains a DC error of 202mV, but at least remains away from saturation. How does R2 affect the integration function? Disregarding VOS, viewing the circuits in Figure (d) and using Vout Z 2 Vin Z1 R Vout 1 2 Vin R1 R2C1s 1 R Vout Vos 1 2 R1 out compared to V 1 Vin R1C1s The circuit now contains a pole at 1/R2C1 rather than at the origin. If the input signal frequencies of interest lie well above this value, then R2C1s>>1 and Vout 1 Vin R1C1 s That is, the integration function holds for frequencies much higher than 1/R2C1. R2/R1 should be small to minimize the amplified offset and R2C1 must be sufficiently large to have negligible impact on the freq. of interest Input Bias and Offset Currents • Op amp input leakage current occurs on dc operating point – Depends on leakage current in electronic device • MOS transistor About 1 picoampere (10-12 amperes) • Bipolar junction transistor About 100 nanoamperes (10-7 amperes) – – Input bias current IB = (IB1 + IB2)/2 Input offset current IOS = |IB1 – IB2| Ref. Sedra and Smith, Fig. 2.32 8 Input Bias Current • The effect of gate leakage or bipolar base currents can be modeled as current sources tied from the input to ground. These currents are typically very small (100nA to 1uA) Consider Fig (a). IB1 has no effect because it flows through a voltage source Vin. Using superposition and setting Vin=0, we arrive at Fig (b), which can be expressed as in Fig (c) using a thevanin equivalent of Vin=R2xIB2 and resulting in (assuming the opamp gain is infinite) R Vout R2 I B 2 1 R1I B 2 R2 Input Bias Current Cancellation • We can cancel the effect of input bias current by inserting a correction voltage in series with the positive terminal. • In order to produce a zero output, Vcorr=-IB2(R1||R2). R Vout Vcorr1 1 I B2 R1 R2 For Vout=0 Vcorr I B2 R1 R2 9 Effects of Input Bias Currents on Integrator • Input bias current will be integrated by the integrator and eventually saturate the amplifier. Vout 1 1 I I B 2 R1dt I B 2 R1dt B 2 dt C1 R1C1 R1C1 So the flow of IB2 through C1 will saturate the opamp. That is, the opamp integrates the current IB2 forcing the output to pos or neg rails. Placing a resistor R1 in series with the non-inverting input can cancel this effect. Nonzero Output Resistance • In practical op amps, the output resistance is not zero. Consider inverting amplifier. Place Rout in series with output voltage source Closed loop gain with Rout R A0 out v out R1 R1 v in R 2 1 R out A R1 0 R2 R2 10