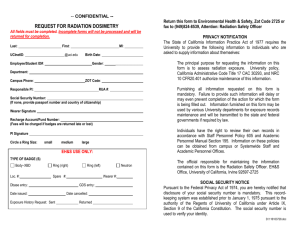

Zot Printed Circuit Division

advertisement