Hardware Pace using Slope Detection

advertisement

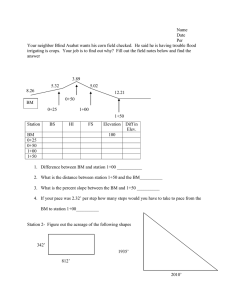

Tony Calabria TI Precision Designs: Verified Design Hardware Pace using Slope Detection TI Precision Designs Circuit Description TI Precision Designs are analog solutions created by TI’s analog experts. Verified Designs offer the theory, component selection, simulation, complete PCB schematic & layout, bill of materials, and measured performance of useful circuits. Circuit modifications that help to meet alternate design goals are also discussed. This hardware pace detection circuit is designed to monitor for occurrences of a pace maker signal in an electrocardiogram (ECG) application by providing an alert to a GPIO. The circuit combines three individual circuits: a differentiator circuit used for slope detection, a window comparator to monitor for an event and SR latch to indicate an event has occurred. A pacemaker signal at the input will latch a digital I/O pin high to indicate the signal is present in the waveform. Design Resources Design Archive TINA-TITM ADS1298 OPA348 TLV3401 SN74LVC2G00DCTR Ask The Analog Experts WEBENCH® Design Center TI Precision Designs Library All Design files SPICE Simulator Product Folder Product Folder Product Folder Product Folder Vcc Vcc R7 R5 V1 C2 R1 + R6 R2 C1 + Alert Out R11 ECG + Pace + – Vbias Vcc R3 + V2 R4 Reset An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other important disclaimers and information. TINA-TI is a trademark of Texas Instruments WEBENCH is a registered trademark of Texas Instruments SLAU511-June 2013-Revised June 2013 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated 1 www.ti.com 1 Design Summary The design requirements are as follows: Supply Voltage: 5V dc Minimum pace signal width: 100µs Minimum pace signal amplitude: 2mV Monitor for slope of pacemaker signal while ignoring ECG signal Set GPIO to indicate pacemaker signal is present The design functionality is displayed below showing a pulse when the slope of the pace maker signal is present. The Differentiator Out signal triggers a falling edge on the window comparator thereby setting the SR latch. ECG + Pace Input Differentiator Out Window Comparator Out SR Latch Out PACE: 20mV Amplitude 100us period Figure 1: Hardware Pace Results 2 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated SLAU511-June 2013-Revised June 2013 www.ti.com 2 Theory of Operation To understand the design approach discussed in this TI Design note, basic pacemaker functionality must first be discussed. The primary role of the pacemaker is to apply a small surge of voltage to the heart, prior to the QRS pulse, to assist with blood flow through the body. The signal can take on a variety of form factors which can be broken down to a specific amplitude and signal width. Figure 2 is used to model a typical QRS pulse with an example of a Ventricle pacemaker signal shown prior. QRS Complex PR Interval R ST Segment T P Pace Q U S QT Interval Figure 2: ECG Signal with Pace The height and width of the pacemaker signal can range anywhere from 2mV to over 500mV in amplitude and 0.1ms to 500ms in width while possibly sharing similar signal characteristics of the ECG pulse. The shape of the signal will differ depending on how the pacemaker is positioned to assist the heart and the type of pacemaker installed. A common characteristic of pacing pulses is to have a very steep rising edge transition which can be used to distinguish from the QRS complex. Using the higher frequency components associated with this steep rising edge can determine if a pacemaker is present. Taking a Fast Fourier Transfer (FFT) of an ECG signal with a pacemaker, the characteristics show that the ECG components lie within the 150Hz and lower range while the pace signal resides in the higher bandwidths, at times 1kHz and greater. Determining if the pace signal is present in an ECG system can be done in a variety of ways. Wide bandwidth ADCs are commonly used to digitize the ECG signal, where post processing can determine if a pace signal appears before the QT interval shown in Figure 2. There are also hardware methods which can be used focused around analog design to determine if the pacemaker signal is present. This TI Design is a hardware pace detection method designed around using slope detection. A complete schematic for this design is shown in Figure 3. The circuit is designed to be specifically used with the ADS1298 which includes an internal differential to single ended converter for the ECG lead. Once routed from the ADC, a differentiator circuit is used for slope detection of the pacemaker signal. A reference voltage, Vbias, is used to add DC bias to the window comparator circuit to allow the circuit to be powered off of a single supply. Resistors set the threshold values for the window comparator prior to the latch stage to indicate an event. The design can be segmented into three stages: Slope Detection, Alert Stage, and Latch to GPIO. SLAU511-June 2013-Revised June 2013 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated 3 www.ti.com Vcc Vcc R7 R5 V1 C2 R1 + R6 R2 C1 + Alert Out R11 ECG + Pace + – Vcc R3 Vbias + V2 R4 Reset Figure 3: Complete Circuit Schematic 2.1 Slope Detection The first stage monitors for the leading edge of the pace signal while attenuating the QRS complex. A differentiator circuit is selected to monitor for the steep leading edge of the pacemaker signal. This circuit takes advantage of the characteristic of current across a capacitor and uses the op amp feedback resistor to develop a proportional voltage. The output from the circuit will reflect a signal relative to the slope, dV/dt, of the input, shown in Figure 4. R1 Vout C1 + Vin + – Vout R1C1 dV Vbias dt Vbias Figure 4: Typical Differentiator Circuit The resistor and capacitor used in this circuit form a high pass filter which is set to monitor for the higher frequency components from the pacemaker signal. Thus, the output will be proportional to the slope amplitude and duration while ignoring the QT interval and being offset by the Vbias voltage. 4 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated SLAU511-June 2013-Revised June 2013 www.ti.com 2.1.1 Circuit Compensation The passive components will set the poles and zeroes for the transfer function and must be selected to ensure stability. A second capacitor, C2, may be placed in parallel with the resistor in the feedback loop to help stabilize the circuit, along with a second resistor, R 2, in the input path. The procedure for selecting the stability network is beyond the scope of this design note; please see reference [1] for a detailed explanation of stability. C2 R1 R2 Vout C1 + Vin + – R11 Vbias Figure 5: Differentiator Circuit with Compensation In order to ensure 40dB gain before compensating for stability, the first order high pass filter for the circuit must begin at around 1Hz. C1 is chosen to be 1µF to set the HPF cut off of the differentiator circuit to attenuate the unwanted QRS complex. Setting R1 to 392kΩ and C2 to 10nF help maximize the gain while keeping the circuit stable. R2 is short circuited to 0Ω but included for design flexibility. R11 is in place as a 1MΩ load resistor for the output. The Vbias voltage is set to 2.5V, the midpoint of the power supplies, to allow the differentiator output maximum swing in either the positive or negative direction allowing design flexibility if the pace maker pulse is of opposite polarity. The Vbias voltage is generated by dividing the 5V supply using two 2MΩ resistors to help conserve power. As mentioned in the modifications section later, a second order high pass filter would help improve gain before compensating for stability. 2.2 Alert Stage The output of the differentiator circuit, discussed above, will produce a pulse when a pace event occurs which must then be recognized to register an alert. By design, this pulse from the output of the differentiator can range anywhere from a few hundred mVs to a couple volts depending on the pacemaker signal characteristics. Capturing the signal is done using a window comparator circuit designed to output a logic low signal when the comparator input pulse exceeds either a high or low threshold voltage. The open drain output window comparator circuit used in the design is shown in Figure 6. SLAU511-June 2013-Revised June 2013 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated 5 www.ti.com Vcc Vcc R6 V1 Vcc R5 R6 R4 V 2 Vcc R3 R 4 R7 R5 V1 + R6 Vin *From Differentiator Vout Comparator Vout Vcc R3 + V2 R4 Figure 6: Window Comparator Circuit The threshold limits, listed as V1 and V2 in Figure 6, are set as a fraction of the power supply determined by the R3, R4, R5, R6 resistor values. When the output from the differentiator circuit, listed as V in, exceeds the set limits V1 or V2, the comparator output will trigger by pulling the comparator Vout line low. Selection of component values is not as straightforward as it is for the differentiator circuit. The boundary limits for the window comparator are dependent on the amplitude of the differentiator amplifier output under the worst case condition, 2mV amplitude and 100µs width pacemaker pulse. Through simulation (shown later) we can estimate a value for the differentiator output amplitude to set the threshold limits of the window comparator, and then make modifications in the verification process. The values chosen are setting V1 to 2.77V and V2 to 2.48V, requiring R3 set to 10.2kΩ, R4 set to 10kΩ, R5 set to 8.06kΩ, and R6 set to 10kΩ. R7 is a weak pull up resistor for the open drain output and will be set to 10kΩ. Vcc is the 5V supply used to power the system. 2.3 Latch to GPIO The width of the comparator output pulse is determined by the time that Vin (from Figure 6) exceeds the window comparator boundaries. This duration can be as small as a few milliseconds and may be missed if not latched. Placing a SR-latch circuit after the window comparator will latch the signal in a steady state to be read back by a microcontroller or DSP until a reset is performed. The SR latch will perform two functions: latching the window comparator out signal, and serving as an inverter to create an active high alert out signal. The design of the SR-latch using two NAND gates is shown in Figure 7. 6 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated SLAU511-June 2013-Revised June 2013 www.ti.com Comparator Vout Alert Out Vcc R8 Reset S1 Figure 7: SR Latch The alert out signal can be routed to a GPIO and the state monitored for a pace event. The R 8 resistor and S1 switch are used to reset the latch. R8 is a weak pull up resistor and will be set to 10kΩ, and S1 is a single pull, single throw (SPST) push button switch. SLAU511-June 2013-Revised June 2013 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated 7 www.ti.com 3 Component Selection 3.1 Differentiator Circuit Amplifier Selection The slope detection circuit has a few requirements on the amplifier selection. The op amp must have adequate bandwidth to respond to the pace signal change on the input before compensation. Earlier it was specified that the minimum pace signal we would like to detect is 100µs in width, therefore, an amplifier of, at least, a decade greater bandwidth is preferred. Depending on the duration of the pace pulse slope, the output may swing close to the power rails, requiring a rail to rail out op amp. The OPA348 was chosen because it has 1MHz bandwidth, is capable of reaching within 25mV of the rail, and maintains adequate bandwidth, while staying cost effective in the TI value line of devices. A wider bandwidth op amp can be selected to provide more flexibility on the high pass filter design prior to compensation for stability. 3.2 Differentiator Vbias Voltage Selection The role of the Vbias voltage is to set the dc operating point to the window comparator input when a pace pulse is not detected. This becomes the idle voltage state of the window comparator input used to set the high and low threshold values of the individual comparators. By setting Vbias to 2.5V, the midpoint of the system power supplies, the swing of individual comparators is maximized in either the positive or negative direction. Adjusting the Vbias value would require that the window comparator threshold voltages are properly set. 3.3 Comparator Device Selection The window comparator circuit design requires two comparators sharing a common output that each has the ability to control. Open drain output comparators allow for either device to pull the line low when the window comparator input voltage exceeds set voltage values. The TLV3401 was chosen for its open drain output and small package option. The TLV3402 is a secondary option as it includes two devices per package. 3.4 NAND Gates for SR Latch Selection Two NAND gates are required for the SR latch design with adequate propagation delay. The SN74LVC2G00 was chosen for its two devices per package and tpd max of under 5ns. A simple push button switch will work for the reset. 3.5 Passive Component Selection The differentiator circuit design and window comparator threshold design are the two paths for which the passive component selection values are critical for this design. To meet the design goal of the differentiator circuit responding to the pace signal, the resistor tolerance values of the passive components setting the high pass filter were chosen to be 1%. Resistors R3, R4, R5, and R6 in Figure 6 set the threshold values for the window comparator. These threshold voltage values may be set very close to the dc operating point set in the differentiator stage, in order to meet the specification of responding to a 2mV amplitude, 100µs period pace signal. Therefore, resistor tolerances of 0.1% were chosen to set the voltages as accurate as possible. When this was not possible due to reasonable cost or availability, the tolerance of the resistor was chosen to be 1%. The TM values, themselves, were obtained experimentally during TINA-TI simulation and then modified based on lab testing. Other passive components in this design may be selected for 1% or greater as they will not directly affect the transfer function of this design. 8 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated SLAU511-June 2013-Revised June 2013 www.ti.com 4 Simulation TM The TINA-TI schematic shown in Figure 8 includes the circuit values obtained in the design process. The first OPA348 in a unity gain buffer configuration is used to model the internal buffer of the ADS1298 prior to the V_PACE_OUT pin. VCC ECG+PACE R6 10k + ECGp + V_PACE_OUT To SR Latch - U3 TLV3401 - OPA348 VPDetect U1 OPA348 + VCC VCC + VCC VCC Vref V1 2.5 + U2 TLV3401 + - R8 10k Vref VCC R7 10.2k + R2 0 + + C1 1u - + R1 1M Vpace Pos R4 392k VECG_block VCC R5 8.06k C2 10n R16 100k Buffer internal to ADS1298 V2 2.5 TM Figure 8: TINA-TI 4.1 Schematic Time Domain Analysis The transient analysis is first performed to get an understanding of the events at each stage of the circuit. ECGp and Vpace Pos are arbitrary waveforms used to model a typical ECG pulse with a 2mV, 100µs pace signal beforehand, similar to what is shown in Figure 2. VPDetect is the output from the differentiator which is used to get an understanding of where to set the voltage threshold levels for the window comparator. V_PACE_OUT is the output from the window comparator which will get pulled low when VPDetect appears outside of the set boundaries. The time domain response is shown in Figure 9. SLAU511-June 2013-Revised June 2013 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated 9 www.ti.com TM Figure 9: TINA-TI - Transient Response The simulation results in Figure 9 are used to make any adjustments to the window comparator levels if a latch does not take place. VPDetect reaches a value of 2.45V when the target of a 2mV, 100µs pace signal is applied to the input. Giving a little room for error, a level of 2.48V is used for the lower limit. 10 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated SLAU511-June 2013-Revised June 2013 www.ti.com 4.2 Step Response The time domain step response of the differentiator stage can be seen in Figure 10 to verify stability. T 779.23m Differentiator Out 1.99m 10.00m Vin 0.00 0.00 100.00m 200.00m 300.00m Time (s) TM Figure 10: TINA-TI - Step Response At the moment of the step input, there is a large spike on the Differentiator Out (VPDetect) relative to the slope before stabilizing to a steady DC value. This is the expected behavior of the differentiator circuit without ringing or oscillations verifying that we have a stable design. SLAU511-June 2013-Revised June 2013 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated 11 www.ti.com 5 PCB Design The PCB schematic and bill of materials can be found in Appendix A. 5.1 PCB Layout The layout of the ECG hardware pace board was designed to pair with the ADS1298ECG-FE board requiring minor modifications to the connecting headers. General layout practices based on the general PCB Layout Guidelines document found on the e2e Wiki were followed. The PCB layout for this design is shown in Figure 11. Figure 11: PCB Layout 12 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated SLAU511-June 2013-Revised June 2013 www.ti.com 6 Verification & Measured Performance 6.1 Time Domain Analysis This circuit is required to pass functionality tests comparing the real-world circuit performance to TM expectations from the TINA-TI simulation and the requirements laid out in the Design Summary. Test points were included in the board design at the VPDetect, V_PACE_OUT, and the SR Latch points out to monitor signal progress through the circuit. Figure 12 displays the transient analysis results when a 20mV amplitude, 100µs period pacemaker pulse is applied prior to the QRS interval. The Fluke Medsim 300B was used to simulate a pacemaker pulse and ECG signal. ECG + Pace Input Differentiator Out Window Comparator Out SR Latch Out PACE: 20mV Amplitude 100us period Figure 12: Time Domain Results (20mV amplitude) A 20mV pace signal amplitude was first selected to show a visual demonstration of how a pace signal (shown on channel 1) will cause the SR latch to change to a high state (shown on channel 4). Once functionality has been proven in Figure 12, a second test is required to demonstrate circuit response to a 2mV amplitude and 100µs period pulse width pace signal. Figure 13 displays the transient analysis for these conditions which can be compared to the Figure 9 simulation results. SLAU511-June 2013-Revised June 2013 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated 13 www.ti.com ECG + Pace Input Differentiator Out Window Comparator Out SR Latch Out PACE: 2mV Amplitude 100us period Figure 13: Time Domain Results (2mV Amplitude) The 2mV amplitude pacemaker signal does successfully trigger the window comparator and SR latch indicating an event. Figure 12 and Figure 13 also show how the amplitude of the differentiator out circuit is dependent on the duration of the input pacemaker slope. This concludes testing verification of the hardware pace detection circuit. 14 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated SLAU511-June 2013-Revised June 2013 www.ti.com 7 Modifications The components selected for this design were based on the design goals and outlined at the beginning of the design process. Those goals are focused on monitoring for a 2mV positive polarity pacemaker pulse that can be as small as 100µs in signal width. In reality, a pacemaker can be positioned in the body a variety of ways, where the monitored pacemaker signal could either read back with positive or negative polarity. Following the design method described above, R5 and R6 can be selected for the circuit to respond to a negative polarity pace signal in addition to the positive pulse. The first order high pass filter and slope detection circuit is designed to demonstrate how manipulation of frequency components can alert a user when a pace maker signal is present prior to the ECG signal. All tests in this document were performed with a Fluke patient simulator, not taking into account any motion artifacts which would be present in a commercial medical system. This circuit is not designed to be used directly with a patient without proper IEC certification. When designed to be used in a patient monitoring system, additional design effort is required to help filter motion artifacts which will cause false positive triggers. The poles and zeroes on the differentiator may need to be manipulated to further attenuate the lower frequency components avoiding unwanted triggers on the window comparator. Additional gain may be required on the differentiator circuit to allow a wider range on the window comparator threshold limits to help with motion artifacts. Adding gain to the differentiator circuit will allow the threshold limits to be pushed further away from the idling voltage, set by Vbias. Designing a second order high pass filter may be required to help attenuate the lower frequency components while providing enough gain at the higher frequencies to help with motion artifacts. A wider bandwidth op amp in the differentiator stage can also help improve the gain before stability compensation. Moving forward, software detection methods are becoming a more accurate way to monitor for a pace maker. Using a wide bandwidth SAR ADC, the ECG and pace signal can be digitized and then processed to remove unwanted signal components. The Q-T interval can be removed, along with electromyography (EMG) signals from muscle movement and any other motion artifacts leaving solely the pace maker signal components. Further algorithms can be put in place to not only alert the user if a pacemaker is present, but also provide details about the pace device. 8 About the Author Tony Calabria is a Systems Engineer and Product Definer in the Delta Sigma ADC group at Texas Instruments where he supports medium to wide bandwidth Delta Sigma ADCs. Tony received his BSEE from the University of Arizona. 9 References 1. Green, T., Operational Amplifier Stability, Parts 1 – 11, November 2008, http://www.engenius.net/site/zones/acquisitionZONE/technical_notes/acqt_050712 SLAU511-June 2013-Revised June 2013 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated 15 www.ti.com Appendix A. A.1 Electrical Schematic Figure A-1: Electrical Schematic 16 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated SLAU511-June 2013-Revised June 2013 www.ti.com A.2 Bill of Materials Figure A-2: Bill of Materials SLAU511-June 2013-Revised June 2013 Hardware Pace using Slope Detection Copyright © 2013, Texas Instruments Incorporated 17 IMPORTANT NOTICE FOR TI REFERENCE DESIGNS Texas Instruments Incorporated ("TI") reference designs are solely intended to assist designers (“Buyers”) who are developing systems that incorporate TI semiconductor products (also referred to herein as “components”). Buyer understands and agrees that Buyer remains responsible for using its independent analysis, evaluation and judgment in designing Buyer’s systems and products. TI reference designs have been created using standard laboratory conditions and engineering practices. TI has not conducted any testing other than that specifically described in the published documentation for a particular reference design. TI may make corrections, enhancements, improvements and other changes to its reference designs. Buyers are authorized to use TI reference designs with the TI component(s) identified in each particular reference design and to modify the reference design in the development of their end products. HOWEVER, NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY THIRD PARTY TECHNOLOGY OR INTELLECTUAL PROPERTY RIGHT, IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services, or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI. TI REFERENCE DESIGNS ARE PROVIDED "AS IS". TI MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO THE REFERENCE DESIGNS OR USE OF THE REFERENCE DESIGNS, EXPRESS, IMPLIED OR STATUTORY, INCLUDING ACCURACY OR COMPLETENESS. TI DISCLAIMS ANY WARRANTY OF TITLE AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, QUIET ENJOYMENT, QUIET POSSESSION, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL PROPERTY RIGHTS WITH REGARD TO TI REFERENCE DESIGNS OR USE THEREOF. TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY BUYERS AGAINST ANY THIRD PARTY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON A COMBINATION OF COMPONENTS PROVIDED IN A TI REFERENCE DESIGN. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, SPECIAL, INCIDENTAL, CONSEQUENTIAL OR INDIRECT DAMAGES, HOWEVER CAUSED, ON ANY THEORY OF LIABILITY AND WHETHER OR NOT TI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES, ARISING IN ANY WAY OUT OF TI REFERENCE DESIGNS OR BUYER’S USE OF TI REFERENCE DESIGNS. TI reserves the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products. Testing and other quality control techniques for TI components are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed. TI assumes no liability for applications assistance or the design of Buyers’ products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers’ products and applications, Buyers should provide adequate design and operating safeguards. Reproduction of significant portions of TI information in TI data books, data sheets or reference designs is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions. Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards that anticipate dangerous failures, monitor failures and their consequences, lessen the likelihood of dangerous failures and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in Buyer’s safety-critical applications. In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms. No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed an agreement specifically governing such use. Only those TI components that TI has specifically designated as military grade or “enhanced plastic” are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components that have not been so designated is solely at Buyer's risk, and Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949. Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated