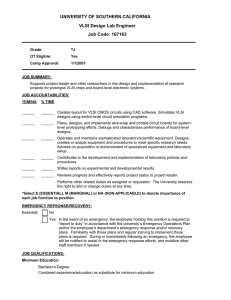

VLSI Design Digital Systems and VLSI Digital Systems and VLSI

advertisement

VLSI Design Digital Systems and VLSI Somayyeh Koohi Department of Computer Engineering Sharif University of Technology Adapted with modifications from lecture notes prepared by 1 author Overview Why VLSI? IC Manufacturing CMOS Technology The VLSI design process Sharif University of Technology Modern VLSI Design: Chap1 2 of 38 Why VLSI? Lower cost 1. • • 2. 3. 4. chip area number of ICs,… Faster Lower power consumption Higher reliability More integration reliability Better testabilit 5. less intra-chip connections better Less design and fabrication time Sharif University of Technology Modern VLSI Design: Chap1 3 of 38 ICs over Discrete Circuits Advantages Size Speed Faster communication Power Consumption Smaller parasitic capacitance & resistance Manufacturing cost Cost reduction for parts other than chip (supply, fan, PCB, …) ASIC might be more expensive than standard IC, but system’s cost will be lower Sharif University of Technology Modern VLSI Design: Chap1 4 of 38 VLSI and you Processors: personal computers Electronic systems in cars Entertainment systems,… DRAM/SRAM Special-purpose processors Sharif University of Technology Modern VLSI Design: Chap1 5 of 38 Levels of Integration SSI MSI Criteria: LSI VLSI Gate count (2-20, 20-200, 200-2000, 2000 +) Pin count Feature size Chip size Function gate & FF, module, subsystem, system Sharif University of Technology Modern VLSI Design: Chap1 6 of 38 Levels of Integration (cont’d) Where to go after VLSI? ULSI (Ultra Large Scale Integration - which is between 500,000 and 10,000,000 transistors), GSI ((Gigantic g Scale Integration g - which is over 10,000,000 transistors). Sharif University of Technology Modern VLSI Design: Chap1 7 of 38 Overview Why VLSI? IC Manufacturing CMOS Technology The VLSI design process Sharif University of Technology Modern VLSI Design: Chap1 8 of 38 Technology Raw material of IC Manufacturing: Silicon Wafers Duringg manufacturingg Photolithographic process: pattern on mask (layout) pattern on wafer Changing the mask with a single fabrication line different ICs Sharif University of Technology Modern VLSI Design: Chap1 9 of 38 CMOS Technology Difference between fabrication technology: type of transistor used Bipolar, nMOS, CMOS Different speed & power characteristics (tradeoff) Sharif University of Technology Modern VLSI Design: Chap1 10 of 38 Moore’s Law Gordon Moore (co-founder of Intel) predicted that number of transistors per chip would grow exponentially (doubles every 18 months) log(#dev) t Obstacles for Moore’s law: 1. 2. 3. Quantity and variety of products which use ICs has had less progress Cost of design verification and test is large Complexity of design makes it difficult to manage it among design and engineering groups Role of CAD tools Sharif University of Technology Modern VLSI Design: Chap1 11 of 38 Moore’s Law plot 109 # transistorss 108 107 integrated circuit invented 106 105 memory CPU 104 103 102 101 100 1960 Sharif University of Technology 1970 1980 1990 Modern VLSI Design: Chap1 2000 2010 year 12 of 38 Cost of fabrication Current cost: $2-3 billion Typical fab line occupies about 1 city block, employs a few hundred people Most profitable period is first 18 months-2 years Sharif University of Technology Modern VLSI Design: Chap1 13 of 38 Cost factors in ICs For large-volume ICs packaging is largest cost testing is second second-largest largest cost For low-volume ICs design costs may swamp all manufacturing costs Wafer size: 8 inch (12 inch) Chip size: 1.5 x 1.5 cm2 Sharif University of Technology Modern VLSI Design: Chap1 14 of 38 Overview Why VLSI? IC Manufacturing CMOS Technology The VLSI design process Sharif University of Technology Modern VLSI Design: Chap1 15 of 38 The VLSI design process Can be part of larger product design Major steps specification p Algorithm design architecture logic design circuit design layout (physical design) Sharif University of Technology Modern VLSI Design: Chap1 16 of 38 The steps Specification Function (what to do) Cost Other requirements Architecture: large blocks Logic Gates Latches Flip-Flops Circuits transistor Estimate speed & power Layout Layout size determines fabrication cost Shapes determine parasitics the circuit speed and power Sharif University of Technology Modern VLSI Design: Chap1 17 of 38 Challenges in VLSI design 1. Multiple levels of abstraction English specification behavior system throughput, design time sequential machines registertransfer function units, clock cycles logic gates logic literals, gate depth transistors circuit nanoseconds rectangles layout microns Sharif University of Technology Modern VLSI Design: Chap1 c cost function unction executable program 18 of 38 Challenges in VLSI design (cont’d) 2. Multiple and conflicting costs Speed Area Cost power, … 3. Short design time (6 months delay Sharif University of Technology losing 33% of the profit) Modern VLSI Design: Chap1 19 of 38 Solutions Techniques to eliminate unnecessary detail: 1. Hierarchical design Divide and conquer: breaking the chip into a hierarchy of components, where each consists of a body and a number of pins 2. Design abstraction U multiple Use lti l levels l l off abstraction b t ti 3. Using CAD tools: tries to solve all the 3 mentioned problems 1. Dealing with multiple levels of abstraction is easier when you are not absorbed in the details 2. Computer programs can analyze cost trade-offs much better Computers are much faster than humans 3. Sharif University of Technology Modern VLSI Design: Chap1 20 of 38 CAD Tools Categories 1. Design entry tools (e.g., schematic capture) Capture a design in machine-readable form for use by other programs Don’t do any real design work 2. Analysis y and verification tools (e.g., ( g , spice) p ) Ease the analysis task Don’t tell how to change the circuit for the desired function/spec. 3. Synthesis tools (e.g., Leonardo) Create a design at a lower level of abstraction from a higher level description. Both hierarchical design and design abstraction are as important to CAD tools as they are to humans Sharif University of Technology Modern VLSI Design: Chap1 21 of 38 Dealing with complexity Divide-and-conquer: limit the number of components you deal with at any one time Group several components into larger components: Transistors form gates Gates form functional units Functional units form processing elements … Sharif University of Technology Modern VLSI Design: Chap1 22 of 38 Hierarchical name Interior view of a component Components and wires that make it up Exterior view of a component = type: body pins cout a b Sharif University of Technology Full adder sum cin Modern VLSI Design: Chap1 23 of 38 Instantiating component types Each instance has its own name: add1 (type full adder) add2 (type full adder) Each instance is a separate copy of the type: cout Add2.a Add1.a a Add1(Full adder) sum a Add2(Full adder) b b cin Sharif University of Technology sum Modern VLSI Design: Chap1 cin 24 of 38 A hierarchical logic design b 1 box1 b 2 box2 x z Sharif University of Technology Modern VLSI Design: Chap1 25 of 38 Net lists and component lists Net list: Component list: net1: top.in1 in1.in net2: i1.out xxx.B topin1: top.n1 top n1 xxx.xin1 xxx xin1 topin2: top.n2 xxx.xin2 botin1: top.n3 xxx.xin3 net3: xxx.out i2.in outnet: i2.out top.out Sharif University of Technology top: in1=net1 n1=topin1 n2=topin2 n3=topine out=outnet i1: in=net1 out=net2 xxx: xin1=topin1 xin2=topin2 xin3=botin1 B=net2 out=net3 i2: in=net3 out=outnet Modern VLSI Design: Chap1 26 of 38 Component hierarchy top i1 Sharif University of Technology xxx Modern VLSI Design: Chap1 i2 27 of 38 Hierarchical names Typical hierarchical name: top/i1.foo component pin Sharif University of Technology Modern VLSI Design: Chap1 28 of 38 Layout and its abstractions Layout for dynamic latch: Sharif University of Technology Modern VLSI Design: Chap1 29 of 38 Stick diagram VDD Q' D VSS φ Sharif University of Technology φ' Modern VLSI Design: Chap1 30 of 38 Transistor schematic + φ' D Q' φ Sharif University of Technology Modern VLSI Design: Chap1 31 of 38 Mixed schematic φ' D Q' φ inverter Sharif University of Technology Modern VLSI Design: Chap1 32 of 38 Circuit abstraction Continuous voltages and time: + v v t t Sharif University of Technology Modern VLSI Design: Chap1 33 of 38 Digital abstraction Discrete levels, discrete time: a a t cout sum full sum adder b t b cin t a a b t cout sum full sum adder t b t Sharif University of Technology cin Modern VLSI Design: Chap1 34 of 38 Register-transfer abstraction Abstract components, abstract data types: 0010 + 0001 + 0011 0100 Sharif University of Technology Modern VLSI Design: Chap1 35 of 38 Top-down vs. bottom-up design Top-down design adds functional detail Create lower levels of abstraction from upper levels Bottom-up B tt design d i creates t abstractions b t ti from f low-level behavior Good design needs both top-down and bottomup efforts Sharif University of Technology Modern VLSI Design: Chap1 36 of 38 Design validation Validation: Any technique which increases confidence in correctness, e.g simulation Verification: Formal proof of correctness Must check at every step that errors haven’t been introduced The longer an error remains, the more expensive it becomes to remove it Forward checking: compare results of less- and moreabstract stages Back annotation: copy performance numbers to earlier stages Sharif University of Technology Modern VLSI Design: Chap1 37 of 38 Manufacturing test Not the same as design validation: just because the design is right doesn’t mean that every chip coming off the line will be right M t quickly Must i kl check h k whether h th manufacturing f t i defects destroy function of chip Must also speed-grade To deliver high quality: Make the chip designer responsible for testing Sharif University of Technology Modern VLSI Design: Chap1 38 of 38