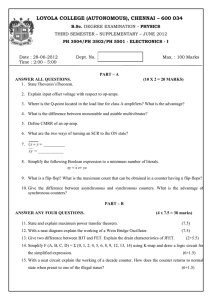

Operational Amplifiers

advertisement