lecture 180 – power supply rejection ratio

advertisement

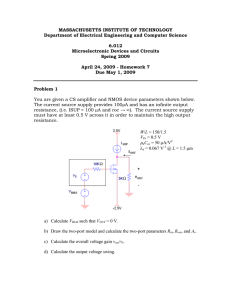

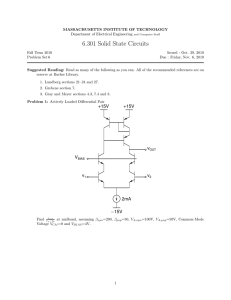

Lecture 180 – Power Supply Rejection Ratio (2/16/02) Page 180-1 LECTURE 180 – POWER SUPPLY REJECTION RATIO (READING: GHLM – 434-439, AH – 286-293) Objective The objective of this presentation is: 1.) Illustrate the calculation of PSRR 2.) Examine the PSRR of the two-stage, Miller compensated op amp Outline • Definition of PSRR • Calculation of PSRR for the two-stage op amp • Conceptual reason for PSRR • Summary ECE 6412 - Analog Integrated Circuit Design - II © P.E. Allen - 2002 Lecture 180 – Power Supply Rejection Ratio (2/16/02) Page 180-2 What is PSRR? Vdd Av(Vdd=0) PSRR = Add(Vin=0) Vin V2 - V1 + VDD Vout Vss VSS Fig.180-01 How do you calculate PSRR? You could calculate Av and Add and divide, however Vdd V2 V2 V1 + Av(V1-V2) VDD Vout Vss V1 VSS Vout ±AddVdd Fig. 180-02 Vout = AddVdd + Av(V1-V2) = AddVdd - AvVout → Vout(1+Av) = AddVdd Vout Add Add 1 ∴V = ≈ = (Good for frequencies up to GB) dd 1+Av Av PSRR+ ECE 6412 - Analog Integrated Circuit Design - II © P.E. Allen - 2002 Lecture 180 – Power Supply Rejection Ratio (2/16/02) Page 180-3 Positive PSRR of the Two-Stage Op Amp Vdd M3 Cc M4 VDD M6 M2 CII CI M5 gm6(V1-Vdd) I3 rds1 rds2 I3 gm1V5 gm2V5 + Vout Vdd M1 1 gm3 rds4 Vdd - I3 gm1Vout gm3 rds5 + M7 V5 - V1 rds6 Cc + rds7 CII CI Vout - VBias V5 ≈ 0 gm6(V1-Vdd) VSS rds4 Vdd gds1Vdd rds2 Fig. 180-03 gm1Vout + V1 - rds6 Cc CI CII + Vout rds7 - The nodal equations are: (gds1 + gds4)Vdd = (gds2 + gds4 + sCc + sCI)V1 − (gm1 + sCc)Vout (gm6 + gds6)Vdd = (gm6 − sCc)V1 + (gds6 + gds7 + sCc + sCII)Vout Using the generic notation the nodal equations are: GIVdd = (GI + sCc + sCI)V1 − (gmI + sCc)Vout (gmII + gds6)Vdd = (gmII − sCc)V1 + (GII + sCc + sCII)Vout whereGI = gds1 + gds4 = gds2 + gds4, GII = gds6 + gds7, gmI = gm1 = gm2 and gmII = gm6 ECE 6412 - Analog Integrated Circuit Design - II Lecture 180 – Power Supply Rejection Ratio (2/16/02) © P.E. Allen - 2002 Page 180-4 Positive PSRR of the Two-Stage Op Amp - Continued Using Cramers rule to solve for the transfer function,Vout/Vdd, and inverting the transfer function gives the following result. Vdd s2[CcCI+CICII + CIICc]+ s[GI(Cc+CII) + GII(Cc+CI) + Cc(gmII − gmI)] + GIGII+gmIgmII Vout = s[Cc(gmII+GI+gds6) + CI(gmII + gds6)] + GIgds6 We may solve for the approximate roots of numerator as sCc s(CcCI+CICII+CcCII) + 1 gmII Cc Vdd gmIgmII gmI + 1 PSRR+ = Vout ≅ GIgds6 sg C mII c + 1 G g I ds6 where gmII > gmI and that all transconductances are larger than the channel conductances. s s sCc sCII + 1 + 1 + 1 + 1 g GIIAvo GB |p2| Vdd gmIgmII gmI mII + ∴ PSRR = V =Gg = gds6 sGIIAvo sgmIICc out I ds6 GIgds6 + 1 + 1 g ds6GB ECE 6412 - Analog Integrated Circuit Design - II © P.E. Allen - 2002 Lecture 180 – Power Supply Rejection Ratio (2/16/02) Page 180-5 Positive PSRR of the Two-Stage Op Amp - Continued GIIAv0 |PSRR+(jω)| dB gds6 0 gds6GB GIIAv0 GB |p2| ω Fig. 180-04 At approximately the dominant pole, the PSRR falls off with a -20dB/decade slope and degrades the higher frequency PSRR + of the two-stage op amp. Using the values of Example 6.3-1 we get: PSRR+(0) = 68.8dB, z1 = -5MHz, z2 = -15MHz and p1 = -906Hz ECE 6412 - Analog Integrated Circuit Design - II © P.E. Allen - 2002 Lecture 180 – Power Supply Rejection Ratio (2/16/02) Page 180-6 Concept of the PSRR+ for the Two-Stage Op Amp Vdd M3 M1 Cc M4 M2 Vout CII CI M5 M7 Vout Vdd VDD M6 Cc Vdd Rout Vout 0dB 1 RoutCc ω Other sources of PSRR+ besides Cc VBias VSS Fig. 180-05 1.) The M7 current sink causes VSG6 to act like a battery. 2.) Therefore, Vdd couples from the source to gate of M6. 3.) The path to the output is through any capacitance from gate to drain of M6. Conclusion: The Miller capacitor Cc couples the positive power supply ripple directly to the output. Must reduce or eliminate Cc. ECE 6412 - Analog Integrated Circuit Design - II © P.E. Allen - 2002 Lecture 180 – Power Supply Rejection Ratio (2/16/02) Page 180-7 Negative PSRR of the Two-Stage Op Amp withVBias Grounded M3 M4 Cc VDD M6 Vout Cc M1 M2 CII CI M5 VBias M7 V ss VBias grounded gmIVout RI CI gmIIV1 CII RII gm7Vss + Vout - VSS Fig. 180-06 Nodal equations for VBias grounded: 0 = (GI + sCc+sCI)V1 - (gmI+sCc)Vo gm7Vss = (gMII-sCc)V1 + (GII+sCc+sCII)Vo Solving for Vout/Vss and inverting gives Vss s2[CcCI+CICII+CIICc]+s[GI(Cc+CII)+GII(Cc+CI)+Cc(gmII −gmI)]+GIGII+gmIgmII Vout = [s(Cc+CI)+GI]gm7 ECE 6412 - Analog Integrated Circuit Design - II Lecture 180 – Power Supply Rejection Ratio (2/16/02) © P.E. Allen - 2002 Page 180-8 Negative PSRR of the Two-Stage Op Amp withVBias Grounded - Continued Again using techniques described previously, we may solve for the approximate roots as sCc s(CcCI+CICII+CcCII) + 1 gmII Cc Vss gmIgmII gmI + 1 PSRR- = Vout ≅ GIgm7 s(C + C ) c I GI + 1 This equation can be rewritten approximately as s sCc sCII s + 1 +1 + 1 + 1 GB |p | g g G A Vss gmIgmII mI mII 2 II v0 PSRR- = Vout ≅ GIgm7 = g g sC s c m7 mI +1 G + 1 G GB I I Comments: PSRR- zeros = PSRR + zeros DC gain ≈ Second-stage gain, PSRR- pole ≈ (Second-stage gain) x (PSRR+ pole) Assuming the values of Ex. 6.3-1 gives a gain of 23.7 dB and a pole -147 kHz. The dc value of PSRR- is very poor for this case, however, this case can be avoided by correctly implementing VBias which we consider next. ECE 6412 - Analog Integrated Circuit Design - II © P.E. Allen - 2002 Lecture 180 – Power Supply Rejection Ratio (2/16/02) Page 180-9 Negative PSRR of the Two-Stage Op Amp withVBias Connected to VSS M3 M1 M4 M2 Cc VDD M6 Vout CII CI Cc Vss M5 VBias M7 V ss rds5 gmIVout CI RI + V1 gmIIV1 - Cgd7 rds7 CII rds6 + Vout - VSS VBias connected to VSS Fig. 180-07 If the value of VBias is independent of Vss, then the model shown results. The nodal equations for this model are 0 = (GI + sCc + sCI)V1 - (gmI + sCc)Vout and (gds7 + sCgd7)Vss = (gmII - sCc)V1 + (GII + sCc + sCII + sCgd7)Vout Again, solving for Vout/Vss and inverting gives Vss s2[CcCI+CICII+CIICc+CICgd7+CcCgd7]+s[GI(Cc+CII+Cgd7)+GII(Cc+CI)+Cc(gmII−gmI)]+GIGII+gmIgmII Vout = (sCgd7+gds7)(s(CI+Cc)+GI) ECE 6412 - Analog Integrated Circuit Design - II © P.E. Allen - 2002 Lecture 180 – Power Supply Rejection Ratio (2/16/02) Page 180-10 Negative PSRR of the Two-Stage Op Amp withVBias Connected to VSS - Continued Assuming that gmII > gmI and solving for the approximate roots of both the numerator and denominator gives sCc s(CcCI+CICII+CcCII) + 1 gmII Cc Vss gmIgmII gmI + 1 PSRR- = Vout ≅ GIgds7 sC s(C +C ) gd7 I c +1 G + 1 g I ds7 This equation can be rewritten as s s + 1 +1 Vss GIIAv0 GB |p2| PSRR- = V ≈ g sCc out ds7 sCgd7 gds7 +1 GI + 1 Comments: • DC gain has been increased by the ratio of GII to gds7 • Two poles instead of one, however the pole at -gds7/Cgd7 is large and can be ignored. Using the values of Ex. 6.3-1 and assume that Cds7 = 10fF, gives, PSRR-(0) = 76.7dB and ECE 6412 - Analog Integrated Circuit Design - II Poles at -71.2kHz and -149MHz © P.E. Allen - 2002 Lecture 180 – Power Supply Rejection Ratio (2/16/02) Page 180-11 Frequency Response of the Negative PSRR of the Two-Stage Op Amp with VBias Connected to VSS ;; ;; ;; ;; ;; GIIAv0 gds7 |PSRR-(jω)| dB Invalid region of analysis 0 GI Cc GB |p2| ω Fig. 180-08 ECE 6412 - Analog Integrated Circuit Design - II © P.E. Allen - 2002 Lecture 180 – Power Supply Rejection Ratio (2/16/02) Page 180-12 Approximate Model for Negative PSRR with VBias Connected to Ground M3 M1 M4 M2 M5 VBias Cc VDD M6 Vout VBias CII CI M5 or M7 iss Vss VSS M7 V ss VSS VBias grounded Fig. 180-09 Path through the input stage is not important as long as the CMRR is high. Path through the output stage: vout ≈ issZout = gm7ZoutVss Vout 1 ∴ V = gm7Zout = gm7Rout sR C +1 ss out out Vout Vss 20 to 40dB 0dB ECE 6412 - Analog Integrated Circuit Design - II 1 RoutCout ω Fig.180-10 © P.E. Allen - 2002 Lecture 180 – Power Supply Rejection Ratio (2/16/02) Page 180-13 Approximate Model for Negative PSRR with VBias Connected to VSS M3 M4 M1 M2 Cc Vout rds7 CII CI M7 VBias Vss rds7 Vss M5 What is Zout? Vt Zout = I ⇒ t VDD M6 vout Zout Path through Cgd7 is negligible VSS VBias connected to VSS Fig. 180-11 gmIVt It = gmIIV1 = g GI+sCI+sCc GI+s(CI+Cc) Thus, Zout = gmIgMII mII It Cc CII+Cgd7 gmIVout CI RI + V1 gmIIV1 - rds6||rds7 + Vout - Vt Fig.180-12 ∴ rds7 1+ Vss Zout s(Cc+CI) + GI+gmIgmIIrds7 Vout = 1 = s(Cc+CI) + GI ECE 6412 - Analog Integrated Circuit Design - II Lecture 180 – Power Supply Rejection Ratio (2/16/02) -GI ⇒ Pole at C +C c I © P.E. Allen - 2002 Page 180-14 The two-stage op amp will never have good PSRR because of the Miller compensation. ECE 6412 - Analog Integrated Circuit Design - II © P.E. Allen - 2002 Lecture 180 – Power Supply Rejection Ratio (2/16/02) • • • • Page 180-15 SUMMARY PSRR is a measure of the influence of power supply ripple on the op amp output voltage PSRR can be calculated by putting the op amp in the unity-gain configuration with the input shorted. The Miller compensation capacitor allows the power supply ripple at the output to be large The two-stage op amp will never have good PSRR unless some modifications are made. ECE 6412 - Analog Integrated Circuit Design - II © P.E. Allen - 2002