SJSU Annual Program Assessment Form Academic Year 2013-2014

advertisement

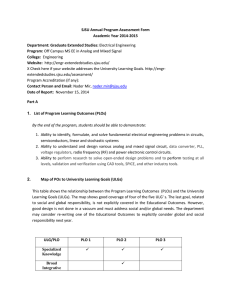

SJSU Annual Program Assessment Form Academic Year 2013-2014 <Please replace the <...> in this template with the requested text, and then delete these instructions prior to submission. The completed forms will be posted under Annual Assessment Reports on the Program Records webpage (http://www.sjsu.edu/ugs/faculty/programrecords/index.html) for your department. Electronic copy of report is due June 1, 2014. Send to Undergraduate Studies (academicassessment@sjsu.edu), with cc: to your college’s Associate Dean and college Assessment Facilitator. List of AFs is found at http://www.sjsu.edu/ugs/faculty/programs/committee/index.html> Department: Graduate Extended Studies: EE Program: Off Campus Programs: EE in Analog and Mixed Signal College: Engineering Website: http://engr-extendedstudies.sjsu.edu/ X Check here if your website addresses the University Learning Goals. http://engrextendedstudies.sjsu.edu/assessment/ Program Accreditation (if any): Contact Person and Email: Nader Mir, nader.mir@sjsu.edu Date of Report: June 1, 2014 Part A <In the 2013-14 AY, we would like to establish a baseline for all degree programs on campus, and we ask that you fill out Items 1 – 5 for all degree programs in your department. In subsequent years, you will only need to note changes from the baseline year.> 1. List of Program Learning Outcomes (PLOs) <Please list PLOs and indicate how faculty decides on PLO content and criteria for assessing levels of mastery. The PLOs should be appropriate to the degree and consider national disciplinary standards. Each outcome should describe how students can demonstrate learning.> Program Educational Objectives List PLOs PLO1 Be a practicing engineer in fields such as design, research, testing and manufacturing PLO2 Engage in lifelong learning to maintain and enhance professional skills PLO3 Fulfill the needs of society in solving technical problems using engineering principles, tools and practices, in an ethical and responsible manner Within five years of graduating from this program, engineers should have: PLO4 Demonstrate leadership skills in the workplace and function professionally in a globally competitive world University Learning Goals (ULGs) ULGs By the end of the program, students should be able to demonstrate: ULG1 Ability to identify, formulate, and solve fundamental electrical engineering problems in circuits, semiconductors, linear and stochastic systems ULG2 Ability to understand and design various analog and mixed signal circuit, data converter, PLL, voltage regulators, radio frequency (RF) and power electronic control circuits. ULG3 Ability to perform research to solve open-ended design problems and to perform testing at all levels, validation and verification using CAD tools, SPICE, and other industry tools. 2. Map of PLOs to University Learning Goals (ULGs) <Please indicate how your PLOs map to the University Learning Goals. Describe the collaborative process used to create or interpret the map.> PLOs ULGs ULG1 ULG2 PLO1 X PLO2 X X PLO3 X X PLO4 ULG3 X 3. Alignment – Matrix of PLOs to Courses <Please show in which courses the PLOs are addressed and assessed. Curriculum map should show increasing levels of proficiency and alignment of curriculum and PLOs.> Courses EE227 EE189A EE223 EE221 EE239 EE210 X X X X X PLO1 PLO2 X PLO3 X X PLOs Courses PLO1 EE228 EE250 EE220 EE229 EE297A EE297B X X X X X X X X X X X X X X PLO2 PLO3 X 4. Planning – Assessment Schedule <Please indicate a reasonable, multi-year assessment plan that describes PLO assessment and improvement of achievement, as well as other assessment activities.> Collected (C) , discussed (D), and implemented changes(I) POs F10 S11 F11 1 - C,D C,D 2 C,D C,D 3 C,D C,D S12 F12 S13 F13 S14 C,D C,D,I C,D C,D C C,D C,D C,D,I C,D C C,D C,D C,D,I C,D C C,D C,D F14 5. Student Experience <Please indicate where your PLOs and the ULGs are communicated to students, e.g. websites, syllabi, promotional material, etc., and whether student feedback is considered in the creation of the PLOs.> PLOs and the ULGs are communicated to students, through e.g. websites, syllabi Part C 6. Closing the Loop/Recommended Actions <Please list all ongoing recommended actions for your program. Recommended actions might arise from: the previous program planning cycle, feedback from a previous annual assessment report, or other feedback. Indicate and describe activities undertaken this year designed to improve learning and/or program quality and health.> N/A 7. Assessment Data <Please briefly describe the data collected for this report (i.e. how, when and why). The data can address achievement of PLOs and/or recommended actions. The instruments used and actual data can be attached as appendices as appropriate. > The assessment data were collected in the form of course learning objectives (CLOs) at the end of each course, course assessment journals (CAJs) at the end of each course, and oral interview with selected students time-to-time. 8. Analysis <Please discuss data and evaluate achievement of PLOs and/or progress on recommended actions. Please consider the composition of your students in your interpretation, if applicable. > In EE288, all CLOs 1, through 8 contributed to this PLO. The direct measurement: the acceptable students’ performance criteria are collectively set at score 70%. All CLOs were achieved by an overall average of 74.00% of the students as assessed by exam and homework questions. As a result, the performance criteria were achieved. The indirect measurement: for Part 1 (importance of course topic), the acceptable performance is set at “B” or 3.75/5.00 and acceptable percentage of students who pass the above score is also set at 75%. Overall, the average class score given by students is: 4.78/5.00, and 100% of all students met the acceptable performance. For Part 2 (portion learned and achieved), the grand average class score by students is: 4.32/5.00, and 100% of all students met the acceptable performance. In EE228, all CLOs 1, through 5 contributed to this PLO. The direct measurement: the acceptable students’ performance criteria are collectively set at score 75%. All CLOs were achieved by an overall average of 90.33% of the students as assessed by exam and homework questions. As a result, the performance criteria were achieved. The indirect measurement: for Part 1 (importance of course topic), the acceptable performance is set at “B” or 3.75/5.00 and acceptable percentage of students who pass the above score is also set at 75%. Overall, the average class score given by students is: 4.90/5.00, and 100.0% of all students met the acceptable performance. For Part 2 (portion learned and achieved), the grand average class score by students is: 4.52/5.00, and 100% of all students met the acceptable performance. 9. Proposed changes and goals (if any) <Please list proposed changes and goals for the next academic year and the future, and identify areas to be assessed. > In EE288, students gave informal feedback regarding the course material, pace of the course, teaching and etc Students generally felt that the time is short and course materials are advanced and hard to understand with fast pace. They like to have another advanced analog class. Students appreciated using tablet for writing on slides and sharing them at the end of each class on dropbox. Plans are: Extra material such as TDC should be added to syllabus The course syllabus has to be updated to Verilog-A instead of Matlab. Will be in effect for the next time offering the course to have more details on circuit level implementation of Delta-Sigma Modulator Will be in effect for the next time offering the course to have a video on ADC testing or have National Instrument to have a demo of new tools such as NI PXI for students In EE228, In Exam 2, Question 2 indicated that only 30% of students showed proficiency. This is due to 2 factors. Exam 2 had a lot of extra-credit problems that would not fit the allocated time so many students stirred away from this question perhaps due to its difficult and extensive calculations too. The second factor is that this material was covered in a prior course. It was condensed again in one class and the students might have felt it was too much. This is the circuit design part of the course and more time could have been allocated for it. Extra class with step-by-step circuit design real example should be added to the course covering and revising basic analog circuit design and stressing the practical design aspect of the course