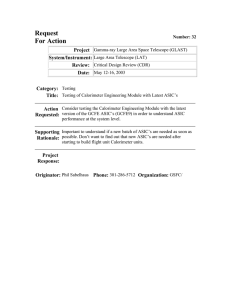

5x5 Pixel Array Status 17 Dec 2003 Sam Burke Sean Stromberg

advertisement

5x5 Pixel Array Status 17 Dec 2003 Sam Burke Sean Stromberg UCSB HEP Group UCSB ASIC BiWeekly Status Meeting Slide 1 ASIC Progress • AMI CMOS 0.35 Design Kit 2 Received Design Manual C035MD Ver 5 Design Manual C035MA Ver 3 Core Cells, D Scan FF’s, LVDS Library Pad Limited and Core Limited I/O Cells Ver 1.8 Databook, Ver1.0 Technology Info UCSB ASIC BiWeekly Status Meeting Slide 2 Transmission Gate • The Trans-Gate will be one of the building blocks for the D FlipFlop along with inverters. V 0 volts 1 2 3 Rs 2100 ohms 3000 4500 6500 • Load Resistor will be needed if float causes voltage decay lag problem UCSB ASIC BiWeekly Status Meeting Slide 3 Transmission Gate • Pulse Response Cload= .08pf Rload=1meg Tplh=330ps UCSB ASIC BiWeekly Status Meeting Slide 4 Work Plan • Characterize AMI035 min-size transistors transfer curves characteristic curves size • Generate desired parameters for inverter Td h/l Td l/h Vsw-Td with 1-Inv load Td with 4-Inv loads Match h/l and l/h Td’s? • Simulate Ring Oscillator with inverter determine Td or Fmax • Define desired D Flip Flop with Clear UCSB ASIC BiWeekly Status Meeting Slide 5 DFFR • D Flip Flop with Reset 4 inverters 4 transmission-gates 2 2-input NAND 24 separate FET’s in design! Active low reset UCSB ASIC BiWeekly Status Meeting Slide 6 DFFR Simulation Goals • • • • • • • Ts: Setup time > 0.13ns Th: Hold time > 0.11ns Tclk-min: Minumum clock pulse width > 0.20ns Trec: Recovery time > .06ns Fclk-max: Max Clock Freq < 950 Mhz Td: Delay time < 0.53 ns Size: 50 x 12 u (600 u^2) Reference times based AMI035 FD2SS specs (AMI std-cell design data book) UCSB ASIC BiWeekly Status Meeting Slide 7 DFFR Spice Results UCSB ASIC BiWeekly Status Meeting Slide 8 DFFR Spice Results UCSB ASIC BiWeekly Status Meeting Slide 9 DFFR Spice Net List UCSB ASIC BiWeekly Status Meeting Slide 10 DFFR Simulation • Critical D Flip Flop time delays are compared to those stated for the AMI FD2SS D Flip Flop Using L=0.35u, W=0.8u which is the minimum size transistor. If W2 = 3W1 then high-low and low-high transitions will be equal and clocking rate will increase, see analysis which follows. • Delay Time Td AMI Std Cell – <0.53 ns DFFR Simulation 5.2 ns ? • Max Clock Frequency Fclk-max – 950 Mhz UCSB ASIC BiWeekly Status Meeting 96 Mhz Slide 11 Ring Oscillator • Inverters have W2=W1 which results in unequal propigation delays. Tphl= 0.9 ns Tplh=1.3 ns UCSB ASIC BiWeekly Status Meeting Slide 12 Ring Oscillator Revised • W2=3W1 for near equal prop delays Tphl=732ps Tplh=589ps UCSB ASIC BiWeekly Status Meeting Slide 13