>> Ray Bittner: Good morning. I'd like to... He's our local field applications engineer, and today he's going...

advertisement

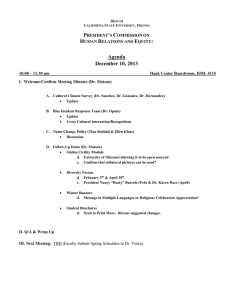

>> Ray Bittner: Good morning. I'd like to welcome back Don Matson from Xilinx. He's our local field applications engineer, and today he's going to be talking about the PlanAhead tool. >> Don Matson: Thank you, Ray. So what you can see here, we advertise this as PlanAhead, and you guys all know that the present version of software is 10.1. But we are going to be releasing 11.1 next month. And so I wanted to talk a little bit about 11.1 features and what's going on there. And so I've sort of broke the talk into two parts. And, actually, there's a third thing. I want to do a demo on PlanAhead and actually demo PlanAhead 11.1. And for those of you who have used PlanAhead, it looks very similar. So the first section will talk about why you would use PlanAhead, and then the second one will talk about what's new in 11.1. And then I'll do the demo. And the big thing that you need to know about that's going on is we're changing how we're releasing our tool set. So the base tool set that everybody has that's here today is our ISE 11 or 10 software. Some of you have ChipScope. I believe you guys have one PlanAhead license at least. So what we're doing is we're going to bundle everything, and so at 11 it becomes an integrated design suite is what we're calling it, so all of those tools are part of the base platform. And then the only options are if you want to do embedded design, you can get an embedded design toolset. So before I get going too far on PinAhead, or a PlanAhead portion called PinAhead, can I see a show of hands? Who's used PlanAhead in any form? Okay. So we've got a couple guys who've used it. So one of the things we've done is in PlanAhead there's some capabilities for doing floor planning and I/O placement, and in 10.1, all 10.1 seats had a light version of PlanAhead, and that feature was what we called PinAhead, and that was the idea of what do I need to get done for laying out the board and assigning the FPGA pins. And for most of the customers I/O work with, when they're doing a board design, they're actually doing the board design before the FPGA is done and they need to know, well, what are the optimal I/Os to chose, what do I need to be concerned with with banking with the different I/O banks and voltage rules and things like that. And so the PinAhead portion is designed to help cover that. And for those who've looked at PlanAhead this looks fairly familiar. You'll see here's the pins, and this is the FPGA itself right here where -- this is your gigabit transceivers on the edge center the center column. I'm going to grab a different light pointer because I've got one that will be easier to see. So this is the center columns where my clockings go. These are the B-RAM banks on the other side. And so that's what I get. I have the ability down here to see what's in the different I/O banks and then the different I/Os. So that's what's in there. And you have the ability to easily create and capture your design there or manage your I/O ports, and then we do our design rule checks to verify that, hey, you haven't put I/O standards, incompatible I/O standards in the same banks and things like that. I can also review the package and pin data. I can sort the data easily because I can -- and I can do it in a couple ways. I can either click on these column headers and see what are at the different VCCO voltages, I can look for the VREF pins. It has the full name of the pin in there. And then also, if you're doing really high-speed design, we have the max trace delays in there as well, so you can do some trace link matching for high-speed LVDS. One of the things you can see on here, this should look very familiar, it's a simple spreadsheet. So one of the things you can do is you can take and import or export from either HDL, a top net list. If I'm going VHDL, I don't need the architecture pair. I can have an empty architecture just have an entity or I can do all my initial design by assigning pins into my spreadsheet and then have it create the UCF and the top level HDL for me, whether it's Verilog or VHDL. So I have that ability to do that. And then you can kind of see, I have easy ways to see what signal the names are and do my sorts real easily that way. And that's the way I kind of prefer to do it initially as just pulling it in that way. And then obviously if we're doing a really large design, it may be that I don't really care about where do the pins go, where do they get placed. It has the ability to use some intelligence and place the I/Os in a safe manager for you so that you can -- you don't have to worry about that. And then the other thing I guess is part of that initial floor planning, you know that there are different buffer types. For high-speed design we have clocks coming in on the regions. They come into a buff I/O buff R. There's some restrictions as to how far -- how many banks can I go up or down. And I have the ability in this PinAhead portion to understand that and make sure that I'm assigning I/Os such that I can take advantage of the resources that are in the FPGA. Yes? >>: When you say automatic, it just looks at the standards and the [inaudible] doesn't look at my design or the board design, does it? >> Don Matson: Yeah. When I'm saying automatic, it does not look at the board design, but it does look at your chip and it can be -- I can tell it that this group of logic has a related clock, and I can tell it that a signal is a clock and it'll make sure that the clocks are placed appropriately. And the other thing is with the transceivers, if you use the high-speed transceivers Vertex 5, there's some pins that if you're using the transceiver we say, hey, if they're too close on the package to the transceiver, there can be potential cross-talk introduced in the package. So we say don't connect there, and so it'll automatically do that as well. Also, you can say, hey, I'm going to prototype in this larger device, make it compatible with a smaller device, and then it will lock out the pins that aren't there or vice-versa. So I just mentioned the DRCs, and this is just showing what the DRCs look like. So here's the DRC, and I highlight it and it'll show up down here as to where it is, and I can then look at the results and make some changes as necessary. This other one is for these larger devices where I have 500 pins. A lot people are doing high-speed memory interfaces, you know, either 32 or 64 bits or 144 bits. And it's pretty easy to get a lot I/Os switching at a very high speed simultaneously. And so the tool is able to do some analysis on that. We have some app notes out there about it, and the calculations have been put into the PlanAhead to do those initial checks. And as I said before, I can export to a CSV. I can also import from it. And here you've just got the list of what I can export and import from. I can either start from a HDL file and a UCF and then go to a CSV or start from a CSV and go the other way. So is makes it a lot easier to do the initial works on the assigning pins. So the whole idea there is to make it a lot easier and quicker to determine the package pins. And the other thing I should say, [inaudible] asked about does it really know much about the board. We've been working with -- Mentor has something called I/O Designer that I've seen a couple of companies use for doing the board level, and so it can work in conjunction with that. So that was the PinAhead capability. That is something that you all have as part of the ISE 10.1 that you have today. Now moving into talking about some of the features that are in PlanAhead itself, so let me give you just a little bit of history. And I think it was about five years ago, there was a company called Higher Design. They had received some initial funding from Xilinx, and they had started off working on this whole idea of building a better floor plan or to help get improved results. At that point in time it only took in EDIF as its input. So today you can take in EDIF, NGC or HDL. HDL was new in 10, and I think that'll probably be the more important way. Once you start playing around with it, I just -- I just got an email this morning from one of my customers who's been doing some work through PlanAhead, and he was amazed at how nice it was and how good it has been in their design. And they use a couple of our Vertex 5 LX 220 sized devices, and there's some things that you can do in seeing how to floor plan things that it allows it to do a better job of meeting timing. And so I think you'll see some of that if you start to use it. As you can see here, I can do the normal things you would expect with HDL. It does have an RTL schematic viewer, and that schematic viewer is better than what you saw in XST. I don't know if you used that much. It's a little better. And just so, you know, there's another company out there, they were purchased by Synopsis, it's called Simplicity, they have an RTL analyst that -- it's not at that level. Let's just say that. There's a reason you pay big money for that one. So just so you're aware, it's better -- it's getting better. Just be aware of that. And then you can do resource estimations. And then when you get your resource estimations, you can export those to spreadsheets once again so you can kind of keep track of them. The other thing you can do, and this is showing the schematic viewer. This schematic viewer should look kind of like what you saw in XST, kind of block. And what I want to point out is in 11 we've switched our synthesis engine. Just so you're aware, as we move from ISE 10, because I think everybody here uses XST, we have something called XST version 11. We're going to a third-party company that builds an industry standard HDL parser. The company's [inaudible]. I don't know that it really makes a lot difference who it is. But the importance for that is what you care about is that it will give us a much better job of language parsing. It gives us a good roadmap to system Verilog or additional support on language constructs. And so that's what we're doing. So when you get ISE 11 and you start playing around with it, be aware, there are two versions of XST. XST 10 and XST 11. By default, if you're using Vertex five or any of the older architectures, you will get XST 10. Now, one of the things I noticed as I was playing around with PlanAhead, by default, it's going to XST 11. And there's some nice things that happen by going with an industry standard front end for the HDL is if you think about it, it doesn't matter whether you're writing code for Xilinx or [inaudible] or anything else. There are certain bugs that happen that you're concerned with, and it'll flag warnings on, you know, latches in your design, it'll flag warnings at the synthesis level for -- if you use cores that are older versions of the core that are not recommended, it'll check some of those kind of things, which should be useful in improving things. So the other thing, you might not understand what this little picture is trying to show here. I guess this is also showing it hierarchically, but this is a hierarchical block. This is the top level. Then it's saying if I go down one level, I have this block and then I have block here, and I just can keep ongoing down. This is another way of you'll have it hierarchically. One of the nice things that PlanAhead does is, if you think about doing your design and you write your code, you have all these modules in it, and it has this thing called P-blocks, which is sort of like a virtual module. And what's highlighted here is just a couple of them, and so now what I can do is I can -- in the PlanAhead level, I can say take this block and this block here and call them a group. It's a P-block. And give it a name, and then, hey, these things need to be put together. And that can help with the timing, and then when I'm doing exploration, I can look at how much interaction I have between modules. The other thing that it has is something we call TimeAhead. You should be getting this sort of -- naming nomenclature down, somebody had some fun with it. But what TimeAhead does is it allows me to take a module and say, hey, how fast will this module run. I don't have to compile the whole design. And then you can see the very first thing here is I can calculate the timing very simply. So it'll give you an estimated routing delay, or I can take that module and kick it off and do a compile by itself. Now, when I'm saying that, I need to let you know that -- and we've talked a little bit about where we're going with partitions and the timing on that. The method that we had to use in ISE 10 is not as good as it is in ISE 11. In a 11, it gets much easier to take and take a module and say, hey, I only want to export this module because that's what I'm working on, and I want to know what kind of timing can I expect in this module, and it will do that for you. And it will run it through the ISE tool's standalone. >>: [inaudible]. >> Don Matson: What's that? >>: [inaudible]. >> Don Matson: Yes. So the question is, is if it's a memory controller or something else where I have both external and internal pins, yes, I can do that. I've got another slide. We'll talk about some potential gotchas on doing something like that. And that is really, when you want to do something like that, okay, well, I have my pin constraints. Are those all in a top-level UCF, and, you know, what am I doing. And ISE 10 allows multiple UCFs, and so if I were going to do something like that, I really want to have an UCF for that module. Now, PlanAhead accepts only one UCF, so you've got to be aware of that. We already talked about rule checking. I guess the one thing I should mention here is there is now rule checking on synthesis as well. So what I was really -- I was talking about there was running a module and looking at it with TimeAhead. There's another thing called ExploreAhead, and we've been promoting this for a while now as the way to do -- get better results. I think some of you guys who have been around long enough with Xilinx, you're aware of this idea of multipass, place and route. If you think about it now in today's world, the biggest area to impact the result is at the * synthesis level. Then the next biggest area is map, and the last area is place and route. By the time it gets to place and route, I don't have nearly as much ability to impact the overall speed of the design. With ExploreAhead, I have the ability to set up runs that either do synthesis or the implementation and use different strategies for design. And then we have this incremental design flow where I use the place and route from the previous design to guide my present place and route. And so what we have is I've seen some companies with these larger devices, what they'll do is they'll run ExploreAhead to try and find what are the best settings, you know, do I need to run with register retiming in synthesis or do I run in global optimization, do I run map dash timing, what are the best options to get a result. And so this just allows me to manage that, it allows me to kick off multiple jobs, and it's limited today on multiple jobs on sort of that operating system you guys probably don't like, but on a Windows environment, it will look at the number of CPUs. So you have CPUs available in your box, so you could kick up off to four jobs and tell it to run four jobs simultaneously. If you do that, though, of course, don't expect to do anything else on your machine. >>: [inaudible]. >> Don Matson: Yes. Well, I think the issue has been our support in Vista 64 has been where we need to really get that to go and that that has been, you know, sort of our schedule, 10 came out. So is that was a year ago in January when that was being released in Vista 64 -- you know, by the time we get back -we've had issues there. And so ->>: I was thinking more like the [inaudible]. >> Don Matson: Okay. >>: Since we seem to be so [inaudible]. >> Don Matson: Uh-huh. So that's not a Vista operating system? >>: [inaudible]. >> Don Matson: Oh, Windows server? >>: [inaudible]. >> Don Matson: Yeah. So our primary platform has been Windows, and -- anyway. So I guess that's a question to ask. It seems like a reasonable way to go. But we are doing things, and part of the reason for the switch is, as Michael had mentioned earlier, in 10 you have ISE with PlanAhead separate. Now we're integrating with 11. With 12 the primary gooey we expect to be PlanAhead. And that has the ability to do a much better job with multi-threading, and that's where we're going. So this is just showing how I can manage it. Kind of the question, what other things can I do with these tools. And one of the things is just how do I visualize, how do I find out what's going on, where are the bottlenecks in the design, and, you know, you can cross-probe, you can easily see from the timing analyst. I will just skip over this and try and show you these things when I show you the demo. The whole pointing is, is faster timing closure. The one thing I want to highlight is this is what I called earlier as a P-block, kind of showing, hey, I've taken two modules, stuck them together logically, and then when I do that I can see how they are interconnected to other modules in the design. And that's part of figuring out how to do a reasonable placement of things. The other thing that you can do is sometimes you want to compress areas in your design. You can give them areas and really force them, you know, something off into a corner, maybe it's not timing critical, or you can force things to be compacted. Obviously you can't -- you guys probably have done enough designs to know that certain things, you can't force them to be in these nice rectangular areas because they interact with things throughout the rest of your design. But depending upon how your design is structured, you can potentially take can and make some area groups for modules or P-blocks and force those to be very highly optimized as far as usage. And then the whole place where we're going with this with the whole idea with partitions, with partial reconfiguration and basically IP reuse are the big things. You know, the idea that I can take a module, lock it down, and export it and then import it into another project and reuse it without spending as much time on timing closure, that's, you know, the major thing we're after. So that's kind of a quick walk-through on the features of PlanAhead. Now I want to talk a little bit about what's new in 11 for you. >>: Can I ask you one thing? >> Don Matson: Sure. >>: [inaudible] this is PR, so, I mean, there's nothing mainline here, but [inaudible]. >> Don Matson: Uh-huh. >>: One comment I've got is that we looked at timing violations [inaudible] so that's not a very reliable method. And, yes, we should be looking at the [inaudible]. >> Don Matson: Yeah. >>: Is there a way to better [inaudible] since you're going into this [inaudible] thing. I don't know, say this module achieves that and according to your [inaudible] so you could have [inaudible] tools that work on that? >> Don Matson: Yeah. So I think your overall question is whether I'm doing a partial reconfigure or an individual region. I really need to be able to verify that if I meet timing in my region, that I'm able to meet it in the system. And one of the problems was in the old partitions flow, you remember those macros that you put in there, those bus macros, and what we needed to be able to do it say, hey, when I compile my basic design I want to compile to the endpoint of the bus macro and say, hey, so that basically becomes a clocked-out time constraint. And then from the bus macro into my design, you know, basically that becomes an offset in constraint in my design. But we weren't able to do that. What we're doing with the newer flow is there are no bus macros, and we're able to time to the input pin of the LUT. And so now we're able to say, hey, I can have a separate constraint for my region or my module and I can constrain, hey, I'm going to give it X amount of time to get there and I'm going to give my other design x amount -- y amount of time to get there and then I can -- I have to allow some additional slack to make sure that everything is going to meet timing. But that ->>: Not only that, but also across [inaudible] designs that go into the region. >> Don Matson: Right. But if they meet their -- they're going to use the same timing. If they meet it, then they will work. And that's the idea of making it more repeatable. And so the issue was before, we weren't able to time across those module boundaries. We've got a solution that we're working on today to do that. It's still not perfect because I've timed it here and there's still a small amount of time that I have to allow for additional routing to make sure everything is stitched up. But I think that will go a long ways to -- whether you're doing partial reconfiguration or trying to take a piece of IP and export it and reuse it and make sure that it works. What I'm showing here is this is a snapshot out of the ISE 11 GUI, and what you can see is there are four areas here where I can kick off PlanAhead under the ISE mode. Now, I want to make it clear, when I demo it, I'm going to demo it in the PlanAhead, full PlanAhead mode. And so the tools are going to look different depending upon whether you start -- if I kick it off in here, this is the PinAhead, I'm going to be limited to what I can see and do in the PlanAhead portion. But I want you to -- it's specific to the task that you're asking it. If you're asking it, hey, I want to do some floor planning, it's going to bring you up in the floor planning mode. We already talked about this so I'm going to skip over that. Floor plan logic, you know, I can do the analysis of the design. You can do your timing analysis in there as well. So we'll show you that. And I had mentioned already I can only have one UCF. So most of these slides here that I've got right here are things that I felt that it was good to have them as a part of the slide deck for you, but I should be able to show you most of this in the demo portion. And this is simply what, if I kick off PinAhead out of the ISE GUI, what I see here, you know, here's my chip and different modules, the device view. So that's a BGA package -- or not a BGA, a quad flat package. So is same thing here. Floor planning view and floor planning post view, so RTL view. The other thing that does happen now in PlanAhead, I have the ability to suck in source by a module directory, so I don't have to say, hey, grab each of these individual VHDL or Verilog files, I can say grab this module or grab this directory. Now maybe you have just one directory with everything in it. I often see people with the module-level directories, so you can pull different modules pretty easily, and then you can export a list of sources to CSV so that you can know what you need to check in and check out of the library. You can do RTL analysis there, and we can look at it in a schematic view. And then this thing, we talked about it a little bit, but the idea is I can kick off synthesis, and I think -- yeah, this shows one synthesis level here, a couple different implementation runs and then a second level different type of synthesis with another implementation run. And just showing you how you set that up, and I'll show and show you that when I get to the demo. And then once you've got your results, you can analyze it and, you know, pretty much the same stuff we've talked about before. So let's kick off -- oh, and I guess this is -- I think most of you have seen this sort of thing in timing analyzing, so this is our way -- same way of doing the cross probing and looking at the constraints. And we'll be able to do all that. The other thing that has been added the in 11 is in here you can now add in ChipScope directly in PlanAhead. So you can either do it by instantiating the ChipScope icon ILAs or calling up the ChipScope wizard. And you can run through that. So that's part of what's been added in 11. So with that, it's time to go ahead and do a demo. Okay. It shows up here. So I have a design I've compiled or started to compile here. The thing you should see, and you could kind of see here while it's opening up that design, is when you open up PlanAhead for the first time, it remembers the previous projects that you've done, and it also has here a list of some tutorials designs, some simple designs that you can play around with. And so that'll allow you to get better acquainted with the tool and what you can do with it. So that's going to start up in a minute. One thing that's going on here is I ran a design, and it's a fairly significant design. It's a Vertex 5 SX 35, and give you a feel for it. I ran it on my laptop and it didn't quite finish so I closed out of it in an unfortunate manner before starting this presentation, so that's part of why it's taking its time opening up. It's not happy about how I closed out of it. >>: [inaudible] [laughter]. >> Don Matson: You've been there before. So here's what it looks like, and this is going to be a bit interesting to show you so maybe I'll just walk around here. So this is what it looks like when I pull it up. There's some Windows here, so this is my sources window. I grabbed a project that I had the HDL source for. So I can see that, I can open up one of those sources, I can evaluate it there. You can see there's a physical hierarchy tab, and I'll flip between that. Then down here, this will show properties. When I'm running, sometimes that'll show me some of the different options. And you can see here's the modules that are in this design. It has a CPU engine in there, a couple of USB cores, and just so you know, I've taken a look before, and I'll show you when I take a look down here at some of the runs that I've made. Obviously, in order to be a good tutorial, when you run it, it should meet timing because that's really where you spend some issues. And so there's a couple issues, and I'll show you that in just a minute. And I/O ports, types -- it's all pretty self-explanatory there. And I can flip here between the package and device window and -- yes, Ray? >>: What's that little memory counter in the lower right-hand corner that keeps ticking up and down? >> Don Matson: Good question. Let me see if I can get my mouse over here, because I've got a very -- I wonder, can I make this window -- this laptop look like the full screen. Let me see. I've got a small window up here that I can kind of run. Design runs. >>: It's running. >> Don Matson: It's running. Because I was running a design [laughter], and I didn't want it to run while I was -- so that's what's going on, and that's why the memory is going up and down. Now, where did my mouse go? Okay. Back over here. So this is a little bit awkward. So what I wanted to show you is -- let's just make this -- float that window down here. Oh, great. It's full screen on my laptop. But somehow I don't think you can see that. Let's drag that over to here. There. Oh, geez, that's not what I wanted. Sorry. That's not the window I wanted. I wanted -- so this is a par run. And you can see as I change the run, it'll show me over here I can look at the option set here and reports and everything. But the real thing I want to do -- I'm going to kill that window. These things aren't really designed very well for a 1024 by 768 display. So what you can see here is how long did it run and -- I guess I have to slide over just a little bit, but here's the number we're interested in, timing scores. So this one was -- and these two are the best two results. Let's just take a look at this design here. Yeah. So it's going to import it and take a look at it and running here. >>: So now it's loading all of the associated reports and everything with that run? >> Don Matson: Yes. And the -- basically the associated placement as well. So now I've got the placement in here. So now if I select CPU engine here and right click -- let's just highlight it in a color here. You can kind of -- should be able to see that. And then over here, statistics. So once again, we're being defeated by the small screen, but you can see there's 4,000 LUTs, I think, roughly. It's hard for me to see from this angle. But anyway, it's a major portion of the design. You can see down here, we now have our timing analysis. So I can look at the timing results, the I/O here, so -and we can see that -- so I can say, hey, show me a schematic on that. And then I can also view the path report and take a look at what's going on. So here's the schematic view. And, of course, we have to zoom in to an area. I'll just make it like that. On your screen here, I'll just make it pretty small. So here's my flip-flop. You can see it goes through some levels of logic on my screen. On a reasonable monitored you'll able to identify that it's a carry chain. That's what it's going through. And then we see -- we hit these big blocks here and lo and behold, those are 4DSP blocks, and there's no registers in there. So if I run any rules, it's going to tell me, gee, you really should use some registers in there. One of the ways you might be able to attack this problem is in synthesis, say do register retiming and it might be able to move one of those following registers somewhere into the middle here. Obviously the best way to attack this would be -- is if I could do something with this multiply. My guess is it's trying to do a 32-by-32-bit multiplication with those 18-by-18 multipliers, which gives you the four stages often. And if it were to throw a couple pipeline stages, it would run much faster. So anyway, I can see that real quickly in that schematic. It's not a question of how is this thing placed in the design, it's a question of the coding style or the implementation style of can I put a register there on that one. So that was one of the timing constraints. Let's go -- and that was in the CPU section. And since I've looked at this design before, I can tell you that there's going to be some failing areas in the USB section. So let's take a look at this one and let's just view the path report. So this is how you've seen it before. I think you guys have seen a report like this in timing analyzer, right? Has everybody seen that? So you know if I go in here and I highlight this, I can highlight the source or the destination, I can cross probe, and I can either cross probe into this schematic that I looked at here or I can cross probe into FPGA editor. And sometimes FPGA editor is a little nicer way to do that. And then if I scroll on down, you know, it gives me each of the areas that -- and where it's going. So I can see here I'm coming out of a FIFO, I'm going through a bunch of LUTs here, and then eventually to a register is what's going on. And, you know, there's not much I can do about that. The question is what's going on in this logic. And then it also gives me how much is logic delay versus everything else. And so the question in this one is going to be can I floor plan it so it gets put together closely to work. The other thing that's a little bit different here is this is highlighted so you can see if I click on it and I had internet connection here, it would launch a data sheet and try and give you where these parameters are found in the data sheet. I'll give you -- I mean, some of these things will be easy to find. This will be easy. A couple of these you may not find in the data sheet, but the idea is that we're trying to give you more information, how do you get more information. And then obviously these things, if I click on it, it'll go to it in either the FPGA editor or the package view. So that's that. Here's the device. And then I have some ability to turn on and off these different blocks. And I can say, gee, just compress everything. So it's a pretty nice way to maneuver around in here. Let's see. That's not I/Os. There. Get the I/O nets off. You know, so now I can see, and that's that path that I had just selected. So that's the overall view, and then if I come down here to my design runs, you know, you can see if I click this, I can set this up to run. And you can see I can manage multiple versions. And I guess one of the things that would be nice here is -- I should show you how I do that. And so run multiple strategies. So you can see I can select between either synthesis or implementation. I'm going to assume we want to do implementation. And I can either do it off of synthesis 1 or synthesis 2. You know, I could have some different floor plans saved as well to kick it off, and constraint files as well. And we don't want to do that. Say next. So now I have some ISE defaults. These are some of the different strategies that it has available for me to kick it off. Obviously I can create my own strategies as well after, and use those. Notice here, this is ISE 10 and ISE 11. So depending on what version of ISE I've been using it in, I might want to from here, from the PlanAhead, to kick it off in an older version. So I could do that as well. So I think -- and then I can add more. And, let's see -- and then this is where I can run how many jobs can I run. So, you know, I can only run two on here because I only have a dual core. I can also generate scripts so that now I might want to have scripts so that I could launch it at a later date however I want. And I thought somewhere -- oh, if I'm networked up, I can launch onto other machines. >>: Does that work under Windows? >> Don Matson: Yeah, this is Windows. >>: You mentioned, you were talking about the differences between, I think, Linux and Windows and spreading jobs around that I was wondered if ->> Don Matson: So on a Linux box I would be able to call other Linux machines. On a Windows box, I can only call the CPUs in the Windows box today. >>: So the network thing would not appear there. >> Don Matson: Right. But I can pass a list of hosts that I have ability to run on. >>: If they're running Windows. >> Don Matson: Yeah. >>: [inaudible]. >> Don Matson: Can I do what? >>: Go from Windows to a Linux faster? >> Don Matson: I don't think I can launch it from the Windows onto a Linux. I mean, you can do that -- I mean, there's other ways to do that, right? I mean, like with the laptop, I really don't want to launch it on here. I do have a server back at the office that I really want launch these things on. And so there's VNC, there's -there's lots of ways that people do do that, and I think that's what I see most people doing on that regards. I guess now is a good time for you to ask any questions, anything you want to see while I've got this up here. Yeah? >>: You said that with the new version that you were going to be defaulted to XST 10 with the v5 and back? >> Don Matson: Uh-huh. >>: What's the advantage of going with the new XST with the older hardware? Why would you default to the old XST with that hardware? >> Don Matson: Because people aren't real happy if I switch synthesis tools and your results are different, your internal names might be different. So by default, you want to run the old tool. We believe that you'll get better results in the long run with the XST 11 version. We just need to stay with -- we just need to allow you to take 11 and not see a huge change in results by default. So anyway, that's the demo, and I just wanted to leave you with a few places where you can get more information. We do have some up on the web under xilinx.com/planahead. There are some nice talks on different features, like PinAhead or ExploreAhead or doing the timing. As I said, even in ISE 10 if you open up PinAhead, there are some nice demos under it. In 11, obviously I showed you there were those three designs already there for you to start playing are around with and there are full tutorials on how to use them as well. And last thing, if you have questions, feel free to send me an email, give me a call. [applause] Thanks, guys.