Document 15999192

advertisement

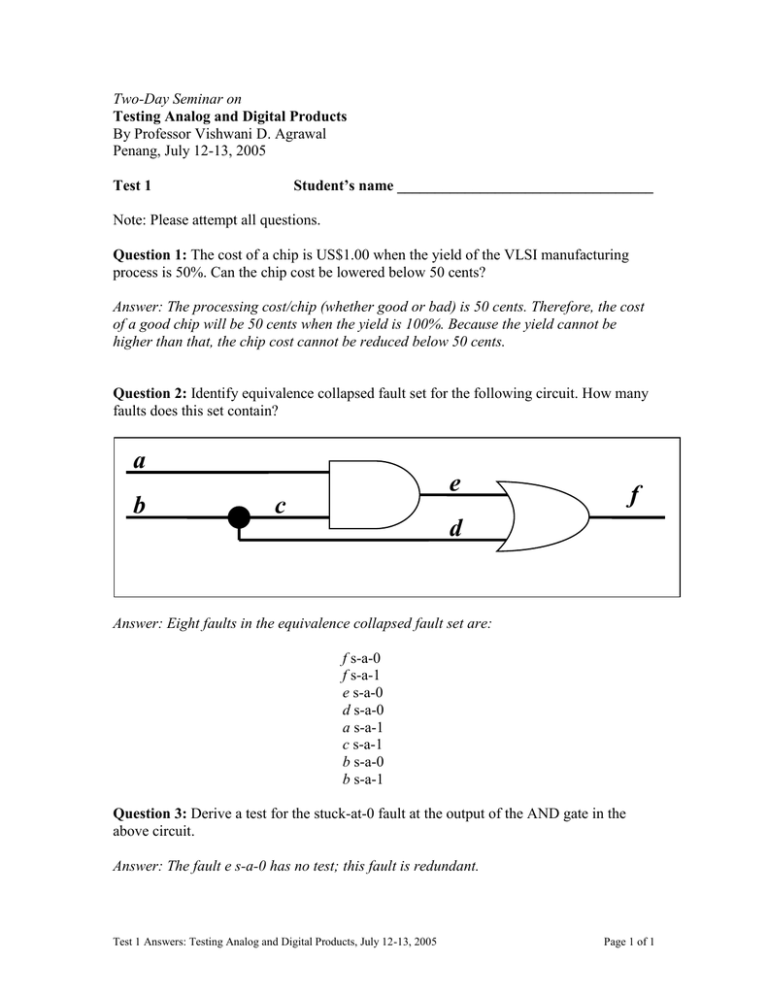

Two-Day Seminar on Testing Analog and Digital Products By Professor Vishwani D. Agrawal Penang, July 12-13, 2005 Student’s name __________________________________ Test 1 Note: Please attempt all questions. Question 1: The cost of a chip is US$1.00 when the yield of the VLSI manufacturing process is 50%. Can the chip cost be lowered below 50 cents? Answer: The processing cost/chip (whether good or bad) is 50 cents. Therefore, the cost of a good chip will be 50 cents when the yield is 100%. Because the yield cannot be higher than that, the chip cost cannot be reduced below 50 cents. Question 2: Identify equivalence collapsed fault set for the following circuit. How many faults does this set contain? a b e c f d Answer: Eight faults in the equivalence collapsed fault set are: f s-a-0 f s-a-1 e s-a-0 d s-a-0 a s-a-1 c s-a-1 b s-a-0 b s-a-1 Question 3: Derive a test for the stuck-at-0 fault at the output of the AND gate in the above circuit. Answer: The fault e s-a-0 has no test; this fault is redundant. Test 1 Answers: Testing Analog and Digital Products, July 12-13, 2005 Page 1 of 1