Energy Source Design ELEC 5270/6270 Spring 2015 Low-Power Design of Electronic Circuits

advertisement

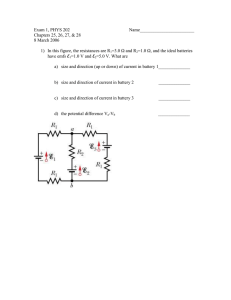

ELEC 5270/6270 Spring 2015 Low-Power Design of Electronic Circuits Energy Source Design Vishwani D. Agrawal James J. Danaher Professor Dept. of Electrical and Computer Engineering Auburn University, Auburn, AL 36849 vagrawal@eng.auburn.edu http://www.eng.auburn.edu/~vagrawal/COURSE/E6270_Spr15/course.html Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 1 Outline Energy source optimization methods Voltage and Clock Management Functional Management Voltage and Clock Management (DVFS) Background A typical system powered with battery Battery Simulation Model DC to DC converter Problem statement Case I : System is Performance bound Case II : A higher battery lifetime is required Case III : Battery weight or size is constrained Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 2 Energy Source Optimization Methods • Dynamic Voltage Management • Multi-Voltage design Voltage Management Timing Management • Dynamic Voltage and Frequency Scaling (DVFS) • Dynamic Frequency Management • Retiming Functional Management Copyright Agrawal, 2011 • Fetch Throttling • Dynamic Task Scheduling • Instruction Slowdown • Low Power solutions to common operations e.g. Low Power FSMs, Bus Encoding etc ELEC5270/6270 Spr 15, Lecture 7 3 Energy Source Optimization Methods Dynamic Voltage and Frequency Scaling (DVFS) Timing Management Voltage Management Parallel Architectures Functional Management Instruction Slowdown Method in Processors Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 4 Powering a System RB VB AHr (capacity) Copyright Agrawal, 2011 + _ IL VL ELEC5270/6270 Spr 15, Lecture 7 RL 5 Current and Load Power Current: IL = VB / (RB + RL) Power supplied to load: PL = IL2 RL = VB2 RL/ (RB + RL)2 PLmax = VB2 / (4RB), maximum power when RL = RB Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 6 Battery Lifetime, Power, Efficiency Ideal lifetime of battery = Ahr / IL = Ahr . (RB + RL) / VB Where AHr is battery capacity in ampere-hours Power supplied from battery: PB = IL2 (RB + RL) = VB2 / (RB + RL) Battery Efficiency = PL /PB = RL / (RB + RL) Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 7 Lifetime, Power and Efficiency PL = VB2/(4RB) (Maximum power transfer theorem) 1.0 Efficiency 8 0.8 6 0.6 4 0.4 Lifetime 2 0 0.2 Efficiency or Power Lifetime (x AHr.RB / VB) 10 0.0 0 Copyright Agrawal, 2011 1 2 3 4 RL/RB 5 ELEC5270/6270 Spr 15, Lecture 7 6 7 8 8 Power Subsystem of an Electronic System VDD 4.2 V to 3.5 V Lithium- ion Battery DC – DC Voltage Converter Decoupling Capacitor Electronic System GND See Lecture 12 on Power and Ground from ELEC 7770: http://www.eng.auburn.edu/~vagrawal/COURSE/E7770_Spr14/course.html Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 9 Some Characteristics Lithium-ion battery Open circuit voltage: 4.2V, unit cell 400mAHr, for efficiency ≥ 85%, current ≤ 1.2A Discharged battery voltage ≤ 3.0V DC-to-DC converter Supplies VDD to circuit, VDD ≤ 1V for nanometer technologies. VDD control for energy management. Decoupling capacitor(s) provide smoothing of time varying current of the circuit. Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 10 Battery Simulation Model Lithium-ion battery, unit cell capacity: N = 1 (400mAHr) Battery sizes, N = 2 (800mAHr), N = 3 (1.2AHr), etc. Ref: M. Chen and G. A. Rincón-Mora, “Accurate Electrical Battery Model Capable of Predicting Runtime and I-V Performance,” IEEE Transactions on Energy Conversion, vol. 21, no. 2, pp. 504–511, June 2006. Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 11 Model: Battery Lifetime Part SOC: State of charge = VSOC VSOC = 1 volt, for fully charged battery. CCapacity = 3600 ✕ AHr-rating ✕ f(Cycles) ✕ f(Temp) f(Cycles), f(Temp): effects of dropping capacity with number of recharges and temperature. Both are close to 1. Rself-Dscharge : A large leakage resistance. Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 12 Voltage-Current Characteristic Determined from experimental data. Open circuit voltage: V = −1.031e−35×SOC + 3.685 + 0.2156 × SOC −0.1178 × SOC2 + 0.3201 × SOC3 RSeries = 0.07446 + 0.1562 e – 24.37×SOC Other resistance and capacitance are also non-linear functions of SOC and represent short-term (S) and long-term (L) transient effects. Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 13 Lifetime from Battery Simulation 1008 sec Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 14 Battery Efficiency Consider: 1.2AHr battery IBatt = 3.6A Ideal Lifetime = 1.2AHr/3.6A = 1/3 hour (1200s) Actual lifetime from simulation = 1008s Efficiency = (Actual lifetime)/(Ideal lifetime) = 1008/1200 = 0.84 or 84% Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 15 DC-to-DC Buck (Step-Down) Converter s Components: Switch (FETs, VDMOS), diode, inductor, capacitor. Switch control: pulse width modulated (PWM) signal. Vs = D · Vg, D is duty cycle of PWM control signal. Source: R. W. Erickson, “DC to DC Power Converters, “ Wiley Encyclopedia of Electrical and Electronics Engineering Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 16 Asynchronous DC-to-DC Buck Converter L V C Vg Load + – Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 Vref 17 An Electronic System Example A 32-bit Ripple Carry Adder (RCA) 352 NAND gates (2 or 3 inputs) 1,472 transistors In order to realize a practical circuit and to generate sufficient current for the battery model, 200,000 copies of RCA were used. That makes it 352 x 200,000 ≈ 70 million gate circuit. Critical path: 32bit ripple-carry adder. Simulation model: 45nm bulk CMOS, predictive technology model (PTM), http://ptm.asu.edu/ Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 18 32-bit Ripple Carry Adder A0 B0 C0=0 A1 B1 C1 S0 C2 S1 A31 B31 C32 Copyright Agrawal, 2011 S31 ELEC5270/6270 Spr 15, Lecture 7 19 Critical Path Vectors 32 bits Vector 1 C A B S = = = = 00000000000000000000000000000000 11111111111111111111111111111111 00000000000000000000000000000000 11111111111111111111111111111111 Vector 2 C A B S = = = = 11111111111111111111111111111110 11111111111111111111111111111111 00000000000000000000000000000001 00000000000000000000000000000000 Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 20 HSPICE Simulation of 32-Bit RCA, VDD = 0.9V 100 random vectors including critical path vectors Average total current, Icircuit = 74.32μA, Leakage current = 1.108μA Critical path vectors 2ns Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 21 HSPICE Simulation of 32-Bit RCA, VDD = 0.3V 100 random vectors including critical path vectors Average total current, Icircuit = 0.2563μA, Leakage current = 0.092μA Critical path vectors 200ns Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 22 Finding Battery Current, IBatt Assume 32-bit ripple carry adder (RCA) with about 350 gates represents circuit activity for the entire system. Total current for 70 million gate circuit, Icircuit = (average current for RCA) x 200,000 DC-to-DC converter translates VDD to 4.2V battery voltage; assuming 100% conversion efficiency, IBatt = Icircuit x VDD/4.2 Example: HSPICE simulation of RCA: 100 random vectors VDD = 0.9V, vector period = 2ns, Average current for RCA = 74.32μA, IBatt = 3.18A Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 23 Case I: Performance System is Performance Bound Battery should be capable of supplying power (current) for required system performance. Battery should meet the lifetime (time between replacement or recharge) requirement. Power management to extend the lifetime of selected battery. Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 24 Four Step Design Step 1: Determine the lower bound on the operating voltage based on required performance. Step 2: Determine minimum battery size for efficiency ≥ 85% Step 3: Increase battery size over the minimum size to meet lifetime requirement. Step 4: Determine a lower performance mode with maximum lifetime for a given battery. Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 25 Step 1: Find Operating Voltage Consider a performance requirement of 200MHz clock, critical path delay ≤ 5ns. Circuit simulation gives, VDD = 0.6V and IBatt = 477mA. Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 26 Circuit Simulation: Determine Operating Voltage and Current for System Performance 477 mA 200 MHz Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 27 Step 2: Determine Minimum Battery Size • For required current 477 mA • Battery Efficiency ≥ 85 % Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 Select 400 mAHr Battery 28 Simulate Selected Battery A meaningful measure of the work done by the battery is its lifetime in terms of clock cycles. For each VDD in the range of valid operation, i.e., VDD = 0.1V to 1.0V, calculate lifetime using circuit delay and battery efficiency obtained from HSPICE simulation. Minimum energy operation maximizes the lifetime in clock cycles. Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 29 Simulation of 400mAHr Battery • Over entire operating voltage range of 0.1 V to 1 V • For both Ideal and Simulated battery 1.80E+12 DVFS range Ideal Battery Number of Cycles per Recharge 1.60E+12 Simulated Battery 1.40E+12 1.20E+12 Higher Circuit Speed, Lower Battery Efficiency 1.00E+12 8.00E+11 6.00E+11 Higher Battery Lifetime, Lower Circuit Speed 4.00E+11 2.00E+11 0.00E+00 0.00 0.20 0.40 0.60 0.80 1.00 1.20 VDD (Volts) 0.098 Copyright Agrawal, 2011 0.560 3.860 23.00 88.00 199.0 325.0 ELEC5270/6270 Spr 15, Lecture 7 446.0 557.0 657.0 (MHz) 30 Step 3: Battery Lifetime Requirement System needs higher battery lifetime Suppose battery lifetime for the system is to be at least 3 hours. For smallest battery, size N = 1 (400mAHr) IBatt = 477mA, Efficiency ≈ 98%, Lifetime = 0.98 x 0.4/0.477 = 0.82 hour For 3 hours lifetime, battery size N = 3/0.82 = 3.65 ≈ 4. We should use a 4 cell (1600mAHr) battery. Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 31 Meeting Lifetime Requirement 7.00E+12 Number of Cycles per Recharge 400 mAHr Battery 6.00E+12 1600 mAHr Battery 5.00E+12 2540x109 clock cycles 205 min ( > 3 Hrs) 4.00E+12 3.00E+12 619 x109 clock cycles, 50 minutes 2.00E+12 1.00E+12 0.00E+00 0.00 0.20 0.40 0.60 0.80 1.00 1.20 VDD (Volts) Copyright Agrawal, 2011 0.098 0.560 3.860ELEC5270/6270 23.00 88.00 199.0 325.0 446.0 Spr 15, Lecture 7 557.0 657.0 (MHz) 32 Step 4: Minimum Energy Operation 7.00E+12 Number of Cycles per Recharge 400 mAHr Battery 1600 mAHr Battery 6.00E+12 6630x109 clock cycles 5.00E+12 4.00E+12 1660x109 clock cycles 3.00E+12 2.00E+12 1.00E+12 0.00E+00 0.00 0.20 0.40 0.60 0.80 1.00 1.20 VDD (Volts) Copyright Agrawal, 2011 0.098 0.560 3.860ELEC5270/6270 23.00 88.00 199.0 325.0 446.0 557.0 657.0 Spr 15, Lecture 7 (MHz)33 Summarizing Power Management Battery size VDD = 0.6V, 200MHz Lifetime VDD = 0.3V, 3.86MHz N mAHr 1 400 98 3 619 100+ 414.5 1660 4 1600 100+ 12.3 2540 100+ 1364 6630 x103 seconds X10 9 cycles Effici. % Lifetime Effici. % x103 seconds X10 9 cycles > two-times 1. Battery size should match the current need and satisfy the lifetime requirement of the system: (a) Undersize battery has poor efficiency. (b) Oversize battery is bulky and expensive. 2 Minimum energy mode can significantly increase battery lifetime. Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 34 Battery Size or Weight is Constrained 1. Some real life applications call for a fixed size (or weight) of a battery, e.g., bio-implantable devices, hearing aid. 2 Performance requirements are secondary and the primary goal is to maximize the lifetime (or number of cycles before next recharge). 3 Example: A CR2032(CR) Lithium-ion battery Nominal Voltage: 3V Capacity: 225mAHr Nominal Current: 0.3 mA Maximum Current: 3 mA Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 35 Number of Cycles per Recharge 9.00E+11 Ideal Battery 8.00E+11 Simulated Battery 7.00E+11 540x109 clock cycles 6.00E+11 5.00E+11 4.00E+11 3.00E+11 2.00E+11 1.00E+11 0.00E+00 0.00 0.20 0.40 0.60 0.80 1.00 1.20 VDD (Volts) 0.098 Copyright Agrawal, 2011 0.560 3.860 23.00 88.00 199.0 325.0 446.0 ELEC5270/6270 Spr 15, Lecture 7 557.0 657.0 (MHz) 36 References 1. 2. 3. 4. 5. M. Pedram and Q. Wu, “Design Considerations for Battery-Powered Electronics,” Proc. 36th Design Automation Conference, June 1999, pp. 861– 866. L. Benini, G. Castelli, A. Macii, E. Macii, M. Poncino, and R. Scarsi, “A Discrete-Time Battery Model for High-Level Power Estimation,” Proc. Conference on Design, Automation and Test in Europe, Mar. 2000, pp. 35 – 41. M. Chen and G. A. Rincón-Mora, “Accurate Electrical Battery Model Capable of Predicting Runtime and I-V Performance,” IEEE Transactions on Energy Conversion, vol. 21, no. 2, pp. 504 – 511, June 2006. Simulation model: 45nm bulk CMOS, predictive technology model (PTM), http://ptm.asu.edu/ Simulator: Synopsys HSPICE, www.synopsys.com/Tools/Verification/AMSVerification/CircuitSimulation /HSPICE/Documents/hspice ds.pdf Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 37 References (Cont.) 6. 7. 8. 9. 10. M. Kulkarni and V. D. Agrawal, “Matching Power Source to Electronic System: A Tutorial on Battery Simulation”, Proc. VLSI Design and Test Symposium, July 2010. M. Kulkarni and V. D. Agrawal, “Energy Source Lifetime Optimization for a Digital System through Power Management,” Proc. Proc. IEEE International Conf. Industrial Technology and 43rd IEEE Southeastern Symp. System Theory, March 2011. M. Kulkarni, S. Sheth and V. D. Agrawal, “Architectural Power Management for High Leakage Technologies,” Proc. Proc. IEEE International Conf. Industrial Technology and 43rd IEEE Southeastern Symp. System Theory, March 2011. M. Kulkarni, “Energy Source Lifetime Optimization for a Digital System through Power Management,” Master’s Thesis, ECE Dept., Auburn University, December 2010. K. Sheth, “A Hardware-Software Processor Architecture using Pipeline Stalls for Leakage Power Management,” Master’s Thesis, ECE Dept., Auburn University, December 2008. Copyright Agrawal, 2011 ELEC5270/6270 Spr 15, Lecture 7 38