Okechukwu Akpa ELEC 7770-001, Spring 2008 Class Project

advertisement

Okechukwu Akpa

ELEC 7770-001, Spring 2008

Class Project

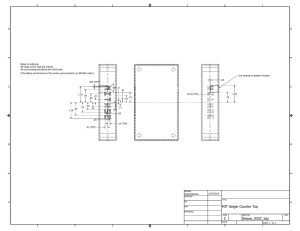

The project for Advance VLSI centered around the test and verification of a 32-bit multiplier circuit.

The schematic of a 32-bit multiplier appears below.

Multiplicand

CK

32

START

32

Add if LSB=1

32-bit Adder

OF

Control:

Do

32 times

Test LSB

32

64-bit product register

00000 . . . 00000 32-bit multiplier

shift

right

DONE

Initialized product register

Below is the Verilog behavioral model for an unsigned 32-bit multiplier used for this project.

ModelSim was used to create this circuit.

module unsingned_mult(start, clk, done, of, product, multiplier,

multiplicand);

output done, of;

output [63:0] product;

input [31:0] multiplier, multiplicand;

input clk, start;

wire done, of;

wire [31:0] multiplier, multiplicand;

reg [31:0] unsingned_mult;

reg [63:0] product;

reg [5:0] control;

wire lsb = product[0];

wire [31:0] sum;

assign done = control[5];

wire shiftreg = ~control[5];

wire [31:0] lsbunsingned_mult = { 32{ lsb }} & unsingned_mult;

adder32 adder32i(.of( of ), .sum( sum ), .m1( product[63:32] ),

.m2( lsbunsingned_mult ));

always @(posedge clk)

if (start)

unsingned_mult <= multiplier;

always @(posedge clk)

if (start)

control <= 6'b000000;

else

control <= control + shiftreg;

always @(posedge clk)

if (start)

product <= {32'b0, multiplicand};

else if (shiftreg)

product <= {of, sum, product[31:1]};

endmodule

module adder32(of, sum, m1, m2);

Verification

Some test cases were used to verify the operation of the multiplier which are summarized in the table

below.

Clk

Start

1

1

1

1

1

1

1

0

1

0

1

1

Multiplier (Hex) Multiplicand

(Hex)

1B5679E

2345A72

1B5679E

2345A72

1B5679E

762A267

1B5679E

762A267

4B5C79E

232A2B7

4B5C79E

232A2B7

Product

0

3C442D14DB05C

0

C9E5C780AAC92

0

A5A0E9F1FADF2

Done

0

1

0

1

0

1

This post synthesis verification proves the behavioral model works. However, it would take

considerable time to input all test cases to completely verify the design. To prove how reliable the

circuit design is Mentor Graphics will be used to optimize and provide additional testing. This

multiplier was synthesized in Leonardo using TSMC0.35 micron technology statistics from the netlist

appear below.

Gate Composition

*******************************************************

Cell: unsingned_mult

View: INTERFACE

Library: work

*******************************************************

Cell

Library

ao32

aoi21

aoi32

dff

inv01

inv02

mux21_ni

nand02

nand03

nand04

nor02ii

nor03_2x

oai21

oai32

or02

or03

or04

xnor2

xor2

Number

Number

Number

Number

References

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

of

of

of

of

1

3

30

116

31

16

98

36

1

3

1

1

7

31

1

2

1

1

61

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

ports :

nets :

instances :

references to this view :

Total accumulated area :

Number of gates :

Number of accumulated instances :

Total Area

2

1

2

5

1

1

2

1

1

1

1

1

1

2

1

2

2

2

2

2

4

52

556

24

12

177

36

1

4

1

1

9

54

1

3

2

2

129

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

132

541

441

0

1070

441

Clock Frequency

Clock Frequency Report

Clock

: Frequency

------------------------------------

clk

: 73.9 MHz

Critical Path and Delay

Critical Path Report

Critical path #1, (unconstrained path)

NAME

GATE

ARRIVAL

LOAD

--------------------------------------------------------------------------------clock information not specified

delay thru clock network

0.00 (ideal)

reg_product(0)_rep_10/Q

ix2959/Y

ix1015/Y

ix2968/Y

ix131/Y

ix2981/Y

ix147/Y

ix2994/Y

ix163/Y

ix3007/Y

ix179/Y

ix3020/Y

ix195/Y

ix3033/Y

ix211/Y

ix3046/Y

ix227/Y

ix3059/Y

ix243/Y

ix3072/Y

ix259/Y

ix3085/Y

ix275/Y

ix3098/Y

ix291/Y

ix3111/Y

ix307/Y

ix3124/Y

ix323/Y

ix3137/Y

ix339/Y

ix3150/Y

ix355/Y

ix3163/Y

ix371/Y

ix3176/Y

ix387/Y

ix3189/Y

ix403/Y

ix3202/Y

ix419/Y

dff

nand02

xor2

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

0.00

0.22

0.53

0.32

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.55

0.78

1.30

1.62

1.72

2.00

2.10

2.37

2.47

2.75

2.84

3.12

3.22

3.49

3.59

3.87

3.97

4.24

4.34

4.62

4.71

4.99

5.09

5.36

5.46

5.74

5.83

6.11

6.21

6.48

6.58

6.86

6.96

7.23

7.33

7.61

7.70

7.98

8.08

8.35

8.45

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

up

dn

0.07

0.02

0.04

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

ix3215/Y

ix435/Y

ix3228/Y

ix451/Y

ix3241/Y

ix467/Y

ix3254/Y

ix483/Y

ix3267/Y

ix499/Y

ix3280/Y

ix515/Y

ix3293/Y

ix531/Y

ix3306/Y

ix547/Y

ix3319/Y

ix563/Y

ix3332/Y

ix579/Y

ix3345/Y

ix595/Y

ix1505/Y

ix2839/Y

reg_product(63)/D

data arrival time

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

aoi32

inv01

mux21_ni

ao32

dff

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.10

0.28

0.47

0.00

Test vectors were generated in the sequential mode

CMD> report statistics

Total number of sequential instances

=

*****Circuit Statistics*****

# of primary inputs = 66

# of primary outputs = 66

# of library design cells = 441

# of library leaf cells = 441

# of combinational library primitives = 460

# of sequential library primitives = 116

# of simulation primitives = 1673

The vectors yielded various fault statistics

*****Fault List Statistics*****

Fault Class

Uncollapsed

Full (FU)

3660

Det_simulation (DS)

3086

Hyp_testable (HT)

136

Posdet_untestable (PU)

4

Posdet_testable (PT)

3

Unused (UU)

164

Atpg_untestable (AU)

232

Unobserved (UO)

35

Fault coverage

86.27%

Collapsed

2646

2095

121

4

3

164

232

27

81.59%

116

8.73 up

8.83 dn

9.10 up

9.20 dn

9.48 up

9.57 dn

9.85 up

9.95 dn

10.22 up

10.32 dn

10.60 up

10.69 dn

10.97 up

11.07 dn

11.34 up

11.44 dn

11.72 up

11.82 dn

12.09 up

12.19 dn

12.47 up

12.57 dn

12.85 dn

13.32 dn

13.32 dn

13.32

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.03

0.01

0.01

0.02

0.00

Test coverage

ATPG effectiveness

90.32%

97.14%

86.99%

96.64%

*****Test Patterns Statistics*****

Total Test Cycles Generated = 511

Total Test Cycles Simulated = 1567

Machine Name

User Name

User CPU Time

System CPU Time

Memory Used

:

:

:

:

:

saratoga

oza0001

73.1 seconds

2.5 seconds

68.602 MB

The faults were classified as follows:

Full (FU) stands for the total number of faults in the circuit

Det_Simulation (DS) are faults detected by the simulation

Hyp_testable (HT) hypertrophic faults

Posdet_untestable (PU) proven ATPG_untestable and hard

Posdet_testable (PT) potentially detectable posdet faults

Unused faults (UU) occur on nets that are not connected in the circuit

Atpg_untestable (AU) occur due to the violation of design rules

Unobserved faults (UO) are unobserved and undetected

A scan was inserted and combinational test vectors were generated.

A full scan design was implemented using the DFTadvisor tool. The area statistics are shown below.

*******************************************************

Cell: unsingned_mult

View: INTERFACE

Library: work

*******************************************************

Cell

ao32

aoi21

aoi32

dff

inv01

inv02

mux21_ni

Library

References

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

1

3

30

116

31

18

98

x

x

x

x

x

x

x

Total Area

2

1

2

5

1

1

2

2

4

52

556

24

14

177

gates

gates

gates

gates

gates

gates

gates

nand02

nand03

nand04

nor02_2x

nor03_2x

oai21

oai32

or02

or03

or04

xnor2

xor2

Number

Number

Number

Number

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

tsmc035_typ

of

of

of

of

36

2

3

1

1

7

31

1

1

1

31

31

x

x

x

x

x

x

x

x

x

x

x

x

ports :

nets :

instances :

references to this view :

Total accumulated area :

Number of gates :

Number of accumulated instances :

1

1

1

1

1

1

2

1

2

2

2

2

36

2

4

1

1

9

54

1

2

2

59

66

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

gates

132

542

443

0

1065

443

The fault classification for fastscan was different from that of the flextest. There are fewer faults

which means this implementation is better, however a new class of fault did occur which was:

Det_Implication (DI) which indicate faults that are detected by implication.

These statistics appear below.

CMD> report statistics

Statistics report

------------------------------------------#faults

#faults

fault class

(coll.)

(total)

----------------------------------FU (full)

3016

4128

----------------------------------DS (det_simulation)

2231

3243

DI (det_implication)

719

819

UU (unused)

66

66

----------------------------------test_coverage

100.00%

100.00%

fault_coverage

97.81%

98.40%

atpg_effectiveness

100.00%

100.00%

------------------------------------------#test_patterns

42

#simulated_patterns

64

CPU_time (secs)

4.7

-------------------------------------------

Area in number of gates went from 1070 to 1065 which is an overhead of 0.47%.

As there is a five gate difference in the two designs, the estimated gate overhead is nominal. What is

gained is that the untested faults are eliminated inserting the scan.