A Tutorial on Emerging Nanotechnology Devices Tezaswi Raja, Vishwani D. Agrawal,

advertisement

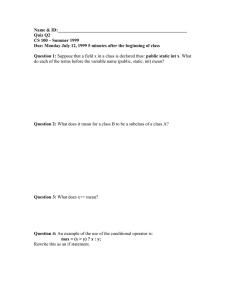

A Tutorial on Emerging Nanotechnology Devices Tezaswi Raja, Rutgers University Vishwani D. Agrawal, Auburn University Michael Bushnell, Rutgers University 7 Jan 2004 17th Int'l Conference on VLSI Design 1 Outline Introduction Nano Scale MOSFET Carbon Nanotube FETs Solid State Quantum Devices Molecular Electronics Challenges and the Current State of the Art Conclusion 7 Jan 2004 17th Int'l Conference on VLSI Design 2 Introduction Feature size nearing the physical limits Fabrication process approaching limits Power consumption – a concern Quantum effects need to be accounted for Solution? Nanotechnology We present an overview of new devices and outline some open problems. 7 Jan 2004 17th Int'l Conference on VLSI Design 3 7 Jan 2004 17th Int'l Conference on VLSI Design 4 7 Jan 2004 17th Int'l Conference on VLSI Design 5 What is Nanotechnology? Switching devices of nanometer (below 100nm, typically 10nm) dimensions define nanotechnology. Emerging Nanotechnology Solutions Quantum Dots Molecular SETs CNFETs RTD Nano CMOS CNT arrays Molecular orientations as Bits DNA self assembly Molecules in Solution 7 Jan 2004 Emerging Nanotechnology Drivers DNA strands as Bits Self assembled CNT using DNA 17th Int'l Conference on VLSI Design Logic (Our Focus) Memory Fabrication 6 Computing Devices Solid State Devices CMOS Devices Nano CMOS CNFET Quantum Molecular Devices Quantum Devices Quantum Dot Electro- RTD Photoactive mechanical 7 Jan 2004 17th Int'l Conference on VLSI Design SET Electrochemical 7 Photo Courtesy: Fujitsu Labs Nano-Scale MOSFET Metal Oxide Semiconductor Field Effect Transistor Three terminal device Source, gate and drain Vg controls the conduction from source to drain Half thickness of the gate is called “Feature size λ” Current feature sizes in production – 90nm (Intel Pentium 5) Demonstrated feature sizes up to 20nm (IBM). 7 Jan 2004 17th Int'l Conference on VLSI Design 8 Challenges Difficulties High electric fields Power supply vs. threshold voltage Heat dissipation Interconnect delays Vanishing bulk properties Shrinkage of gate oxide layer Too many problems to continue miniaturization as physical limits approach Proposed solutions are short term Open Problems Improve lithographic precision (eBeam) Explore new materials (GaAs, SiGe, etc.) As a long term goal explore new devices 7 Jan 2004 17th Int'l Conference on VLSI Design 9 Outline Introduction Nano scale MOSFET Carbon Nanotube FETs Solid State Quantum Devices Molecular Electronics Challenges and current state of the art Conclusions 7 Jan 2004 17th Int'l Conference on VLSI Design 10 Carbon Nanotubes Carbon nanotubes are long meshed wires of carbon Longest tubes up to 1mm long and few nanometers thick made by IBM. Property Carbon Nanotubes Comparatively Size 0.6-1.8 nm in diameter Si wires at least 50nm thick Strength 45 Billion Pascals Steel alloys have 2 Billion P. Resilience Bent and straightened without damage Metals fracture when bent and restraightened Conductivity Estimated at 109 A/cm2 Cu wires burn at 106 A/cm2 Cost $2500/gram by BuckyUSA in Houston Gold is $15/gram 7 Jan 2004 17th Int'l Conference on VLSI Design 11 Electrical Properties of CNT Carbon nanotubes can be metallic or semiconductor depending on their chirality. C = n a1 + m a2 Chiral Vector C is defined as the vector from one open end of the tube to the other after it is rolled. If (n-m) is divisible by 3, the tube is metallic If (n-m) is not divisible by 3, the tube is semiconducting. 7 Jan 2004 17th Int'l Conference on VLSI Design 12 Courtesy: IBM Carbon Nanotube FET CNT can be used as the conducting channel of a MOSFET. These new devices are very similar to the CMOS FETs. All CNFETs are pFETs by nature. nFETs can be made through Annealing Doping Very low current and power consumption Although tubes are 3nm thick CNFETs are still the size of the contacts, about 20nm. 7 Jan 2004 17th Int'l Conference on VLSI Design 13 Courtesy: IBM Courtesy: IBM CNT Fabrication Controlling the conductivity of the tubes (Constructive Destruction) All tubes laid on the contact Metallic tubes are destroyed Controlling diameter of the tube Start with MWNTs. Destroy the outer layers one by one to reduce diameter. Placing exactly at the required location. Yet to be demonstrated convincingly to exploit complete advantage using Lithography. Using DNA for self assembly Demonstrated by Techion-Israel very recently (Nov’2003). 7 Jan 2004 17th Int'l Conference on VLSI Design 14 Summary and Challenges CNTs are flexible tubes that can be made conducting or semiconducting. Nano-scale, strong and flexible. Challenges: Multilevel interconnects not available Chip density still limited to the density of contacts. Tube density not entirely exploited Fabrication is still a stochastic process Alternatives to gold contacts need to be found. Open Problems and Initiatives: Fabrication using DNA for self assembly (Technion-Israel; Science, Nov 2003) Memory array of nanotubes using junctions as bit storages (Lieber at Harvard) Using nanotube arrays to make computing elements (DeHon at Caltech) Fabricate FPGAs using CNFETs and STM (Avouris at IBM) 7 Jan 2004 17th Int'l Conference on VLSI Design 15 Outline Introduction Nano scale MOSFET Carbon Nanotube FETs Solid State Quantum Devices Molecular Electronics Challenges and current state of the art Conclusions 7 Jan 2004 17th Int'l Conference on VLSI Design 16 Allowed Energy Levels Barrier Occupied Energy Levels Barrier Energy Solid State Quantum Devices Occupied Energy Levels Distance Source Island Drain Quantum effects used to build devices. Electrons confined on an island Island can be created by using different band-gap devices in succession Island has certain allowed energy levels If allowed energy levels are filled then the device is in conduction Types of devices Resonant Tunneling Diode (RTD) Single Electron Transistor (SET) Quantum Dot (QD) Blocking conduction due to unavailable energy levels is called coulomb blockade 7 Jan 2004 17th Int'l Conference on VLSI Design 17 Conduction Occupied Conduction Band Allowed Energy Levels Occupied Conduction Band Energy Energy Principle of Conduction Conduction Occupied Conduction Band Allowed Energy Levels Gate bias Source Island Drain Source Island Drain Conduction can occur by Increasing source to drain voltage Applying Gate Bias 7 Jan 2004 17th Int'l Conference on VLSI Design 18 Single Electron Transistors (SET) Source Gate Cg Island Drain Conductance changes in spurts as energy levels are discrete To go from conducting to non-conducting stage, it requires voltage sufficient for one electron to cross This is achieved by applying gate bias enough for just one electron charge -- hence the name SET Bias required for conduction is coulomb gap voltage Same device can act as pFET or nFET based on the barrier strength Applications: Extra sensitive charge meters CMOS style conducting devices 7 Jan 2004 17th Int'l Conference on VLSI Design 19 Quantum Dots and Arrays Dot occupied by Electron Dot unoccupied Inter-dot Barriers Outer Barriers Courtesy: vortex.tn.tudelft.nl/ grkouwen/kouwen.html 3-dimensional island tunneling barrier State determined by presence of electron and not by conduction. Quantum cell array (QCA) is a lattice of these cells with 2 electrons confined. Occupied electrons are furthest from each other due to repulsive forces. 7 Jan 2004 17th Int'l Conference on VLSI Design 20 Quantum Cellular Automata 1 “1” 1 QCA Wire “0” Stable 1 0 Unstable QCA Inverter 2 states – “1” and “0”. Electrostatic interaction of nearby cells makes the bits flip. Input to the cell is by manipulating the Inter-dot barriers. Logic gates can be constructed. 7 Jan 2004 17th Int'l Conference on VLSI Design 21 Summary and Challenges Summary Electrons confined on an island. Allowed energy levels are discrete and allow the device to fluctuate between conducting and non-conducting states. SET – 2 dimensional device with gate bias control. QD – device with electron presence as state. QCA – Arrays of QDs used for computing. Challenges Background charge may offset states (noise sensitivity) Sensitivity of tunneling current to barrier width (lithographic accuracy) Sensitivity to barrier widths Cryogenic operation Open Problems Lithographic methods with guaranteed accuracy Self assembly of systems Background charge elimination Synthesis and verification techniques needed Testing of these devices as stuck-at models may be inadequate. 7 Jan 2004 17th Int'l Conference on VLSI Design 22 Outline Introduction Nano scale MOSFET Carbon Nanotube FETs Solid State Quantum Devices Molecular Electronics Challenges and current state of the art Conclusions 7 Jan 2004 17th Int'l Conference on VLSI Design 23 Molecular Electronics Incentives Molecules are nano-scale Self assembly is achievable Very low-power operation Highly uniform devices Quantum Effect Devices Building quantum wells using molecules Electromechanical Devices Using mechanical switching of atoms or molecules Electrochemical Devices Chemical interactions to change shape or orientation Photoactive Devices Light frequency changes shape and orientation. 7 Jan 2004 17th Int'l Conference on VLSI Design 24 Molecular Electronics Thiol Acetylene linkage Benzene ring Mechanical synthesis Molecules aligned using a scanning tunneling microscope (STM) Fabrication done molecule by molecule using STM Chemical synthesis Molecules aligned in place by chemical interactions Self assembly Parallel fabrication 7 Jan 2004 17th Int'l Conference on VLSI Design 25 An Atomic Relay 7 Jan 2004 17th Int'l Conference on VLSI Design 26 Summary and Challenges Summary Parallel self assembly Very regular structures Many alternatives proposed but inherent problems Very low energy operation Challenges Signal restoration and gain Finding non-interacting chemicals Chemical reactions stochastic with by-products Slow operating speeds Open Problems Self assembling of devices Increased speed of operation Guaranteed switching of molecules (HP- UCLA devices) Simulation models and CAD 7 Jan 2004 17th Int'l Conference on VLSI Design 27 Conclusion CMOS technology is approaching saturation – problems in the nanometer range Several new possibilities emerging Carbon nanotubes (CNT) Single-electron transistor (SET) and quantum dots (QD) Molecular computing devices 7 Jan 2004 17th Int'l Conference on VLSI Design 28