These slides incorporate figures from Digital Design

advertisement

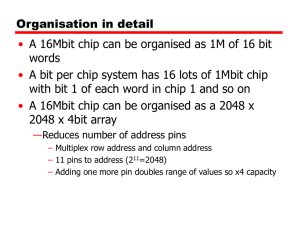

These slides incorporate figures from Digital Design Principles and Practices, third edition, by John F. Wakerly, Copyright 2000, and are used by permission. NO permission is given to re-use or publish these figures, in either original or modified form, in printed, electronic or any other format. Slide Set 13 Random access memory Read-Only Memories • Program storage – Boot ROM for personal computers – Complete application storage for embedded systems. Two-dimensional decoding Modern chips use transistors to pull down lines: Larger example, 32Kx8 ROM EEPROM: Typical commercial EEPROMs Microprocessor EPROM application ROM control and I/O signals ROM timing Read/Write Memories • a.k.a. “RAM” (Random Access Memory) • Volatility – Most RAMs lose their memory when power is removed – NVRAM = RAM + battery – Or use EEPROM • SRAM (Static RAM) – Memory behaves like latches or flip-flops • DRAM (Dynamic Memory) – Memory lasts only for a few milliseconds – Must “refresh” locations by reading or writing SRAM SRAM operation • Individual bits are D latches, not edge-triggered D flip-flops. – Fewer transistors per cell. • Implications for write operations: – Address must be stable before writing cell. – Data must be stable before ending a write. SRAM array SRAM control lines • Chip select • Output enable • Write enable SRAM read timing • Similar to ROM read timing SRAM write timing • Address must be stable before and after write-enable is asserted. • Data is latched on trailing edge of (WE & CS). Bidirectional data in and out pins • Use the same data pins for reads and writes – Especially common on wide devices – Makes sense when used with microprocessor buses (also bidirectional) memory read (assuming CS_L is always asserted): load MAR from bus appears load MAR from bus disappears OE_L asserted load MBR from memory appears load MBR disappears OE_L disappears MAR has memory address MBR has data memory write (assuming CS_L is always asserted): load MAR from bus appears load MBR from bus appears enable MBR to memory appears load MAR from BUS disappears WE_L appears load MBR disappears WE_L disappears MBR has data MAR has memory address SRAM devices • Similar to ROM packages 28-pin DIPs 32-pin DIPs Synchronous SRAMs • Use latch-type SRAM cells internally • Put registers in front of address and control (and maybe data) for easier interfacing with synchronous systems at high speeds • E.g., Pentium cache RAMs DRAM (Dynamic RAMs) • SRAMs typically use six transistors per bit of storage. • DRAMs use only one transistor per bit: • 1/0 = capacitor charged/discharged DRAM read operations – Precharge bit line to VDD/2. – Take the word line HIGH. – Detect whether current flows into or out of the cell. – Note: cell contents are destroyed by the read! – Must write the bit value back after reading. DRAM write operations – Take the word line HIGH. – Set the bit line LOW or HIGH to store 0 or 1. – Take the word line LOW. – Note: The stored charge for a 1 will eventually leak off. DRAM charge leakage • Typical devices require each cell to be refreshed once every 4 to 64 mS. • During “suspended” operation, notebook computers use power mainly for DRAM refresh. DRAM-chip internal organization 64K x 1 DRAM multiplex 16-bit address as 8-bit row selector and 8-bit column selector RAS/CAS operation • Row Address Strobe, Column Address Strobe – n address bits are provided in two steps using n/2 pins, referenced to the falling edges of RAS_L and CAS_L – Traditional method of DRAM operation for 20 years. – Now being supplanted by synchronous, clocked interfaces in SDRAM (synchronous DRAM). DRAM read timing DRAM refresh timing DRAM write timing