Hardware Accelerated Market Order Packet Generation Ankur Gupta, Dhananjay Palshikar , Mithila

advertisement

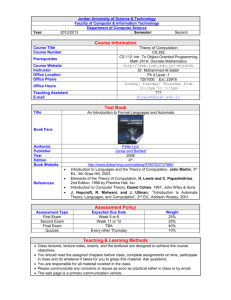

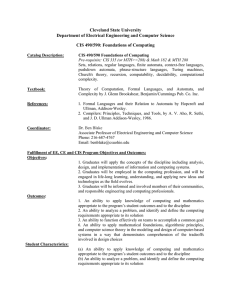

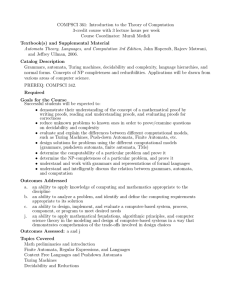

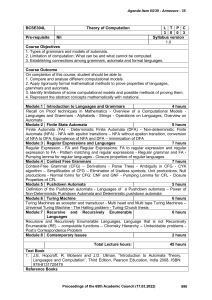

Hardware Accelerated Market Order Packet Generation Ankur Gupta, Dhananjay Palshikar , Mithila Paryekar , Sushant Bhardwaj and Yasser Mohammed Aim of the Project • The designed system aims at accelerating the release of packets on the network. • Optimization is achieved in terms of reducing the latency, decreasing the data uploaded on the Avalon bus which will eventually lead to power optimization. • A software application running on a soft-processor would change the transaction data going over the network in runtime. • Our implementation accelerates the sending of data to the network while receiving of data is handled in software. System Architecture Custom DM9000 Basic Automata: – Avalon Peripheral – UDP Packetization Component – DM9000A initialization component – DM9000A Communication Iterator: – Loops over basic automata – Accomplishes Basic read/write functionality UDP-Payload Format Automata of Custom Hardware Timing Diagram: Write Cycle Timing Diagram: Read Cycle Automata of Iterator Result • Original (software) transmission rate = 18.50 Kbps • Improved (hardware) transmission rate = 687.16 Kbps • X 36 times faster!