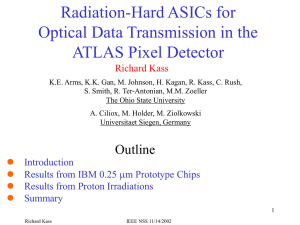

Rad-Hard ASICs for Optical Data Transmission in the ATLAS Pixel Detector

advertisement

Radiation-Hard ASICs for Optical Data Transmission in the ATLAS Pixel Detector Richard Kass K.E. Arms, K.K. Gan, M. Johnson, H. Kagan, R. Kass, C. Rush, A. Rahimi, S. Smith, R. Ter-Antonian, M.M. Zoeller The Ohio State University A. Ciliox, M. Holder, S. Nderitu, M. Ziolkowski Universitaet Siegen, Germany Outline l l l l Introduction Results from IBM 0.25 mm Prototype Chips Results from Proton Irradiations Summary 1 LECC03, 9/30/2003 Richard Kass/OSU ATLAS Pixel Detector 2 disks/end 2 layers in barrel l l l l Inner most charged particle tracking detector Pixel size: 50 mm x 400 mm ~ 100 million channels Dosage after 10 years: middle barrel layer: optical link: 50 Mrad or 1015 1-MeV neq/cm2 30 Mrad 2 LECC03, 9/30/2003 Richard Kass/OSU ATLAS Pixel Opto-link VCSEL: Vertical Cavity Surface Emitting Laser diode VDC: VCSEL Driver Circuit PIN: PiN diode DORIC: Digital Optical Receiver Integrated Circuit Opto-board: this board holds the VDCs, DORICs, PINs, VCSELS use BeO as substrate for heat management 3 LECC03, 9/30/2003 Richard Kass/OSU VCSEL Driver Circuit Specs lConvert LVDS input signal into single-ended signal appropriate to drive the VCSEL diode lOutput (bright) current: 0 to 20 mA, controlled by external voltage lStanding (dim) current: ~ 1 mA to improve switching speed lRise & fall times: 1 ns nominal (80 MHz signals) lDuty cycle: (50 +/- 4)% l“On” voltage of VCSEL: up to 2.3 V at 20 mA for 2.5 V supply l Constant current consumption! lCurrent design uses TRUELIGHT “high power oxide” VCSELs 4 LECC03, 9/30/2003 Richard Kass/OSU Digital Optical Receiver IC Specs Decode Bi-Phase Mark encoded (BPM) clock and command signals from PIN diode l l Input signal: 40-1100 mA 40 MHz clock l Extract: 40 MHz clock command l Duty cycle: (50 +/- 4)% l Total timing error: < 1 ns l Common Cathode PIN array l Bit Error Rate (BER): < 10-11 at end of life l BPM Training period: ~1 ms of 20 MHz clock (BPM with no data) Input transitions ] leading edges Internal delays LECC03, 9/30/2003 ] trailing edges Richard Kass/OSU 5 Status of VDC and DORIC VDC and DORIC produced using IBM 0.25mm CMOS process Migrated ATLAS SCT’s VDC & DORIC design in AMS 0.8mm Bipolar to DMILL DMILL (0.8mm CMOS) process met e-specs but was not rad hard enough VDC-I5e and DORIC-I5e: our fifth IBM submission Use CADENCE program 5 layers, enclosed layout transistors and guard rings 4 channels per chip (VDC: 1.4mm4mm DORIC: 2.3mm4mm) engineering run, produced enough chips for production Received chips in June 2003 Electrical measurements performed on these chips: detailed measurements of many parameters: rise/fall time, duty cycle, bright/dim current… VDC-I5e and DORIC-I5e are acceptable for use in pixel detector Need to certify that these chips are radiation hard previous VDC and DORIC version (I4) rad hard to > 50Mrad detailed plan to certify radiation hardness LECC03, 9/30/2003 Richard Kass/OSU 6 DORIC and VDC Layout DORIC-I5 (2.3 x 4mm) VDC-I5 (1.4 x 4mm) Ch 4 Ch 3 Ch 2 Ch 1 Ch 1 Ch 2 Signal_in GndA Noise_in VddAmp VddA Ch 3 Input Pads: Ch 4 Preamp / Digital Test Pads 7 LECC03, 9/30/2003 Analog / Digital Bias, Resets Richard Kass/OSU VDC-I5e Measurements VDCI5e I-dim and I-bright vs Iset 15 bright Current (mA) 10 Eight VDCI5e chips with four channels per chip were measured 5 dim 0 0 0.5 1 Duty Cycle VDCI5 1.5 2 2.5 Current (mA) 54 VDCI5e duty cycle + Duty Cycle (%) 53 VDC-1 VDC-2 VDC-3 VDC-4 52 VDC-5 VDC-6 VDC-7 Spec is 50±4% VDC-8 51 50 0 1 LECC03, 9/30/2003 2 3 Channel # 4 5 8 Richard Kass/OSU VDC-I5e Rise and Fall Times VDCI5e Rise Times at Iset = 0.6 mA 2.0 rise time VDC-1, I_set = .6 mA VDC-2, I_set = .6 mA VDC-3, I_set = .6 mA VDC-4, I_set = .6 mA VDC-5, I_set = .6 mA VDC-6, I_set = .6 mA VDC-7, I_set = .6 mA VDC-8, I_set = .6 mA Time (ns) 1.5 1.0 0.5 0.0 0 1 2 3 4 5 spec is <1 ns VDCI5e Fall Times Channel # at Iset = 0.6 mA 0.8 fall time VDC-1, I_set = 0.6 mA VDC-2, I_set = 0.6 mA VDC-3, I_set = 0.6 mA VDC-4, I_set = 0.6 mA VDC-5, I_set = 0.6 mA VDC-6, I_set = 0.6 mA VDC-7, I_set = 0.6 mA VDC-8, I_set = 0.6 mA Time (ns) 0.7 0.6 0.5 0 1 2 3 4 5 9 Channel # LECC03, 9/30/2003 Richard Kass/OSU Status of BeO Opto-Board converts electricaloptical 6-7 links/board First BeO opto-boards arrive in April. Find problems: many vias not filled. Send boards back to company for repair. Company only partially successful with repairs (~50% success rate) We find a new company to produce the boards two populated opto-boards used for rad-hardness tests (more $$$ too) LECC03, 9/30/2003 10 Richard Kass/OSU Radiation Hardness Measurements CERN August 2003 Important to measure/certify radiation hardness of optical components VDC DORIC VCSEL Fibers Glues, etc… Use CERN’s T7 beam (24 GeV protons) for radiation hardness studies. We perform two types of radiation hardness tests: Cold Box: read out VDC and DORIC electrically (copper wires) Shuttle: readout VDC and DORIC via optical fibers VDC and DORICs mounted on BeO opto-board shuttle can be moved in and out of beam remotely For both tests we monitor the VDCs and DORICs in real time. 11 LECC03, 9/30/2003 Richard Kass/OSU CERN Irradiation Tests System for Irradiation in Cold Box PC BER Tester 20 MHz 0.2 m Ribbon Coaxial DORIC Distribution 25m Ribbon + 25 m Coaxial VDC Distribution Beam Area Distribution 0.5m Ribbon Test Boards VDC or DORIC Testing system at OSU before shipping to CERN 12 LECC03, 9/30/2003 Richard Kass/OSU Irradiation Tests Opto-board System for Irradiation in Shuttle Bit error test board in T7 control room Bi-phase marked optical signal 25 m fibers/wires Decoded data Opto-pack clock PIN DORIC data VCSEL VDC VCSEL VDC An irradiation test Opto-link measure power of clock and data Vs dose LECC03, 9/30/2003 Richard Kass/OSU 13 Setup for CERN’s T7 Shuttle shuttle test electronics at OSU prior to shipping to CERN 25m of optical fibers opto-boards Optical fibers Remotely moves in/out of beam 14 LECC03, 9/30/2003 Richard Kass/OSU Results from Irradiation Threshold for zero bit errors vs Dose Opto-board #1 anneal anneal anneal anneal anneal all other links: pseudo-random bit string and Ipin=100 uA Thresholds independent of dose LECC03, 9/30/2003 Richard Kass/OSU 15 Results from Irradiation Clock Optical Power Vs Dose Irradiate for ~4-6 MRad (~4-5 hours) Move boards out of the beam and anneal for 12-15 hours LVCSELs need time to anneal Monitor the optical power of each link in real time. Opto-board #2(BeO#4) Opto-board #1(BeO#3) anneal anneal anneal anneal anneal anneal anneal anneal anneal anneal Beam Iset = 0.6 mA (=10mA) for beam, 1.5mA (=1314mA) for annealing 16 LECC03, 9/30/2003 Richard Kass/OSU Summary and Conclusions VDC and DORIC chips satisfy ATLAS Specs BeO Opto-board: Original vendor not able to produce quality boards Have found new vendor updated layout submitted Radiation studies: Cold Box: VDC and DORIC are more than hard enough! Shuttle: VCSEL radiation hardness an issue will VCSELs anneal enough to meet power specs ? Move to Production in 2004 ~500 VDCs, ~400 DORICs, ~200 opto-boards (includes spares) 17 LECC03, 9/30/2003 Richard Kass/OSU