Fall 09 (New)

Name:

CAD of Digital VLSI

Dr. Ralph Etienne-Cummings

Exam 2: The Inverter, Combinational and Sequential Logic (1.5 hours, Open book)

November 11 th , 2009

Attempt all questions. Show all calculations to obtain partial credits. If you run out of time, outline how you would approach the problem.

Exam #2 (1.5 Hours)

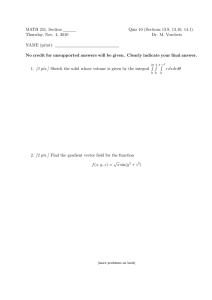

NMOSFET PMOSFET

K ( o

C ox

)

VTO

19.6 uA/V 2

0.74 V

0.6

0.06 V

Xd (Under Diffusion) 6 nm

-1

NSUB

COX

CGDO = CGSO

1.3 x 10^(16) cm -3

1.1 x 10^(-3) F/m 2

6.6 x 10^(-12) F/m

CJ 2.8 x 10^(-4) F/m 2

CJSW m b

= m sw

b

= sw

Depth of Well

1.7 x 10^(-10) F/m

0.5

1 V

5.4 uA/V 2

-0.74 V

0.6

0.19 V -1

6 nm

4.8 x 10^(15) cm -3

1.1 x 10^(-3) F/m 2

6.6 x 10^(-12) F/m

3.0 x 10^(-4) F/m 2

2.6 x 10^(-10) F/m

0.5

1 V

5um

P.1 (30 pts)

(a) Design a 3-input NAND gate with the average of the logic threshold voltages at

Vdd/2. (10 pts)

(b) Rank the logic threshold of the transitions starting from the highest to the lowest. (5 pts)

(c) Compute the longest and shortest fall times using the 90% - 10% criterion. (10 pts)

(d) Compute the peak power consumption for your design. (5 pts)

1

Name:

2

Name:

P.2 (40 pts)

(a)

Derive the Boolean function that counts the number of zero’s in a 4-bit number. (10 pts)

(b)

(c)

(d)

(e)

Draw the schematic of this function using pass transistor logic. (10 pts)

Estimate the speed of operation of your design if all minimum size transistors are used. (5 pts)

Redesign the circuit with Domino Logic gates. (10 pts)

Estimate the speed of operation of the new design if all minimum size transistors are used. (5 pts)

3

Name:

4

Name:

P.3 (30 pts)

(a)

(b)

(c)

Design an 8-bit counter. (10 pts)

Draw the schematic of one bit-slice of the counter. (10 pts)

Draw the timing diagram for the operation of the counter. (10 pts)

5

Name:

6

Name:

P.4 (30 pts)

(d)

Consider the function Y = ([A’BCG’]+[E + F])D’. Draw the CMOS schematic for the function. (Assume the inverses are available.) (10 pts)

(e)

(f)

(g)

If all the transistors are implemented with W/L = 1, Kp = Kn, and Vtop = Vton, what is the value of the logic threshold, VLT for a 0110110 to 1001001 transition. (10 pts)

Which transitions will have the longest and shortest rise and fall times. (10 pts)

What are the longest and shortest rise and fall times. (10 pts)

7

Name:

8