Fall 08 (New)

advertisement

CAD of Digital VLSI

Dr. Ralph Etienne-Cummings

Exam 2: The Inverter, Combinational and Sequential Logic (1.5 hours, Open book)

November 12, 2008

Attempt all questions. Show all calculations to obtain partial credits. If you run out of time,

outline how you would approach the problem. This exam will be graded out of 100.

Exam #2 (1.5 Hours)

P.1 (40 pts)

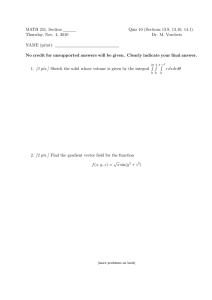

Consider the circuit in figure P1. Assuming that n = p, Vtn = Vtp = |1|V and = 0:

(a) What voltages must be applied to nodes (A) and (B) for Vout = Vin for Vin = {0, 5}.

(10 pts)

(b) Plot the DC characteristics, labeling all important features of the curve. (10 pts)

(c) Derive the expression for resistance of the transmission gate at Vin = Vout = Vmid

when the circuit is conducting. (10 pts)

(d) When the connection between Vin and Vout is open, the Vout node will float. This is

not desirable. Augment the circuit such that the Vout is never floating. Justify your

choice of augmentation, i.e. explain the pros and cons of your design. (10 pts)

Figure P.1

(a)

(b)

(c)

(d)

P.2 (40 pts)

Determine the two function(s) which indicate whether the decimal value of 3-bit

number is odd or even. (10 pts)

Using AND, OR and NOT gates, implement the results of (a). How many transistors

are required for CMOS implementation? (The direct translation.) (10 pts)

Now implement the circuit with Differential Cascode Voltage Switch Logic

(DCVSL). How many transistors does this implementation require. (10 pts)

Assuming the load PMOS in (c) has a W/L=1, Kn = 2*Kp = 10uA/V2, Vtn = Vtp =

|1|V, Vdd = 5V, = =0, determine the W/L for the NMOSes in the path which runs

the highest risk of NOT switching the state of the output. Identify this path clearly.

(10 pts)

P.3 (45 pts)

(a) Consider the function Y = [(AB’+C D’)(E’F)]. Draw the CMOS schematic for the

function. (Assume the inverses are available.) (10 pts)

(b) If all the transistors are implemented with W/L = 1, Kp = Kn, and Vtop = Vton, what

is the value of the logic threshold, VLT for a 101001 to 010110 transition. (5 pts)

(c) Which transitions will have the longest and shortest rise and fall times. (10 pts)

(d) What are the longest and shortest rise and fall times. (20 pts)

P.4 (40 pts)

(a) Starting with a single clock, design e circuit that will generate a 2-phase nonoverlapping clock. (10 pts)

(b) Labeling all the internal nodes of your design, draw a timing diagram to show how

your design works. (20 pts)

(c) In your design, how would you increase the delay between the two phases of the nonoverlapping clock. (10 pts)