Fall 08

advertisement

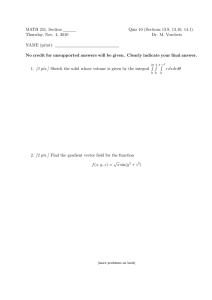

Name: CAD of Digital VLSI Ralph Etienne-Cummings Exam 1: Devices, Circuits and Interconnections (1.5 hours, Open book) October 8th, 2008 Attempt all questions. Show all calculations to obtain partial credits. If you run out of time, outline how you would approach the problem. The exam will be graded out of 120 pts (i.e. 30 pts extra credit). 1 Name: P1: (i) Three pieces of Si with donor concentration 1018 cm-3, acceptor concentration 1016 cm-3 and donor concentration of 1015 cm-3, respectively, are abutted. (55 points) (a) Draw the band diagrams before and after they are abutted. (5 points) (b) Compute the built in potential for each junction. (10 points) (c) Sketch and compute the depletion width on each side of each junction. (15 points) (d) Compute the capacitance for each of the junctions when no external voltage is applied. (10 points) (e) Can you name this type of device? (5 points) (f) Draw the cross-section of an implementation of this device for the 0.5um CMOS process. (10 points) 2 Name: 3 Name: P2. Consider the circuit in figure P2. Assume Kn =10uA/V2, Kp=5uA/V2, Vton = |Vtop| = 1V, =0 and =0 V-1. (40 pts) (a) Draw the I vs. Vo curves for this circuit when Vin = 0V and 5V. (10 pts) (b) Compute the Logic Threshold (VLT) for this circuit. (10 pts) (c) How would you expect the Vo to change in (a) and (b) if =0.5? (10pts) (d) Draw the cross-section of the circuit, showing all relevant connections, parasitic diodes and capacitors and shapes of the channels when Vin = 5V. (10 pts) P.2 4 Name: 5 Name: P3. For the circuit P.2, compute (Drain_length = Source_Length = 4u): (20 pts) (a) The capacitance at the input node, Vin @ Vin = 0V. (5 pts) (b) The capacitance at the output node, Vout @ Vin = 0V. (5 pts) (c) The capacitance at the input node, Vin @ Vin = 5V. (5 pts) (d) The capacitance at the output node, Vout @ Vin = 5V. (5 pts) 6 Name: 7 Name: P4. Consider the circuit figure P4. Using the parameter set below, and assuming that the lengths of the drain and source are 4um, (35 pts) a) What are the maximum and minimum voltages for Vout, assuming that the circuit is powered from 0 – 5V. (10 points) b) Compute the resistance of the conducting PMOS when Vin = Vout = 1V and 4V. (10 pts) c) List all the components of the capacitance at the Vout node. (5 points) d) Estimate the total area of the circuit if implemented in the 0.5um CMOS process using SCMOS rules. (10 pts) Process Parameters: NMOSFET PMOSFET K (oCox) 19.6 uA/V2 5.4 uA/V2 VTO 0.74 V -0.74 V 0.6 0.6 0.06 V-1 0.19 V-1 Xd (Under Diffusion) 6 nm 6 nm NSUB 1.3 x 10^(16) cm-3 4.8 x 10^(15) cm-3 COX 1.1 x 10^(-3) F/m2 1.1 x 10^(-3) F/m2 CGDO = CGSO 6.6 x 10^(-12) F/m 6.6 x 10^(-12) F/m CJ 2.8 x 10^(-4) F/m 2 3.0 x 10^(-4) F/m2 CJSW 1.7 x 10^(-10) F/m 2.6 x 10^(-10) F/m mb = msw b = sw Depth of Well 0.5 1V 0.5 1V 5um 8 Name: 9 Name: 10