Fall 03

advertisement

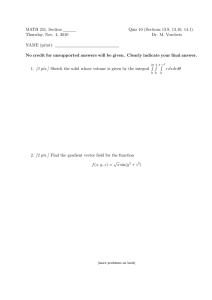

Name: SS#: CAD of Digital VLSI Ralph Etienne-Cummings Exam 1: Devices, Circuits and Interconnections (1.5 hours, Open book) September 30, 2003 Attempt all questions. Show all calculations to obtain partial credits. If you run out of time, outline how you would approach the problem. The exam will be graded out of 120 pts (i.e.20 pts extra credit). 1 Name: SS#: P1: Consider the circuit in figure P.1. An input square wave with amplitude +/-10V, 50% duty cycle and 100KHz is applied to the input. The diodes have the following characteristics: Vd(ON) = 0.7V, Area=12um2 (i.e. 3um x 4um), AD = 1, Xj (diffusion depth) = 2um, m=0.5, Na=1016 and Nd = 1017. (35 pts) (a) Calculate minimum and maximum voltages observed at the output node. (5 pts) (b) Sketch the temporal waveform observed at the output node (ignore the parasitic capacitance introduced by the diode). (10 pts) (c) Compute the parasitic capacitance of the diode. If it was considered in (b), how would it have changed the observed waveform? (20 pts) P.1 2 Name: SS#: 3 Name: SS#: P2. Consider the circuit in figure P2. Assume Kn =10uA/V2, Kp=5uA/V2, Vton = |Vtop| = 1V, =0 and =0 V-1. (40 pts) (a) Compute Vo if Vin = 0V and 5V. (10 pts) (b) Sketch the transfer function as Vin is swept from 0V to 5V. (10 pts) (c) How would you expect the Vo to change in (a) and (b) if =0.5? (10pts) (d) Draw the cross-section of the circuit, showing all relevant connections, parasitic diodes and capacitors and shapes of the channels when Vin = 0V. (10 pts) P.2 4 Name: SS#: 5 Name: SS#: P3. Using the grid below, draw the layout of circuit in P.2. Label (or color or shade) each layer. Use the SCMOS design rules, Lambda = 1.0um design rules for the design. Let each square be 2x 2 (20 pts) 6 Name: SS#: 7 Name: SS#: 8 Name: SS#: P4. A circuit calls for a passive RC filter low-pass with cut-off frequency of 10MHz. (45 pts) a) Explain how you would select the resistor and capacitor values. (5 pts) b) Explain how you would select the layers to implement the resistor and capacitor. (5 pts) c) Outlining the pros and cons of using at least two other choices for each (vis-à-vis your choices). (10 pts) d) Estimate the area of the RC filter design in the 0.5um CMOS process using SCMOS rules. (5 pts) e) Design a 2 transistor CMOS circuit to implement the filter. (5 pts) f) Estimate the sizes of the transistors. (10 pts) g) Explain the pros and cons the transistor circuit versus the passive circuit. (5 pts) 9 Name: SS#: 10 Name: SS#: NMOSFET PMOSFET VTO 19.6 uA/V2 0.74 V 5.4 uA/V2 -0.74 V 0.6 0.6 0.06 V-1 6 nm 0.19 V-1 1 nm COX 1.3 x 10^(16) cm-3 1.1 x 10^(-3) F/m 4.8 x 10^(15) cm-3 1.1 x 10^(-3) F/m CGDO = CGSO 9.6 x 10^(-12) F/m 1.7 x 10^(-12) F/m CJ 2.8 x 10^(-4) F/m2 1.7 x 10^(-10) F/m 3.0 x 10^(-4) F/m2 2.6 x 10^(-10) F/m K Xd (Under Diffusion) NSUB CJSW 11