FPGA tutorial for Logic project

advertisement

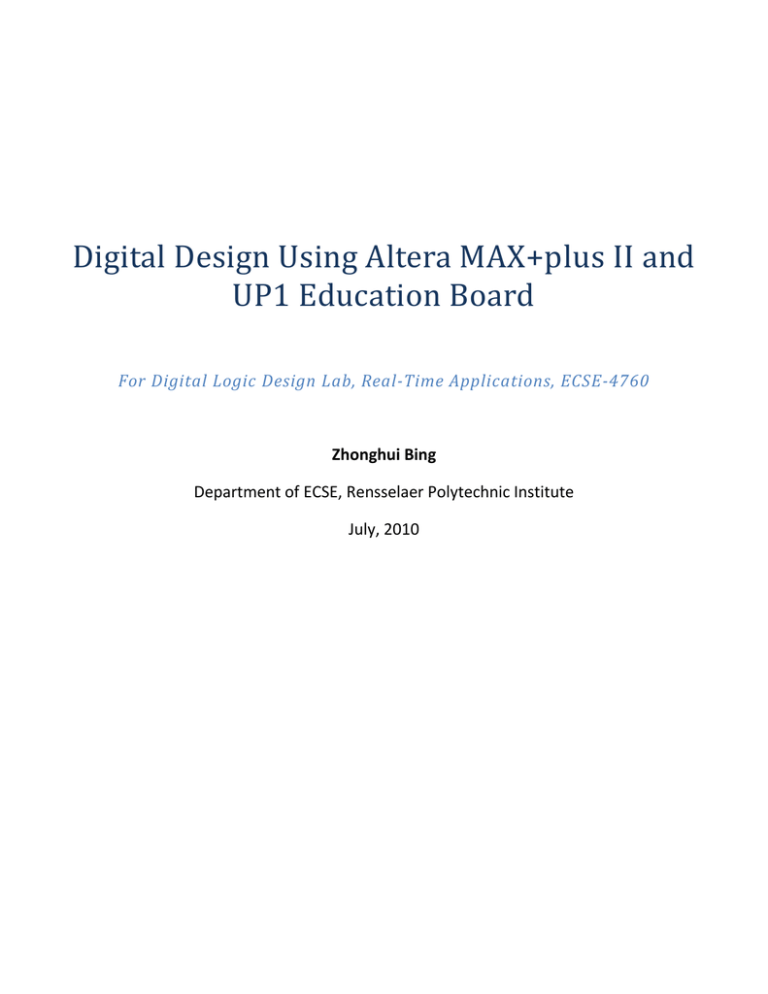

Digital Design Using Altera MAX+plus II and UP1 Education Board For Digital Logic Design Lab, Real-Time Applications, ECSE-4760 Zhonghui Bing Department of ECSE, Rensselaer Polytechnic Institute July, 2010 Introduction UP1 Educational Board The University Program (UP) Design Laboratory Package (referred to as UP1) was designed and released by Altera to meet the needs of universities teaching digital logic design with the development tools and programmable logic devices (PLDs). The UP 1 Education Board has many features that facilitate rapid prototyping of digital logic. MAX+plus II Software The logic designs that are entered on the UP 1 Education Board require the use of special CAD software to configure the Flex10K20 CPLD/MAX7128 FPGA. Students will use software that runs on standard PCs under Windows. The general engineering design cycle which is supported by the Altera MAX+plus II software is highlighted. The process includes the design entry, project verification, project processing, and device programming. The UP1 contains 2 programmable logic devices, a MAX7128 and a FLEX 10K, along with several I/O devices. The MAX7128 may be connected to two pushbutton switches (PB1 & PB2), two 8-bit DIP switches (SW1_1 – 8 & SW2_1 – 8), 16 LEDS (D1 – D16), and two 7-segment displays with decimal points for inputs and outputs. The FLEX 10K has access to two pushbutton switches (FLEX_PB1 & FLEX_PB2), a single 8-bit DIP switches (SWITCH_1 – 8), and two 7-segment displays with decimal points for inputs and outputs. To speed up the development process of implementing a state machine on the hardware, an example (bcounter.gdf) is provided that uses most of the I/O available in a simple counter circuit. It is strongly suggested that students copy this example as a starting point and modify it to implement the state machine developed as the final project for the Digital Logic Design Experiment in Real-Time Applications in Control & Communications. The input block on the left side of the circuit, which also includes switch debouncing and multiple clock outputs, and the output block on the right side will remain relatively unchanged in student implementations. Only the logic circuit between the 2 blocks that manifest the project will be modified. Before building the circuit for the Digital Logic Design final project, the counter example should be compiled, downloaded, and executed to verify the operation of the UP1 board. The bcounter.gdf circuit is a 4-bit up/down counter that uses PB1 to change the count direction and PB2 to clear the counter. LEDs D0 – D4 display the binary value of the count along with the decimal value on the 7-segment display (with other symbols representing hexadecimal A through F). DIP switch 1 on SW2 controls D9. In order for the counter to work external wires must be added to the board between the I/Os and the MAX7128 chip. The required connections between the MAX headers and the switches/LEDs are list below in the table under Hardware Connections. Initial Setup There are 4 jumpers on the top left of the UP1 board labeled TD1, TD0, DEVICE, and BOARD that should be as follows: This brief tutorial will only discuss use of the MAX7128 FPGA. Students wishing to implement circuits on the FLEX 10K CPLD will be referred to the Altera reference manuals for additional set-up information. Plug in the +5V and Ground connections to the board. Connect the parallel port on the PC to the ByteBlasterMV port on the UP1 card. The required software tools should be on the lab computers under All Programs MAX+plus II 10.2 BASELINE MAX+plus II 10.2 BASELINE. If this is missing you will need to use a different computer. Hardware Connections The following table summarizes the connected external components. The Pin numbers refer to that on the MAX7128 chip while the label in parentheses is the header pin number. P1, P2, P3, & P4 are the 4 header that surround the MAX7128. These jumpers must be in place for the bcounter.gdf demonstration to work. Component SW1_DIP 1 SW1_DIP 2 SW1_DIP 3 SW1_DIP 4 SW1_DIP 5 SW1_DIP 6 SW1_DIP 7 SW1_DIP 8 MAX_PB1 MAX_PB2 7128 Pin 28 (P2_17) 30 (P2_19) 31 (P2-20) 29 (P2_18) 34 (P3_2) 33 (P3_1) 35 (P3_3) 36 (P3_4) 24 (P2_13) 25 (P2_14) Component Diode D1 Diode D2 Diode D3 Diode D4 Diode D5 Diode D6 Diode D7 Diode D8 Diode D9 SW2_DIP 1 7128 Pin 57 (P4_4) 56 (P4_3) 55 (P4_2) 54 (P4_1) 52 (P3_20) 51 (P3_19) 50 (P3_18) 49 (P3_17) 80 (P1_6) 37 (P3_5) The following assignments have been defined in bcounter.gdf but are not used by the circuit. They are there for use in student circuits if more inputs and output are required by the project. As before, external wires must be placed between the corresponding DIP switch or LED header pin and the header pin on the MAX7128 to use that particular input or output. Defining these new connections could be a little confusing so it was decided to just create all the possible connections the MAX7128 supported on the UP1 board in the demonstration program to reduce student frustration. Component SW2_DIP 1 SW2_DIP 2 SW2_DIP 3 SW2_DIP 4 SW2_DIP 5 SW2_DIP 6 SW2_DIP 7 SW2_DIP 8 7128 Pin 37 (P3_5) 39 (P3_7) 40 (P3-8) 41 (P3_9) 44 (P3_12) 45 (P3_13) 46 (P3_14) 48 (P3_16) Component Diode D9 Diode D10 Diode D11 Diode D12 Diode D13 Diode D14 Diode D15 Diode D16 7128 Pin 80 (P1_6) 81 (P1_7) 4 (P1_14) 5 (P1_15) 6 (P1_16) 8 (P1_18) 9 (P1_19) 10 (P1_20) Schematic Design In addition to using Hardware Description Languages (HDL), users can enter a digital logic design via schematic capture techniques using Graphic Editor. The design will be entered using the graphic editor, processed with the MAX+plus II software and verified using functional simulation. The design will then be used to configure the MAX7128 portion of the UP 1 Educational Board. bcounter.gdf is provided to students to facilitate the design process. All I/O ports that can be directly applied to a user’s circuit have been pre-defined. These are located in the dashed black boxes and user should avoid modifying them. The input components have a group of clock sources: CLK_1M (meaning 1 MHz), CLK_100K, …, and CLK_1Hz (1 Hz), two push buttons, and sixteen DIP switch inputs. The outputs have two groups of 7-segment displays and sixteen diodes (LEDs). Users can modify and add circuits in between the blocks and route the necessary I/Os. Running the Demonstration The quick start for initially using the boards involves running the MAX+plus II program, opening the bcounter.gdf file, compiling the design (and specifying it to be the current project if asked), starting the programmer utility and initiating the program process. After starting All Programs MAX+plus II 10.2 BASELINE MAX+plus II 10.2 BASELINE, use File Open to open the file bcounter.gdf in c:\mp2student\counter\bcounter.gdf. You will see the schematic with the input block on the left, the output block on the right, and the counter circuit in the middle shown below. Select the Compile button (see below) to compile the circuit. If you see a warning saying the file is not recognized as being part of the current project, click on Yes to change the project. The other compiler warnings may be ignored since there are several inputs that are not used and some pins that are disabled by holding them high. Close the windows associated with the compiler operation and select the Program button. The following window will appear: Click on the Program button in the window to begin the download process. If everything is set up correctly and there are no errors in the schematic or its configuration, you will get a message saying: Programming complete. Close the windows associated with programming the UP1. At this point the circuit will begin to operate automatically. The counter will count pulses from the 1Hz clock on the board and the LEDs and 7-segment display will show the value of the counter. PB1 and PB2 will change the direction of the counter and clear it, respectively. Design Steps To implement the project portion of the Digital Logic Experiment it will probably be easiest to reenter the schematic using the MAX+plus II tools rather than try to figure out how to export it from LogicWorks. LogicWorks may be used to debug the design since its tools for doing that are easier to use than MAX+plus II. Alternatively LogicWorks may be skipped altogether and the project entered directly into MAX+plus II. As previously mentioned, students should create a new folder in c:\md2students and COPY (NOT MOVE) the files from c:\md2students\counter into it to kick-start the design process. The assigned I/O pins may be used as defined, but if you are ambitious you may redefine them anyway you like and make sure you rewire the connections between the MAX headers and the switches/LEDs. Read the up1ug.pdf file on the studio web site for a more detailed description of the hardware. Of the 84 pins surrounding the MAX7128 FPGA, 16 are permanently reserved for use by the two 7-segment displays and 24 are not useable. The pins reserved for the displays are: Unusable pins are: 1, 2, 3, 7, 13, 14, 19, 23, 26, 32, 38, 42, 43, 47, 53, 59, 62, 66, 71, 72, 78, 82, 83, and 84. Users employ the Altera MAX+plus II to graphically enter the symbols that represent each of the components that make up the design and then use the tool to ‘wire’ the components to one another to form the complete schematic diagram. The procedures are generally the same as those used in LogicWorks. The first step in the schematic capture design process, after opening your copy of the counter gdf file, is to enter each of the components which make up the design. This can be accomplished within the Altera MAX+plus II environment by double clicking the mouse with the cursor pointing on the white space of current gdf file. This will launch the “Enter Symbol” Window as shown below: This window contains the high-level macros and low-level primitive components which can be included in the design. The system libraries are: 1. prim (primitive library) – c:\maxplus\max2lib\prim – A set of basic functional blocks used to design circuits with MAX+plus II software. The primitives include buffers, flip-flops, latches, input and output primitives, and logic primitives. 2. mf (mega functions) – c:\maxplus\max2lib\mf – A set of complex or high-level building blocks (i.e. macros) that can be used together with gate and flip-flop primitives in MAX+plus II design files. 3. mega_lpm (library of parameterized modules) – c:\maxplus\max2lib\mega_lpm – A technology-independent library of logic functions that are parameterized to achieve scalability and adaptability. 4. mega_lpm (library of parameterized modules) – c:\max2work\up1core – A library of high-level logic functions with useful features such as switch debouncing and clock divide-downs. UP1core lib is a customized library for UP1 board by Altera. It can be obtained from the CStudio website if it isn’t already present. Components are wired together by moving the cursor over to a wire or bus connection point on the symbol (component). At this point in time the cursor will turn into a ‘+’ sign. The left mouse button is then pressed and held and the cursor is then moved over to the desired termination point and the mouse button is released. In this process other wires and busses can act as starting and termination points. Individual wires (i.e. nodes) can be brought out from collections of nodes (i.e. buses) simply by giving the node the same name as the desired component of the bus. To name a node (wire) or a bus, simply double click on the wire or bus using the left mouse button and type in the node or bus name. Bus names usually have the following format: bus name [most significant element number .. least significant element number] For example, in the binary counter design there is a simple bus named q[31..0]. This implies that there are 32 nodes contained within the bus that are individually named q31, q30, ..., q1, q0, respectively. Compilation and Download The design compilation and download can be simply done by using the buttons as shown previously. Remember to connect the ByteBlasterMV and power up the board. When the Program icon is selected, the Programmer window appears. Programming begins after the Program button is selected. Reference [1] Altera University Program Design Laboratory Package (User Guide), Altera Corporation, ver. 2.0, October 2001. [2] MAX+plus II Programmable Logic Development System: Getting Started, Altera Corporation.