CIT 110 Syllabus.docx

advertisement

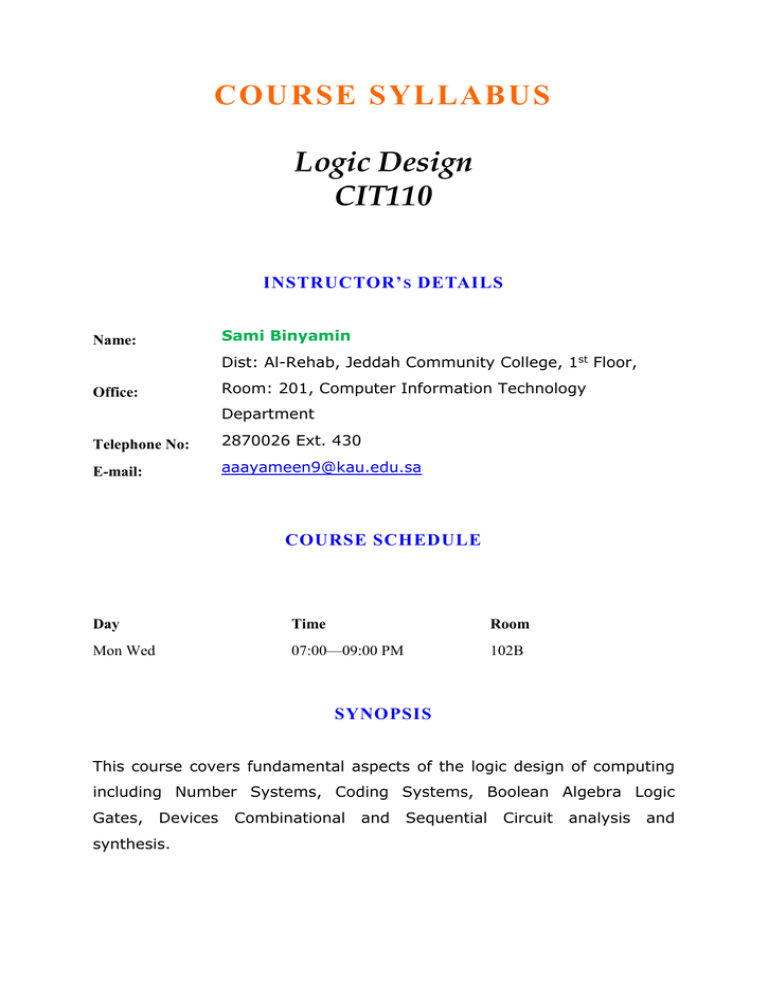

COURSE SYLLABUS Logic Design CIT110 INSTRUCTOR’ S DETAILS Sami Binyamin Name: Dist: Al-Rehab, Jeddah Community College, 1st Floor, Room: 201, Computer Information Technology Office: Department Telephone No: 2870026 Ext. 430 E-mail: aaayameen9@kau.edu.sa COURSE SCHEDULE Day Time Room Mon Wed 07:00—09:00 PM 102B SYNOPSIS This course covers fundamental aspects of the logic design of computing including Number Systems, Coding Systems, Boolean Algebra Logic Gates, Devices synthesis. Combinational and Sequential Circuit analysis and King AbdulAziz University Course Plan LEARNING OUTCOMES After completing the course, students should be able to: 1. Explain the binary and hexadecimal number system. 2. Describe the relationship between Boolean Algebra and digital logic. 3. Explain the integration of various logic devices into a microprocessor system. COURSE OUTLINE I. Number systems, codes and arithmetic operations. a. Binary and hexadecimal numbers b. Addition/subtraction of signed numbers c. BCD and ASCII codes II. Boolean algebra, basic logic gates: a. AND, OR, NOT, NAND and NOR gates b. Analysis and synthesis of simple logic circuits c. Map simplifications III. Medium scale integrated circuit Chapters: a. Adders b. Decoders c. Encoders d. Multiplexers and demultiplexers IV. Sequential logic: a. Latches and flip flops b. Timing diagrams c. Synchronous, asynchronous and pseudo counters d. Registers, and registers transfer equation V. Programmable logic VI. Memory a. ROM b. RAM VII. Processor design: a. Organization of a simple ALU. Jeddah Community College -2- CIT110 Logic Design King AbdulAziz University Course Plan WEEKLY PLAN Dates Week Chapter Topic 1 Introduction to Number system, codes and arithmetic operations 1 Introduction to Number system, codes and arithmetic operations 2 Boolean algebra, basic logic gates 4 3 Boolean algebra, basic logic gates 5 3 Medium Scale Integrated circuit Chapters 09/02—15/02 1 16/02—22/02 2 Assignments Quizzes Mid Exam Remarks: Submission Deadline for Assignments Assignment 1 Assignment 1 23/02—01/03 3 Due Date: 24/02/2014 02/03—08/03 Chapter 1, 2 09/03—15/03 16/03 – 22/03 6 4 Quiz 1 Due Date: 03/03/2014 Medium Scale Integrated circuit Chapters Semester Break 23/03 To 29/03 30/03—05/04 7 4 Sequential Logic Assignment 2 06/04—12/04 8 5 Assignment 2 Due Date: 07/04/2014 Sequential Logic Chapter 1, 2, 3, 4 13/04—19/04 9 5 Programmable Logic Mid Exam Due Date: 14/04/2014 Jeddah Community College -3- CIT110 Logic Design King AbdulAziz University Course Plan 20/04—26/04 10 6 Programmable Logic 27/04—03/05 Chapter 5, 6 11 7 Memory 12 8+9 Processor Design Quiz 2 Due Date: 28/04/2014 04/05—10/05 To Be Announced Later Jeddah Community College FINAL EXAMINATION -4- CIT110 Logic Design King AbdulAziz University Course Plan ASSESSMENT BREAKDOWN & POLICY Students’ assessments in this course are based on the following: 1. 2. Carry Marks or Course Work Marks: Marks % a. Assignments 20% b. Mid-Semester Examination 30% c. Quizzes 10% Final Examination: 40 % Total 100 % Jeddah Community College -5- CIT110 Logic Design King AbdulAziz University Course Plan ATTENDANCE POLICY Attendance is mandatory. Instructor is required to keep attendance records and report absences. Due to the interactive nature of this course, attendance is an essential part of the educational experience. JCC expects students to exercise good judgment regarding attendance. Students accept full responsibility for ensuring that work does not suffer from absence. Punctuality is important. The instructor may not allow student(s) to enter the classroom if he/she is a habitual latecomer. Students with ZERO absence will be upgraded to the next grade, if passed. Registration to a course and dropping procedure is a student’s responsibility The proof of registration should be shown in the first class The students are expected to be in class from the beginning of class Proof of valid reasons for absences will be verified by authority after receiving DN Those who come in the class within 10 minutes are considered LATE After ten (10) minutes the students are marked absent After three weeks equivalent absence, a grade of “DN” (Denied) will be issued It's responsibility of the student to keep the record of his absences Electronic devices must be turned off during all class and Lab times. Otherwise he may be asked to leave class and will be marked absent. Jeddah Community College -6- CIT110 Logic Design King AbdulAziz University Course Plan REFERENCES Main Reference: 1. Logic and Computer Design Fundamental, by M.Moris Mano and Charles R. Kime, 4th Edition, Prentice Hall, 2007. Additional Reference: 1. Logic Functions and Equations: Binary Models for Computer Science, by Christian Posthoff, Bernd Steinbach, Springer; 1st Edition. 2011 Jeddah Community College -7- CIT110 Logic Design