نـمـاذج أســئـلـة

advertisement

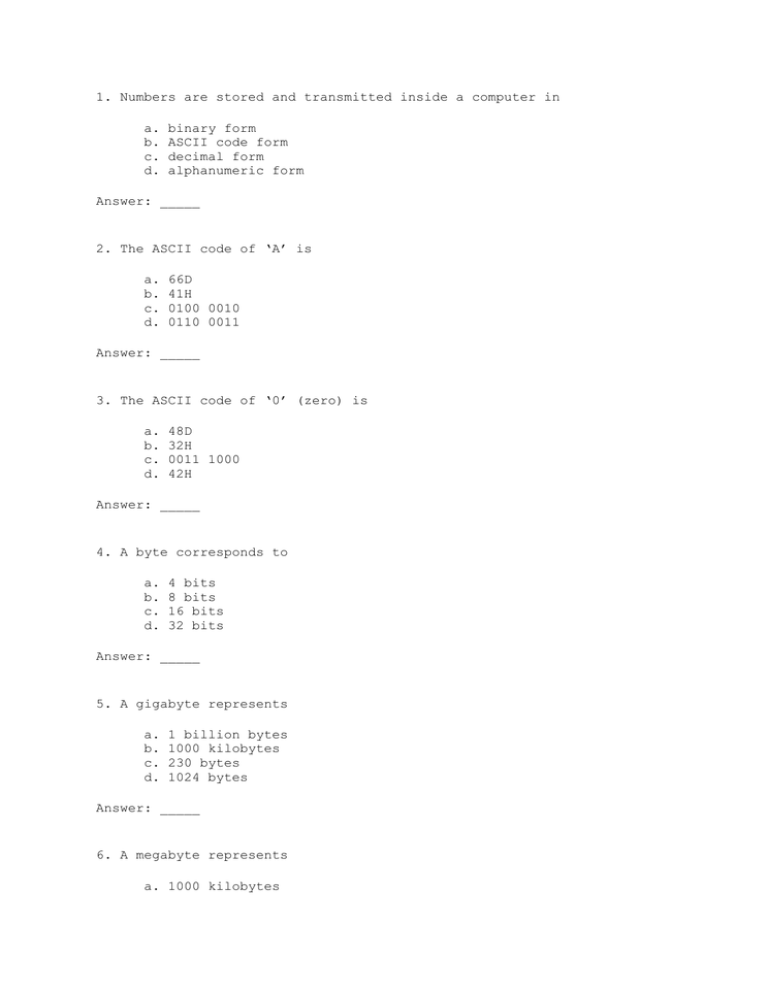

1. Numbers are stored and transmitted inside a computer in a. b. c. d. binary form ASCII code form decimal form alphanumeric form Answer: _____ 2. The ASCII code of ‘A’ is a. b. c. d. 66D 41H 0100 0010 0110 0011 Answer: _____ 3. The ASCII code of ‘0’ (zero) is a. b. c. d. 48D 32H 0011 1000 42H Answer: _____ 4. A byte corresponds to a. b. c. d. 4 bits 8 bits 16 bits 32 bits Answer: _____ 5. A gigabyte represents a. b. c. d. 1 billion bytes 1000 kilobytes 230 bytes 1024 bytes Answer: _____ 6. A megabyte represents a. 1000 kilobytes b. 220 bytes c. 1024 bytes d. 1 million bytes Answer: _____ 7. A Kb corresponds to a. b. c. d. 1000 bytes 1024 bits 210 bytes 210 bits Answer: _____ 8. A 32-bit processor has a. b. c. d. 32 registers 32 I/O devices 32 Mb of RAM 32- bit registers Answer: _____ 9. Information is stored and transmitted inside a computer in a. b. c. d. ASCII code form decimal form binary form alphanumeric form Answer: _____ 10. The minimum number of bits required to store the hexadecimal number FF is a. b. c. d. 2 4 8 16 bits Answer: _____ 11. A 20-bit address bus allows access to a memory of capacity a. 2 Mb b. 1 Mb c. 32Mb d. 64 Mb Answer: _____ 12. A 32-bit address bus allows access to a memory of capacity a. b. c. d. 64 Mb 16 Mb 1 Gb 4 Gb Answer: _____ 13. Clock speed is measured in a. b. c. d. bits per second baud bytes Hertz Answer: _____ 14. Pipelining improves CPU performance due to a. b. c. d. reduced memory access time increased clock speed the introduction of parallellism additional functional units Answer: _____ 15. The system bus is made up of a. b. c. d. data data data data bus bus and address bus bus and control bus bus, control bus and address bus Answer: _____ 16. A machine cycle refers to a. b. c. d. fetching an instruction clock speed fetching, decoding and executing an instruction executing an instruction Answer: _____ 17. CISC machines a. b. c. d. have fewer instructions than RISC machines use more RAM than RISC machines have medium clock speeds use variable size instructions Answer: _____ 18. ROM a. b. c. d. is volatile is non-volatile stores more information than RAM is used for cache memory Answer: _____ 19. Which of the following is an illegal instruction a. b. c. d. MoV iNc aNd add Ax, Al, bx, ax, 30000 1 bx 30 Answer: _____ 20. Which of the following is an illegal instruction a. b. c. d. MoV iNc aNd add Ax, 30000 Al bx, bx ax 30 Answer: _____ 21. Given that the bl register contains 1111 0000, the effect of the following instruction OR BL, 0000 1111 is to a. b. c. d. clear store store leave Answer: _____ bl 1111 1111 in bl 0000 1111 in bl bl unchanged 22. Which of the following is an illegal 8086 instruction a. b. c. d. iNc aNd mov add Al bx, bx 20, bx ax, 30 Answer: _____ 23. Which of the following is an illegal 8086 instruction a. b. c. d. mov iNc aDd add ax, [bx] [bx] bx, [bx] ax [bx] Answer: _____ 24. Which of the following is an illegal 8086 instruction a. b. c. d. mov iNc aDd add ax, [bx] [bx] bx, [dx] [bx], 1 Answer: _____ 25. A Harvard architecture means that a machine has a. b. c. d. separate memories for data and instructions unified cache memory multiple functional units an on-chip cache Answer: _____ 26. The read/write line is a. b. c. d. belongs to the data bus belongs to the control bus belongs to the address bus CPU bus Answer: _____ 27. The instruction INC X where X is a memory variable involves a. a memory read operation b. a memory write operation c. a memory read and a memory write operation d. only an arithmetic operation Answer: _____ 28. A hardware interrupt is a. b. c. d. also called an internal interrupt also called an external interrupt an I/O interrupt a clock interrupt Answer: _____ 29. An assembly language program is typically a. b. c. d. non-portable shorter than an equivalent HLL program harder to read than a machine code program slower to execute than a compiled HLL program Answer: _____ 30. An assembly language program is translated to machine code by a. b. c. d. an assembler a compiler an interpreter a linker Answer: _____ 31. Which of the following is not part of the processor a. b. c. d. the the the the ALU CU registers system bus Answer: _____ 32. Which of the following defines a constant Max a. b. c. d. Max Max Max mov db 80 equ 80 dw 80 Max, 80 Answer: _____ 33. The call instruction is used to a. b. c. d. access subprograms access memory perform I/O access the stack Answer: _____ 34. The effect of the following instructions: to a. b. c. d. read a character into read a character into display the character display the character MOV AH, 2H - INT 21H is al dl stored in al stored in dl Answer: _____ 35. The effect of the following instructions MOV AH, 1h - INT 21h is to a. b. c. d. read a character into read a character into display the character display the character al dl stored in al stored in dl Answer: _____ 36. Given that AL contains the ASCII code of an uppercase letter, it can be converted to lowercase by a. b. c. d. add al, 32 sub al, 32 or al, 1101 1111 and al, 0010 0000 Answer: _____ 37. Given that al contains the ASCII code of a lowercase letter, it can be converted to uppercase by a. b. c. d. add al, 32 sub al, 32 or al, 1101 1111 and al, 0010 0000 Answer: _____ 38. Given that AL contains the ASCII code of an uppercase letter, it can be converted to lowercase by a. b. c. d. add al, 20h sub al, 20h or al, 0010 0010 and al, 0010 0010 Answer: _____ 39. Given that AL contains the ASCII code of a lowercase letter, it can be converted to uppercase by a. b. c. d. add al, 20h sub al, 20h or al, 1101 1111 and al, 1101 1111 Answer: _____ 40. The instruction jg operates with a. b. c. d. unsigned numbers 2’s complement numbers floating point numbers ASCII codes Answer: _____ 41. The instruction ja operates with a. b. c. d. unsigned numbers signed numbers floating point numbers ASCII codes Answer: _____ 42. The instruction mov ax, [bx] is an example of a. b. c. d. indirect addressing indexed addressing direct addressing based addressing Answer: _____ 43. The instruction( je label) is an example of a. b. c. d. indirect addressing indexed addressing relative addressing immediate addressing Answer: _____ 44. The word size of an 8086 processor is a. b. c. d. 8 bits 16 bits 32 bits 64 bits Answer: _____ 45. The code used to boot up a computer is stored in a. b. c. d. RAM ROM Hard disk CD ROM Answer: _____ 46. Given that dl contains 'x' which of the following will cause 'x' to be displayed a. b. c. d. mov mov mov mov ah, ah, ah, ah, 1h - int 21h 2h - int 20h 2 - int 21h 0h - int 21h Answer: _____ 47. Which of the following will read a character into AL a. b. c. d. mov mov mov mov Answer: _____ ah, ah, ah, ah, 9h 2h 2h 1h - int int int int 21h 20h 21h 21h 48. Which of the following will display a string whose address is in the DX register a. b. c. d. mov mov mov mov ah, ah, ah, ah, 0h 2h 9h 9h - int int int int 21h 20h 21h 22h Answer: _____ 49. Which of the following will terminate a program and return to operating system a. b. c. d. mov mov mov mov ax, ax, dx, ax, 4c00h 4c00h 4c00h 9h - - int 20h - int 21h - int 21h int 22h Answer: _____ 50. The cmp instruction modifies the a. instruction pointer b. instruction register c. flags register d. segment register 51.The bp register is typically used for accessing a. strings b. memory *c. stack d. data segment Answer: _____ 51. The RET instruction modifies the a. b. c. d. instruction register instruction pointer address register flags register Answer: _____ 52. The SP register is typically used for accessing a. b. c. d. strings memory stack data segment Answer: _____ 53. The CALL instruction modifies a. b. c. d. the program counter and SP register flags register bp register none of the previous Answer: _____ 54. In 8086 microprocessor , the address bus is ________ bit wide a. b. c. d. 12 10 16 20 bit bit bit bit Answer: _____ 55. The CF is known as ________ a. b. c. d. carry flag condition flag common flag single flag Answer: _____ 56. The SF is called as ________ a. b. c. d. service flag sign flag single flag condition flag Answer: _____ 57. The register AX is formed by grouping ________ a. b. c. d. AH BH CH DH & & & & Answer: _____ AL BL CL DL 58. The IP is ________ bits in length a. b. c. d. 8 bits 4 bits 16 bits 32 bits Answer: _____ 59. The PUSH SOURCE copies a word from source to ______ a. b. c. d. stack memory register destination Answer: _____ 60. INC DESTINATION increments the content of DESTINATION by _______ a. b. c. d. 1 2 30 41 Answer: _____ 61. _________ DESTINATION inverts each bit of DESTINATION a. b. c. d. NOT NOR AND OR Answer: _____ 62. The _________ translates a byte from one code to another code a. b. c. d. XLAT XCHNG POP PUSH Answer: _____ 63. ________ line is used to write into memory a. b. c. d. RD WR RD / WR Chk Answer: _____ 64. A _____ Instruction at the end of interrupt service program takes the execution back to the interrupted program a. b. c. d. forward return data line Answer: _____ 65. The data pins are _______ data lines and are connected to data bus in system a. b. c. d. unidirectional bidirectional directional multidirectional Answer: _____ 66. The _______ allow data transfer between memory and peripherals a. b. c. d. DMA technique Microprocessor Register Decoder Answer: _____ 67. 8088 microprocessor differs with 8086 microprocessor in _______ a. b. c. d. data width on the output address capability support of coprocessor support of MAX / MIN mode Answer: _____ 68. The address bus flow in __________ a. bidirection b. unidirection c. mulidirection d. circular Answer: _____ 69. The translator program used in assembly language is called a. b. c. d. Compiler Interpreter Assembler Translator Answer: _____ 70. A compiler is a translating program which a. Translates a high level language program into machine language b. Translates assembly source program into machine language program c. It is not involved in program’s execution d. All of above Answer: _____ 71. Which of the following is a machine independent program a. b. c. d. High level language Low level language Assembly language Machine language Answer: _____ 72. Which of the following is a secondary memory device a. b. c. d. Keyboard Hard disk ALU All of the above Answer: _____ 73. The most commonly used standard data code to represent alphabetical, numerical and punctuation characters used in electronic data processing system is called a. ASCII b. EBCDIC c. BCD d. All of above Answer: _____ 74. Where does a computer add and compare data? a. b. c. d. Hard disk Floppy disk CPU chip Memory chip Answer: _____ 75. A complete microcomputer system consists of a. b. c. d. microprocessor memory peripheral equipment all of above Answer: _____ 76. Pipelining strategy is called implement a. b. c. d. instruction instruction instruction instruction execution prefetch decoding manipulation Answer: _____ 77. A stack is a. an 8-bit b. a 16-bit c. a set of information d. a 16-bit register in the microprocessor register in the microprocessor memory locations in R/W memory reserved for storing temporarily during the execution of computer memory address stored in the program counter Answer: _____ 78. A stack pointer is a. a 16-bit register in the microprocessor that indicate the beginning of the stack memory. b. a register that decodes and executes 16-bit arithmetic expression. c. The first memory location where a subroutine address is stored. d. a register in which flag bits are stored Answer: _____ 79. Interrupts which are initiated by an instruction are a. b. c. d. internal external hardware software Answer: _____ 80. A time sharing system imply a. b. c. d. more more more None than one processor in the system than one program in memory than one memory in the system of above Answer: _____ 81. Processors of all computers, whether micro, mini or mainframe must have a. b. c. d. ALU Primary Storage Control unit All of above Answer: _____ 82. What is the control unit's function in the CPU? a. b. c. d. To to to to perform arithmetic operations store program instruction perform logic operations decode program instructions Answer: _____ 83. What is meant by a dedicated computer? a. which is used by one person only b. which is assigned to one and only one task c. which does one kind of software d. which is meant for application software only Answer: _____ 84. When a subroutine is called, the address of the instruction following the CALL instructions stored in the a. b. c. d. stack pointer accumulator program counter stack Answer: _____ 85. A collection of 8 bits is called a. b. c. d. byte word record nibble Answer: _____ 86. How many address lines are needed to address each memory locations in a 2048 x 4 memory chip? a. b. c. d. 10 11 8 12 Answer: _____ 87. A computer program that converts an entire program into machine language at one time is called a/an a. b. c. d. interpreter simulator compiler commander Answer: _____ 88. In immediate addressing the operand is placed a. in the CPU register b. after OP code in the instruction c. in memory d. in stack Answer: _____ 89. The ALU and control unit of most of the microcomputers are combined and manufacture on a single silicon chip. What is it called? a. b. c. d. monochip microprocessor ALU control unit Answer: _____ 90. When the RET instruction at the end of subroutine is executed, a. the information where the stack is iniatialized is transferred to the stack pointer b. the memory address of the RET instruction is transferred to the program counter c. two data bytes stored in the top two locations of the stack are transferred to the program counter d. two data bytes stored in the top two locations of the stack are transferred to the stack pointer Answer: _____ 91. Interrupts which are initiated by an I/O device are a. b. c. d. internal external software all of above Answer: _____ 92. A collection of lines that connects several devices is called .............. a. b. c. d. bus peripheral connection wires Both a and b internal wires Answer: _____ 93. The access time of memory is ............... the time required for performing any single CPU operation. a. b. c. d. Longer than Shorter than Negligible than Same as Answer: _____ 94. When the CPU detects an interrupt, it then saves its ................... a. b. c. d. Previous state Next state Current state Both A and B Answer: _____ 95. The unit which decodes and translates each instruction and generates the necessary enable signals for ALU and other units is called .. a. b. c. d. arithmetic unit logical unit control unit CPU Answer: _____ 96. Pipelining increases the CPU instruction .......... a. b. c. d. efficiency latency throughput Both a and c Answer: _____ 97. .................. is concerned with the way the hardware components operate to form computer system. a. Computer organization b. Computer design c. Computer architecture d. Computer implementation Answer: _____ 98. Which statement is valid about computer program? a. b. c. d. It is understood by a computer It is understood by programmer It is understood to use All of the above Answer: _____ 99. CISC stands for ................ a. b. c. d. Common Instruction Set Computers Complex Instruction Set Compilers Complex Instruction Set Computers Compound Instruction Set Computers Answer: _____ 100. The communication between central system and the outside environment is done by a. b. c. d. Input-output subsystem Control system Memory system Logic system Answer: _____ 101. The register that keeps track of the instructions in the program stored in memory is .. a. Control register b. Program counter c. Status register d. Direct register Answer: _____ 102. Data transfer between the main memory and the takes place through two registers namely ....... a. b. c. d. general purpose register and MDR accumulator and program counter MAR and MDR MAR and Accumulator Answer: _____ CPU register 103. The advantage of serial data communication are : a. b. c. d. Requires less number of lines between transmission& receiver. Cheaper Larger speed of transmission Both (a) & (b) Answer: _____ 104. Memory mapped I/O scheme is used for the allocation of address to memories and I/O devices is used for a. b. c. d. Small systems Large systems Both large and small systems None Answer: _____ 105. From a source code, a compiler can detect a. b. c. d. run-time error Logical errors Syntax error None Answer: _____ 106. If the Memory chip size is 256*1 bits, then the number of chips required to make up 1k bytes of Memory is a. b. c. d. 32 24 12 8 Answer: _____ 107. How many address bits are required for 512*4 memory a. b. c. d. 512 4 9 0 Answer: _____ 108. Cache memory a. b. c. d. Increase performance Reduce performance Machine cycle increases None of them Answer: _____ 109. Associative memory is a a. b. c. d. Very cheap memory Pointer addressable memory Content address memory Slow memory Answer: _____ 110. How many address bits are required for a 1024*8 memory a. b. c. d. 1024 5 10 None Answer: _____ 111. A major advantage of direct mapping of a cache is its simplicity. The main disadvantage of this organization that a. It does not allow simultaneous access to the intended data and its tag b. It is more expensive than other types of cache organizations c. The cache hit ratio is degraded if two or more blocks used alternatively map onto the same block frame in the cache. d. None of them. Answer: _____ 112. The purpose of ROM in a computer system is a. b. c. d. To To To To store constant data required for computers own use help reading from memory store application program store 0’s in memory. Answer: _____ 113. Data from memory location after fetching is deposited by memory in a. b. c. d. MAR MDR IR Status Register Answer: _____ 114. Virtual memory system allows the employment of a. b. c. d. More than address space The full address space More than hard disk capacity None of these. Answer: _____ 115. With 2’s complement represent, the range of values that can be represented on the data bus of an 8 bit micro- processor is given by a. b. c. d. -128 to +127 128 to + 128 -127 to + 128 None Answer: _____ 116. When signed numbers are used in binary arithmetic, then which one of the following notations would have unique representation for zero a. b. c. d. Sign magnitude 1’s complement 2’s complement None Answer: _____ 117. What is the 2’s complement representation of -24 in a 16 bit bit micro-computer a. b. c. d. 0000 0000 0001 1000 1111 1111 1110 0111 1111 1111 1110 1000 None Answer: _____ 118. Instruction cycle is a. b. c. d. Fetch-decode-execution Decode-Fetch-execution Fetch-execution-decode None Answer: _____ 119. Micro instructions are kept in a. Main memory b. Control memory c. Cache memory Answer: _____ 120. The time interval between adjacent bits is called the a. b. c. d. word-time bit-time adjacent time slice time Answer: _____ 121. MIMD stands for a. b. c. d. Multiple instruction multiple data Multiple instruction memory data Memory instruction multiple data Multiple information memory data Answer: _____ 122. The average time required to reach a storage location in memory and obtain its contents is called a. b. c. d. Latency time. Access time. Turnaround time. Response time. Answer: _____ 123. Memory unit accessed by content is called a. b. c. d. Read only memory Programmable Memory Virtual Memory Associative Memory Answer: _____ 124. Cache memory acts between a. b. c. d. CPU and RAM and CPU and None of RAM ROM Hard Disk these Answer: _____ 125. Von Neumann architecture is a. b. c. d. SISD SIMD MIMD MISD Answer: _____ 126. In a vectored interrupt. a. the branch address is assigned to a fixed location in memory. b. the interrupting source supplies the branch information to the processor through an interrupt vector. c. the branch address is obtained from a register in the processor d. none of the above Answer: _____ 127. What characteristic of RAM memory makes it not suitable for permanent storage? a. b. c. d. too slow unreliable it is volatile too bulky Answer: _____