ES210, Digital Design Lab

Reporter Name:

Date:

Partner Names

Group No.:

Lab 11 Synchronous Binary Counter

A. Objectives

Examine the Synchronous Binary Counter and its operation using flip-flops (FFs)

Learn how the Synchronous Binary Counter can perform other operations.

Write and test the Verilog programs that can display the clocks and the four outputs of a 4-bit counter.

B. Introduction

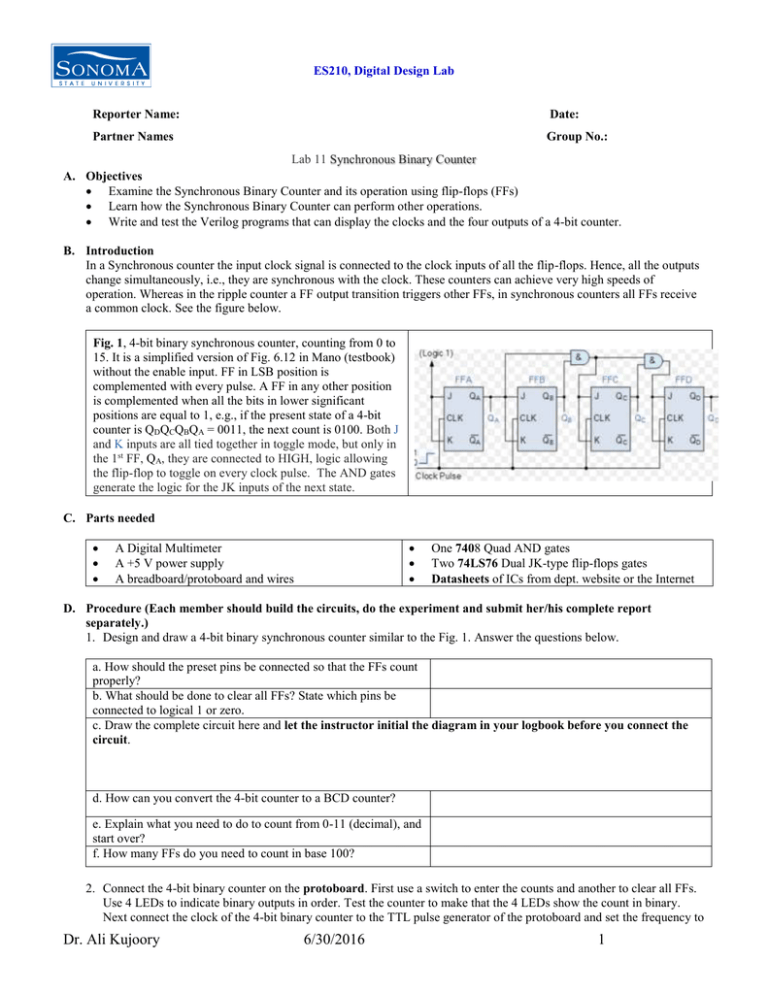

In a Synchronous counter the input clock signal is connected to the clock inputs of all the flip-flops. Hence, all the outputs

change simultaneously, i.e., they are synchronous with the clock. These counters can achieve very high speeds of

operation. Whereas in the ripple counter a FF output transition triggers other FFs, in synchronous counters all FFs receive

a common clock. See the figure below.

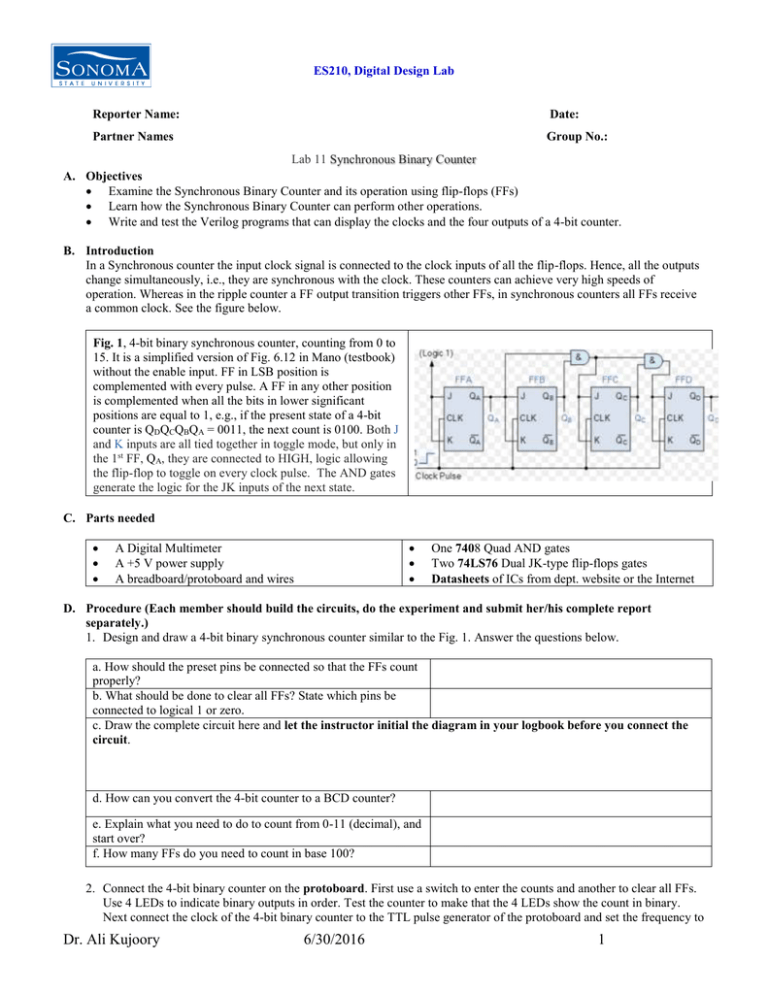

Fig. 1, 4-bit binary synchronous counter, counting from 0 to

15. It is a simplified version of Fig. 6.12 in Mano (testbook)

without the enable input. FF in LSB position is

complemented with every pulse. A FF in any other position

is complemented when all the bits in lower significant

positions are equal to 1, e.g., if the present state of a 4-bit

counter is QDQCQBQA = 0011, the next count is 0100. Both J

and K inputs are all tied together in toggle mode, but only in

the 1st FF, QA, they are connected to HIGH, logic allowing

the flip-flop to toggle on every clock pulse. The AND gates

generate the logic for the JK inputs of the next state.

C. Parts needed

A Digital Multimeter

A +5 V power supply

A breadboard/protoboard and wires

One 7408 Quad AND gates

Two 74LS76 Dual JK-type flip-flops gates

Datasheets of ICs from dept. website or the Internet

D. Procedure (Each member should build the circuits, do the experiment and submit her/his complete report

separately.)

1. Design and draw a 4-bit binary synchronous counter similar to the Fig. 1. Answer the questions below.

a. How should the preset pins be connected so that the FFs count

properly?

b. What should be done to clear all FFs? State which pins be

connected to logical 1 or zero.

c. Draw the complete circuit here and let the instructor initial the diagram in your logbook before you connect the

circuit.

d. How can you convert the 4-bit counter to a BCD counter?

e. Explain what you need to do to count from 0-11 (decimal), and

start over?

f. How many FFs do you need to count in base 100?

2. Connect the 4-bit binary counter on the protoboard. First use a switch to enter the counts and another to clear all FFs.

Use 4 LEDs to indicate binary outputs in order. Test the counter to make that the 4 LEDs show the count in binary.

Next connect the clock of the 4-bit binary counter to the TTL pulse generator of the protoboard and set the frequency to

Dr. Ali Kujoory

6/30/2016

1

1 Hz and watch the LEDs. Let the instructor check the correct operational counter of your circuit.

Does the counter show the 4 LEDs in binary properly?

3. To simulate the above circuit above write a Verilog design program for a 4-bit synchronous binary up counter,

called “binary_counter.v”, in the table below. It should have:

HINT: It is strongly advisable that you follow the Verilog instruction at http://www.asic-world.com/verilog/first1.html

a) Three inputs:

clock to count,

reset to provide synchronous reset the counter when reset is active high, and

enable to enable counting when enable is active high,

b) Four outputs:

count_out[0], as LSB (least significant bit)

count_out[1],

count_out[2],

count_out[3], as MSB (most significant bit)

Compile it to ensure it is error-free.

Note the program on the reference above has three modules: (a) Hello World Program, (b) Counter Design, and (c)

Counter Test Bench. You can see actual Verilog program by clicking “here” under each module. You are interested

only in modules (b) and (c). Module (a) starts with a block diagram that shows the inputs and outputs of the counter.

Module (b) with the Test Case is followed by the small blocks for Clock Generator, Reset, and Enable, that point to the

counter and monitor checker. It will be instructive if you run the program on the website first to see how it works and

see the result. Below is a display of the program on the website.

4. Then, write the corresponding Verilog test bench program, called “binary_counter_tb.v” in the table below. It

should calculate the four outputs above. Compile the program to ensure it is error-free.

5. Simulate the program to display the waveforms for the three inputs clock, reset, enable, and the four outputs count_out

[3:0]. To be able to select and display all four outputs you need to tick the + sign in both columns in the simulation

table. Show your programs and displays to the instructor. Each member should present her/his Verilog portion.

// binary_counter.v program module 15%

// binary_counter_tb.v program module 15%

Verilog waveforms 10%

E. Feedback/Comments (your comments will help improving this lab)

Dr. Ali Kujoory

6/30/2016

2

Was the instruction clear enough? Any error?

How difficult was it for you?

Do you have any observations to make?

F. Report

1. Report the answers in the tables above. You do not need to include the unnecessary text such as the objectives,

instructions, and procedures in the report.

2. Each member should submit her/his complete report separately.

G. References

1. “Digital Design”, Mano and Ciletti, Pearson/Prentice Hall.

2. My first program in Verilog, http://www.asic-world.com/verilog/first1.html

Dr. Ali Kujoory

6/30/2016

3