Verilog Sequential Circuit Design

advertisement

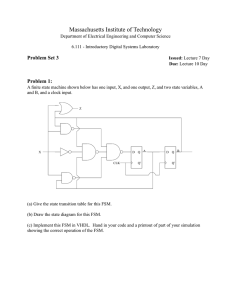

ENEE 408C Lab Capstone Project: Digital System Design Fall 2005 Sequential Circuit Design Finite State Machines A finite state machine (FSM) is a circuit designed to sequence through specific patterns of states in a sequential manner. Each state is represented by a binary value. An FSM contains a sequential state register, and combinational next-state and output logic. Mealy and Moore Machines A Mealy state machine has outputs that are a function of the current state AND the primary inputs. A Moore state machine has outputs that are a function of the current state only. A combined Mealy/Moore state machine has both. Numerous FSM ‘dialects’ exist in design tools. State Table Input A Input Hold Current State Next State Output Y_Me Output Y_Mo 0 1 0 X X X 000 000 001 000 001 000 1 0 0 0 0 1 1 X X 0 X X 1 0 001 010 011 011 010 011 011 000 1 0 0 1 1 0 1 1 1 X 0 X 011 100 100 000 1 0 1 1 State Encoding Sequential (“binary”) – Simple assignment Gray – Assigns states by the minimum logic difference in the state transition graph. – I.e., assign adjacent codes to adjacent states – Reduces the amount of logic needed to decode each state. Johnson – Only one bit changes. One-hot – One bit in the state register for each state. – A large number of flip-flops, but no decoding for states. – Can result in smaller and faster FSMs, especially for ASICs with large amounts of sequential logic relative to combinational logic resources. State Encoding (Example) Number Sequential Gray Johnson One-Hot 0 0000 0000 00000000 0000000000000001 1 0001 0001 00000001 0000000000000010 2 0010 0011 00000011 0000000000000100 3 0011 0010 00000111 0000000000001000 4 0100 0110 00001111 0000000000010000 5 0101 0111 00011111 0000000000100000 6 0110 0101 00111111 0000000001000000 7 0111 0100 01111111 0000000010000000 8 1000 1100 11111111 0000000100000000 9 1001 1101 11111110 0000001000000000 10 1010 1111 11111100 0000010000000000 11 1011 1110 11111000 0000100000000000 12 1100 1010 11110000 0001000000000000 13 1101 1011 11100000 0010000000000000 State Diagram 0X/1 0 XX/0 1 000 1X/0 001 100 1 0X/0 00/1 1X/1 10/1 1 X1/0 011 010 XX/0 0 Circuit Implementation of FSM Combinational part – compute next state and output given inputs and current state Sequential part – use registers to store state codes – update state registers at each clock cycle How to Describing a FSM and its circuit implementation in Verilog HDL? Blocking and Non-blocking assignments “<=“ : (non-blocking assignment): – synchronized to clock (time unit) edge, concurrent = (blocking assignment): – propagates immediately, sequential Example: Blocking assignment “ = “ module swap; reg a, b, temp; always @ (a or b) begin temp = a; a= b; b =temp; end endmodule Example: Non-blocking assignment“<=“ module swap; reg a, b; always @ (a or b) begin a <= b; b <= a; end endmodule intra and inter assignment #3 a <= b; a <= #3 b; General Rules for Blocking and Non-blocking assignments <= (non-blocking assignment): synchronized to clock (time unit) edge, concurrent = (blocking assignment):propagates immediately, sequential # <delay> <assignment statement> (blocking delay) <LHS><assignment OP>#<delay>RHS (non-blocking delay) Any of the four (2 X 2) possible combinations is allowed. Example 1: module assign1; reg a,b,c,d; initial begin a = 0; b = 0; c = 0; d = 0; $monitor($time,,”a = %d, b =%d, c = %d, d = %d”, a,b,c,d); #20 $finish(2); end always begin b = ~d; a = #2 b; //non-blocking delay c = ~c; #3 d <= c; //blocking delay end endmodule Example 2: module assign2; reg a, b, c, d; initial begin a = 0; b = 0; c = 0; d = 0; $monitor($time,,”a=%d, b=%d, c=%d, d=%d”,a,b,c,d); #20 $finish(2); end always begin b = ~b; #2 a = b; //blocking delay c = ~c; d <= #3 c; //non-blocking delay end endmodule Concurrent Execution always @(posedge clock) x = y; always @(x) z = ~z; HDL Coding Style for FSM Typically the synchronous portion is simply the state <= next_state assignment. The next_state portion is done in a purely combinational block (or multiple blocks). – This is best done using a case statement rather than an if/else tree. – Defaults are easily set and excepted by unique cases. FSM Verilog Behavior modeling Combinational part – always@ (inputs or current states) begin case (current state) state1: next state = ....; output = …; state2: … … end Sequential part – cyclic behavior and edge detection – use non-blocking assignment for sequential behavior always@ (posedge clk) begin current state <= next state; end Generate CLOCK signal in Testbench module testbench; reg clk; parameter half_cycle = 50; initial begin clk = 0; … #350 $finish; end always begin #half_cycle clk = ~clk; end endmodule Resets Using an asynchronous reset – Ensures that the state machine is always initialized to a known valid state. – No need to decode any unused current state values and thus minimizes next state logic. Using a synchronous reset or no reset – Cannot predict initial state. – Must decode all states in the next state logic. – Can be a win if the next state logic is small compared to the additional size of the reset HW. Assignment: Design a 4-bit counter with 1-bit input to control increase/decrease, 1 bit to reset to zero, and it should be synchronized. – design the counter using FSM. Draw the state transition table/graph – design the counter using a while loop – design the counter using a for loop – design the counter using only if statement