Jon Brame

advertisement

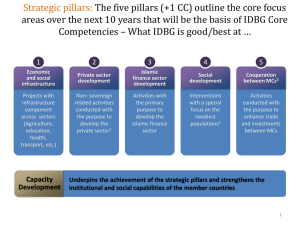

Selectively Grown Silicon Nano-Wires for Transistor Devices Jonathon A. 1 2008 2 1 Brame , Nathan 1 Woods , Dr. Stephanie A. 2 Getty Student Internship Program, Goddard Space Flight Center, Department of Physics, Provo, UT, jon.brame@gmail.com NASA Goddard Space Flight Center, Materials Engineering Branch, Code 541, Greenbelt, MD, Stephanie.A.Getty@nasa.gov Applications Abstract The goal of this project is to fabricate a transistor device using silicon nano-wires (SiNW) as semiconductors. In order to be able to establish electrical conduct with the nano-wires the SiNW growth is confined to certain areas that can be contacted using electron-beam lithography (EBL). This is done by controlling the catalyst deposition through angleevaporation onto pillars on the device. The nanowires then grow from the sidewalls of the pillars and can be contacted using EBL. Background We have been able to successfully fabricate pillar structures on a Silicon/Silicon Dioxide chip and grow Silicon nanowires from the sidewalls of these pillars. This ability to grow SiNWs selectively will allow us to selectively place devices on a substrate as part of a lab-ona-chip ensemble. We are also able to control the amount of gold catalyst by varying the height of the pillars. The amount of catalyst determines the length and width of nanowires. This will allow us to maximize the number of devices as well as control their dimensions. This device was designed to be the transistor in a chemical sensing field effect transistor (chemFET) application. Once the placement of a SiNW transistor device can be controlled, it can be placed in-line with a micro-fluidics framework which could deliver liquid at unknown concentrations across the device. The charge concentration in the fluid will act as a variable gate voltage, and once calibrated will indicate the concentration of chemical in the fluid. In combination with a liquid chromatography device and a mass spectrometer, the chem-FET device will contribute to the “lab on a chip” concept for planetary exploration. Figure (top) A single Silicon nanowire is used as a transistor with source (S), drain (D) and gate (G) electrodes. (bottom) An IV curve for the device at top with several different gate voltages. This work, done by Chung at UCLA, showed the viability of making transistors out of as-grown SiNWs. Silicon Nanowires (SiNW) are grown using a goldcatalyzed LPCVD process. At high temperatures in the growth furnace, the thin-film (~2 nm) gold catalyst beads up, allowing crystalline Silicon to grow in narrow wires under the gold “seeds”. Growth temperature is 450° C and the feedstock gas is Silane (SiH4). The result is a wire with width from 10-40 nm and length anywhere from 100 nanometers to several micrometers. Since these wires are made of Silicon, they exhibit semiconductor properties and can be doped for use in transistor devices (see Chung et al). Results Figure A pillar structure with a SiNW grown from the side wall. The pillar height is 2400Å and the SiNW dimensions are about 1 μm long by 20 nm in diameter. Figure Future potential missions to Mars (above) and Saturn’s moon Titan (at left) are two possible applicationgs where the ChemFET device would be useful. A knowledge of the chemical composition of the planets and moons in our solar system will enhance our ability to expand exploration to places like these and beyond Fabrication Electron beam lithography (EBL) is used to pattern small squares (1μm on a side) on a Si/SiO2 wafer, then a gold layer is deposited using thermal evaporation. These patterned gold squares are used as an etch stop in a reactive ion etch (O2, CF4) to create “pillars” of oxide 2400Å high. Next gold catalyst for nanowire growth is angle-evaporated at an angle of 5° (from parallel) onto the sides of the pillars. This confines the growth to the sides of the pillars. Once nanowires are grown, EBL and a titanium/gold E-beam evaporation are used to pattern contact pads to electrically contact the ends of the wires. Initial testing can be done using the Silicon substrate as a gate for the nanowire transistor. Eventually the gate voltage will be supplied by passing ions in an ionized fluid flowing over the top of the transistor. 1 5 2 6 3 4 7 8 Figure 1. Gold is deposited on top of a Silicon/Silicon Dioxide wafer that has been through a lithography process to expose small squares on the surface. 2. Once the resist is removed, all that remains are squares of gold 1μm x1μm. 3. The wafer is put into a reactive ion etcher where fluorine ions directionally etch away 2400Å of oxide wherever it is not protected by gold. 4. The gold on top of the pillars is removed using a potasium iodide etch. 5. Gold catalyst is angle-evaporated onto the sidewalls of the pillars. 6. Silicon nanowires are grown using an LPCVD at 450°C with Silane as the feedstock gas. 7. Another lithography process exposes the ends of the nanowires, then gold is evaporated over the entire surface. 8. After removing the resist and excess gold, the nanowires are contacted at each end by gold leads and the device is ready for testing. Total Survi ving Pillars Pillars with no wires Pillars with one wire Pillars with two wires Pillars with three wires Pillars with >3 wires Pillars with Usable wires 1200Å 35 15 11 4 3 2 3 2400Å 24 3 11 3 4 3 11 Table 1 Comparison of the number of pillars with usable wires at heights of 1200Å and 2400Å. Usable wires are wires extending more than 500nm from the side wall. Although the wires are slightly thicker, the density of usable devices is much greater at 2400Å. Conclusions and Future Work • Selectively placing nanowires is possible using pillar-grown SiNWs. • The ideal pillar height for maximum wire density is 2400A. • Actual transistor devices are in fabrication and will be tested in the near future. • Once transistors are tested, process will be used to selectively place SiNWs for use in Chem-FET devices. Bibliography •Sung-Wook Chung, Jae-Young Yu, and James R. Heath, “Silicon nanowire devices” Applied Physics Letters, 2000. Yi Cui, “High Performance Silicon Nanowire Field Effect Transistors” Nano Letters, 2003 Acknowledgements Student Internship Program Rocky Mountain Space Grant Consortium BYU- Dr. David Allred C. Taylor, T. Adachi, V. Mikula