Digital Design with VHDL Presented by: Amir Masoud Gharehbaghi Email:

advertisement

Digital Design with VHDL

Presented by: Amir Masoud Gharehbaghi

Email: amgh@mehr.sharif.edu

Design Hierarchy

Design Specification & Requirement

Behavioral Design

Register Transfer Level (RTL) Design

Logic Design

Circuit Design

Physical Design

Manufacturing

Design Automation (DA)

Automatic doing task in design process:

–

–

–

–

–

Transforming one form of design to another

Verifying functionality and timing of design

Generating test sequence for design validation

Documentation

…

Hardware Description Languages

(HDLs)

Describing Hardware for:

–

–

–

–

–

–

Design & Modeling

Simulation

Synthesis

Testing

Documentation

…

VHDL History

Initiated with VHSIC project in 1981 by DoD

– VHSIC: Very High Speed Integrated Circuits

In 1983 DoD established requirements for

VHSIC HDL (VHDL)

In 1987 VHDL became an IEEE standard:

VHDL 1076-1987

In 1993 a new version of VHDL released:

VHDL 1076-1993

VHDL Specifications

Designing in Various Levels of Abstraction: from

Behavioral to Gate Level

Support for Design Hierarchy (Structural Design)

Library Support

Support of Generic Design

Timing Control

Concurrent & Sequential Statements

Type Declaration

..

Components in VHDL

Each Component in VHDL is described as an

ENTITY-ARCHITECTURE pair

ENTITY part describes the interface of

component

ARCHITECTURE part describes the functionality

and timing of component

An ENTITY may have different ARCHITECTURES,

describing the component at various levels and with

different details of timing and functionality

ENTITY Declaration

ENTITY entity_name IS

generic clause

port clause

END ENTITY entity_name ;

ENTITY and3 IS

GENERIC (delay: TIME := 5 ns);

PORT (a, b, c : IN BIT; z : OUT BIT);

END and3;

Ports

Ports are Component Interface Signals

Each Port has:

– Name

– Mode

•

•

•

•

IN

OUT

INOUT

BUFFER

– Type

: Input signals

: Output Signals

: Bidirectional Signals

: Like OUT from outside the component &

INOUT from Inside it

Standard Types

Standard Package Types:

–

–

–

–

–

–

–

–

BIT

BIT_VECTOR

BOOLEAN

INTEGER

REAL

TIME

CHARACTER

STRING

ARCHITECTURE Declaration

ARCHITECTURE arch_name OF entity_name IS

architecture declarative part

BEGIN

concurrent statements

END ARCHITECTURE arch_name ;

ARCHITECTURE single_delay OF and3 IS

BEGIN

z <= a AND b AND c AFTER delay ;

END single_delay ;

Concurrent Statements

Concurrent Signal Assignment

Component Instantiation Statement

Generate Statement

Process Statement

Block Statement

Concurrent Procedure Call Statement

Concurrent Assert Statement

Concurrent Signal Assignment

Conditional Signal Assignment Statement

Selected Signal Assignment Statement

Conditional Signal Assignment

target <= conditional_waveforms;

conditional_waveforms ::=

{ waveform WHEN condition ELSE }

waveform [ WHEN condition]

waveform ::=

waveform_element {, waveform_element}

| UNAFFECTED

waveform_element ::=

value_expression [AFTER time_expression]

| NULL [AFTER time_expression]

Conditional Signal Assignment

Examples

a <= b;

a <= ‘0’ AFTER 10 ns ;

x <= a AND b OR c ;

y <= a AFTER 1 ns WHEN x = y ELSE b ;

z <= a AND b, c AFTER 5 ns, ‘1’ AFTER 30 ns

WHEN NOW < 1 ms ELSE

‘0’, a AFTER 4 ns, c OR d AFTER 10 ns;

2 Input NAND Gate

ENTITY nand2 IS

PORT (a, b: IN BIT; z: OUT BIT);

END nand2;

ARCHITECTURE no_delay OF nand2 IS

BEGIN

z <= a NAND b;

END no_delay;

3 Input NAND Gate

ENTITY nand3 IS

PORT (a, b, c: IN BIT; z: OUT BIT);

END nand3;

ARCHITECTURE no_delay OF nand3 IS

BEGIN

z <= NOT (a AND b AND c);

END no_delay;

2:1 MUX

ENTITY Mux2x1 IS

PORT (a0, a1, sel: IN BIT; z: OUT BIT);

END Mux2x1;

ARCHITECTURE conditional OF Mux2x1 IS

BEGIN

z <= a0 WHEN sel = ‘0’ ELSE a1;

END conditional;

VHDL Operators

Logical AND , NAND , OR , NOR , XOR , XNOR

Relational

= , /= , < , <= , > , >=

Shift

SLL , SRL , SLA , SRA , ROL , ROR

Adding + , - , &

Sign

+,Multiplying

* , / , MOD , REM

Miscellaneous ABS , **

Selected Signal Assignment

WITH expression SELECT

target <= selected_waveforms ;

selected_waveforms ::=

{ waveform WHEN choices, }

waveform WHEN choices

choices ::= choice { | choice }

choice ::= expression | range | simple_name | OTHERS

2:1 MUX

ARCHITECTURE selected OF Mux2x1 IS

BEGIN

WITH sel SELECT

z <= a0 WHEN ‘0’,

a1 WHEN ‘1’;

-- a1 WHEN OTHERS;

END selected;

Component Instantiation Statement

label: instantiated_unit

[ GENERIC MAP (association_list) ]

[ PORT MAP (association_list) ] ;

instantiated_unit ::=

[COMPONENT] component_name

| ENTITY entity_name [ (architecture_name) ]

| CONFIGURATION configuration_name

association_list ::= association_element { , association_element }

association_element ::= [ formal_part => ] actual_part

4:1 MUX (using entity)

ENTITY Mux4x1 IS

PORT (a : IN BIT_VECTOR(3 DOWNTO 0); sel: IN BIT_VECTOR(0 TO 1) ;

z: OUT BIT);

END Mux4x1;

ARCHITECTURE mux2x1_based OF Mux4x1 IS

SIGNAL im0, im1 : BIT;

BEGIN

m1: ENTITY WORK.Mux2x1(conditional) PORT MAP (a(0), a(1), sel(0), im0);

m2: ENTITY WORK.Mux2x1(conditional) PORT MAP (a(2), a(3), sel(0), im1);

m3: ENTITY WORK.Mux2x1(selected) PORT MAP (im0, im1, sel(1), z);

END mux2x1_based;

4:1 MUX (using component)

ARCHITECTURE comp_based OF Mux4x1 IS

SIGNAL im0, im1 : BIT;

COMPONENT mux2 PORT (a0, a1, sel: IN BIT; z: OUT BIT);

END COMPONENT;

FOR ALL: mux2 USE ENTITY WORK.Mux2x1(conditional);

BEGIN

m1: mux2 PORT MAP (a(0), a(1), sel(0), im0);

m2: mux2 PORT MAP (a(2), a(3), sel(0), im1);

m3: mux2 PORT MAP (a0 =>im0, a1 =>im1, sel =>sel(1), z => z);

END comp_based;

4:1 MUX (another binding)

ARCHITECTURE another OF Mux4x1 IS

SIGNAL im0, im1 : BIT;

COMPONENT mux2 PORT (a0, a1, sel: IN BIT; z: OUT BIT);

END COMPONENT;

FOR m1, m2: mux2 USE ENTITY WORK.Mux2x1(conditional);

FOR OTHERS: mux2 USE ENTITY WORK.Mux2x1(selected);

BEGIN

m1: mux2 PORT MAP (a(0), a(1), sel(0), im0);

m2: mux2 PORT MAP (a(2), a(3), sel(0), im1);

m3: mux2 PORT MAP (a0 =>im0, a1 =>im1, sel =>sel(1), z => z);

END another;

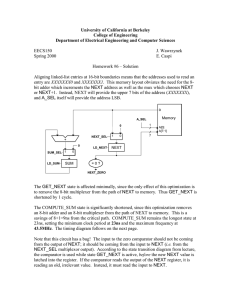

Testing the Mux4x1

ENTITY test_mux4x1 IS END test_mux4x1;

ARCHITECTURE test1 OF test_mux4x1 IS

SIGNAL inp: BIT_VECTOR(3 DOWNTO 0);

SIGNAL sel: BIT_VECTOR(1 DOWNTO 0);

SIGNAL outp: BIT;

BEGIN

comp: ENTITY Mux4x1(another) PORT MAP (inp, sel, outp);

inp <= "0101", "1101" AFTER 50 ns, "1110" AFTER 100 ns,

"0011" AFTER 200 ns;

sel <= "00", "01" AFTER 20 ns, "11" AFTER 60 ns, "10" AFTER

90 ns, "00" AFTER 180 ns;

END test1;