Embedded System (ETEC-404) for ECE & IT - Question Bank by MANORANJAN KUMAR

advertisement

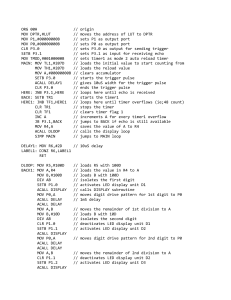

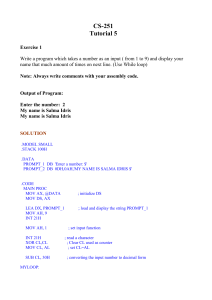

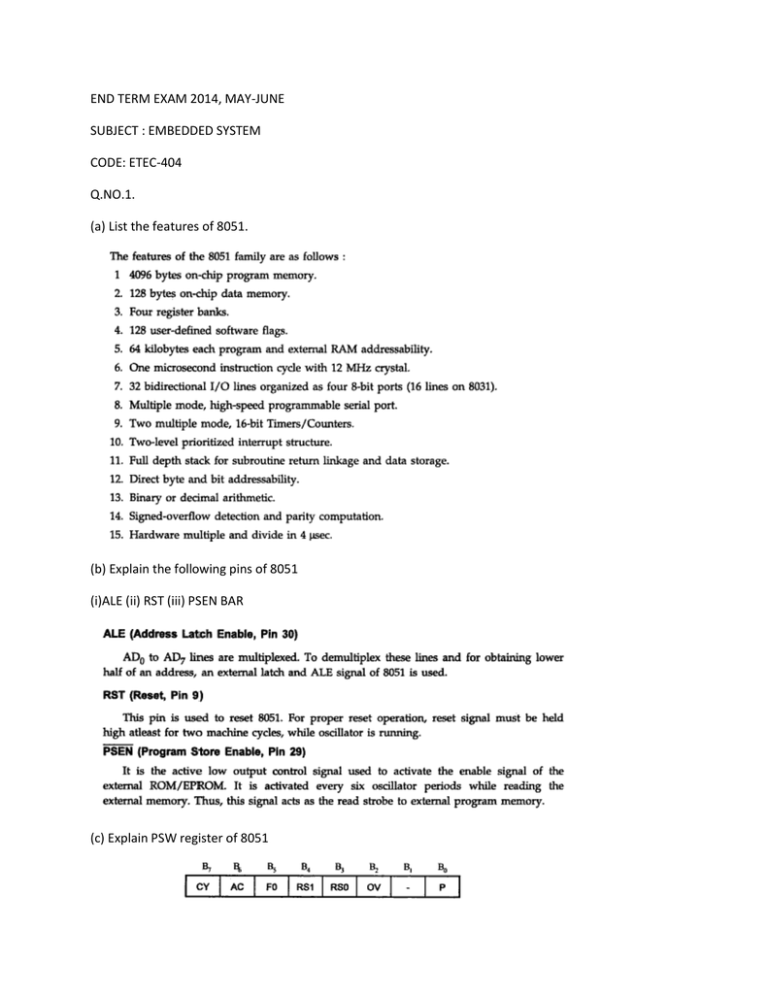

END TERM EXAM 2014, MAY-JUNE SUBJECT : EMBEDDED SYSTEM CODE: ETEC-404 Q.NO.1. (a) List the features of 8051. (b) Explain the following pins of 8051 (i)ALE (ii) RST (iii) PSEN BAR (c) Explain PSW register of 8051 (d) Write a program to find the maximum number from a given 8-bit ten numbers. (e) How can be enabled or disabled an interrupt of 8051. (f) Explain features of 8255. (g) Explain modes of 8255. (h) Q.NO.2 Q.NO.3 Q.NO.4 Q.NO.5 Q.NO.6 Q.NO.7 Q.NO.8 Q.NO.9 Q.NO.10 Write assembly language program to sending command code . Ans.: Simple LCD interfacing program with 8051 microcontroller so we have three control pins to take care of. so lets program using these 3 control pins. ; P2.0 EQU RS ; P2.1 EQU RW ; P2.2 EQU E ORG 0000H ; MOV A, #38H ; INITIATE LCD ACALL COMMWRT ; ACALL DELAY ; MOV A, #0EH ACALL COMMWRT ACALL DELAY ; DISPLAY ON CURSOR ON ; ; MOV A, #01H ACALL COMMWRT ACALL DELAY ; CLEAR LCD ; ; MOV A, #84H ACALL COMMWRT ACALL DELAY ; CURSOR AT LINE 1 POSITION 4 ; ; MOV A, #'A' ACALL DATAWRT ACALL DELAY ; SEND ASCII DATA ; ; AGAIN : SJMP AGAIN ; COMMWRT: MOV P1, A ; CLR P2.0 ; RS = 0 FOR COMMAND REGISTER CLR P2.1 ; R/W = 0 FOR WRITE SETB P2.2 ; E = 1 FOR HIGH PULSE ACALL DELAY ; CLR P2.2 ; E = 0 FOR LOW PULSE RET DATAWRT: MOV P1, A ; SETB P2.0 ; RS = 1 FOR DATA REGISTER CLR P2.1 ; R/W = 0 FOR WRITE SETB P2.2 ; E = 1 FOR HIGH PULSE ACALL DELAY ; CLR P2.2 ; E = 0 FOR LOW PULSE RET DELAY : MOV R3, #50H ; BACK: MOV R4, #255H ; HERE: DJNZ R4, HERE ; DJNZ R3, BACK ; RET END Q.NO.11 A switch is connected to pin p2.7. write a assembly languge program to monitor the status of the SW and perform the following a) If SW=0 the stepper motor moves clockwise. b) If SW=1 the stepper motor moves counterclockwise. Ans.: ORG OH ; starting address MAIN: SETB P2.7 ; make an input MOV A, #66H ; starting phase value MOV P1, A ; send value to port TURN: JNB P2.7, CW ; check switch result RR A ; rotate right ACALL DELAY ; call delay MOV P1, A ; write value to port SJMP TURN ; repeat CW: RL A ; rotate left ACALL DELAY ; call delay MOV P1, A ; write value to port SJMP TURN ; repeat DELAY: MOV R2, #100 H1: MOV R3, #255 H2: DJNZ R3, H2 DJNZ R2, H1 RET END Q.NO.12 Explain Scheduling policies? state to the running state. of the key metrics in evaluating a scheduling policy. -monotonic scheduling (RMS), introduced by Liu and Layland [Liu73], was one of the first scheduling policies developed for real-time systems and is still very widely used. RMS is known as rate-monotonic analysis(RMA). -known scheduling policy. It is a dynamic priority scheme-it changes process priorities during execution based on initiation times. -EDF can extract higher utilization out of the CPU, but it may be difficult to diagnose the possibility of an imminent overload. -Our analyses of RMS and EDF have made some strong assumptions. -In addition of SCHED_FIFO,POSIX supports two other real-time scheduling policies:SCHED_RR and SCHED_OTHER. -real-time processes to intermix with realtime processes. Q.NO.13 Explain Inter process Communication Mechanism? -Unix supports another, very simple communication mechanism-the signal. -A UML signal is actually a generalization of the Unix signal. While a Unix signal carries no parameters other than a condition code,a UML signal is an object. -Conceptually, semaphores are the mechanism we use to make shared memory safe. IX supports semaphores, but it also supports a direct shared memory mechanism. counting semaphore allows than one process access to a resource at a time. -Based Communication:-The shell syntax of the pipe is very familiar to Unix users. An example appears below.